Recommended

PPT

PDF

PDF

PDF

PPTX

PPTX

PPT

PDF

PDF

PPTX

研究者のための Python による FPGA 入門

PDF

PPTX

PDF

PDF

Synthesijer.Scala (PROSYM 2015)

PDF

FPGAで作るOpenFlow Switch (FPGAエクストリーム・コンピューティング 第6回) FPGAX#6

PDF

PDF

Tensor flow usergroup 2016 (公開版)

PDF

PDF

Pynqでカメラ画像をリアルタイムfastx コーナー検出

PDF

PDF

ACRi_webinar_20220118_miyo

PPTX

Abstracts of FPGA2017 papers (Temporary Version)

PDF

電波望遠鏡用の分光器をAltera SDK for OpenCL使ってサクッと作ってみた

PDF

PDF

深層学習フレームワークChainerの紹介とFPGAへの期待

PDF

VIOPS WORKSHOP 10 クラウドの次に起こるコト

PPTX

Maker Faire 2016 - Microbit & Nano Satellite

PDF

第3回ローレイヤー勉強会 : FPGAでコンピュータを作ってみた

PPTX

PDF

社会の意見のダイナミクスを物理モデルとして考えてみる

More Related Content

PPT

PDF

PDF

PDF

PPTX

PPTX

PPT

PDF

What's hot

PDF

PPTX

研究者のための Python による FPGA 入門

PDF

PPTX

PDF

PDF

Synthesijer.Scala (PROSYM 2015)

PDF

FPGAで作るOpenFlow Switch (FPGAエクストリーム・コンピューティング 第6回) FPGAX#6

PDF

PDF

Tensor flow usergroup 2016 (公開版)

PDF

PDF

Pynqでカメラ画像をリアルタイムfastx コーナー検出

PDF

PDF

ACRi_webinar_20220118_miyo

PPTX

Abstracts of FPGA2017 papers (Temporary Version)

PDF

電波望遠鏡用の分光器をAltera SDK for OpenCL使ってサクッと作ってみた

PDF

Viewers also liked

PDF

深層学習フレームワークChainerの紹介とFPGAへの期待

PDF

VIOPS WORKSHOP 10 クラウドの次に起こるコト

PPTX

Maker Faire 2016 - Microbit & Nano Satellite

PDF

第3回ローレイヤー勉強会 : FPGAでコンピュータを作ってみた

PPTX

PDF

社会の意見のダイナミクスを物理モデルとして考えてみる

PDF

PDF

私のファミコンのfpsは530000です。もちろんフルパワーで(以下略

PDF

[Azure Council Experts (ACE) 第20回定例会] Microsoft Azureアップデート情報 (2016/10/14-201...

PDF

FPGAによる津波シミュレーション -- GPUを超える高性能計算の手法

PDF

PDF

PPTX

PDF

PDF

2値化CNN on FPGAでGPUとガチンコバトル(公開版)

Similar to Myoshimi extreme

PDF

PDF

多数の小容量FPGAを用いた スケーラブルなステンシル計算機の開発

PDF

PDF

FPGAを用いた世界最速のソーティングハードウェアの実現に向けた試み

PDF

PDF

PDF

GPU-FPGA 協調計算を記述するためのプログラミング環境に関する研究(HPC169 No.10)

PPTX

PDF

PDF

PDF

2値ディープニューラルネットワークと組込み機器への応用: 開発中のツール紹介

PPTX

PDF

FPGAベースのソーティングアクセラレータの設計と実装

PDF

Fully-Functional FPGA Prototype with Fine-Grain Programmable Body Biasing (FP...

PDF

PPTX

GPU-FPGA協調プログラミングを実現するコンパイラの開発

PPTX

Androidとfpgaを高速fifo通信させちゃう

PDF

機械学習とこれを支える並列計算 : 並列計算の現状と産業応用について

PPTX

PDF

IEICE technical report (RECONF), January 2015.

Myoshimi extreme 1. 2. 3. 生化学モデルとシミュレーション

解析モデル(ODE)

手法

確率モデル(SSA)

確率的な振る舞いを含めたモデル化

モンテカルロ・シミュレーション

パラメータサーベイ的な性質

分子濃度を連続的な変量としてモデル

化

モデルの構築,検証に膨大な

シミュレーションを要する

→高いスレッドレベル並列性

パイプライン実行+並列モジュール

3

4. FPGAを用いた化学反応シミュレー

タ

ReCSiP (Reconfigurable Cell Simulation Platform) [2003-]

細胞内で生じる化学反応をシミュレーションする専用計算機

長崎大学,JST-ERATO,Caltechとの共同研究(NIH)

並列アクセス可能なSRAMと差動シリアル通信を実装

FPGA: Field-Programmable Gate Array

幸せな時代:1万~10万程度のLUTで任意の論理回路を構成するLSI

十分な数のFP演算が構成できるようになっていた

NoC型(16スレッド) SSA-FPGAの構造

FP- ヒープ+NoC (2007)

Multiplier D D

FPGA PRNG

A

B

FP- C D D C

Logarithm

E

入力 出力

ReCSiP-3 board (2006) LUT: LookUpTable 0000 1

Xilinx Virtex-4 XC4VLX100- 出力をカスタム可能 0001 0

C F C

11FF1136 ….. 4..

1111 1

5. CUBE: 512 FPGA Cluster

英国インペリアル・カレッジで海外研究(2009年2月~3月)

FPGAが8x8実装されたボードを8枚重ねて運用• Verilog-HDLを用いたFP演算の実装

– IEEE754準拠の四則演算+対数

64ビット単方向信号で接続 • 乱数生成モジュール

– LSFR,Merssenne-Twisterなど

ストリームアプリケーション向け計算システム • BlockRAMを利用したヒープ

文字列編集距離で性能をCell/B.E.,GPUと比較• NoC用ルータモジュール

このころ,CPUのマルチコア化と,GPUが人気になり,

「特定のアプリでも」何百倍も高速化する夢のデバイスと 5

してのFPGAはその歴史的役割を終えつつあった...(‘A`)

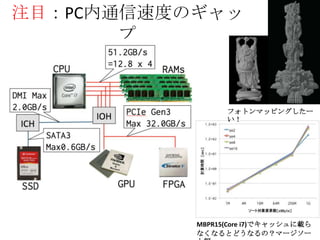

6. 注目:PC内通信速度のギャッ

プ

フォトンマッピングしたー

い!

MBPR15(Core i7)でキャッシュに載ら

なくなるとどうなるの?マージソー

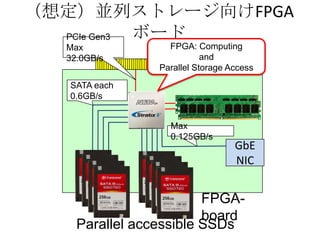

7. (想定)並列ストレージ向けFPGA

PCIe Gen3 ボード

Max FPGA: Computing

32.0GB/s and

Parallel Storage Access

SATA each

0.6GB/s

Max

0.125GB/s

GbE

NIC

FPGA-

board

Parallel accessible SSDs

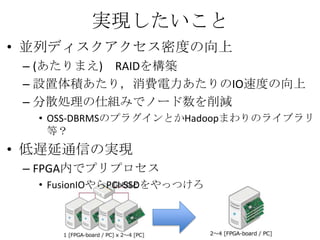

8. 実現したいこと

• 並列ディスクアクセス密度の向上

– (あたりまえ) RAIDを構築

– 設置体積あたり,消費電力あたりのIO速度の向上

– 分散処理の仕組みでノード数を削減

• OSS-DBRMSのプラグインとかHadoopまわりのライブラリ

等?

• 低遅延通信の実現

– FPGA内でプリプロセス

• FusionIOやらPCI-SSDをやっつけろ

9.

![FPGAを用いた化学反応シミュレー

タ

ReCSiP (Reconfigurable Cell Simulation Platform) [2003-]

細胞内で生じる化学反応をシミュレーションする専用計算機

長崎大学,JST-ERATO,Caltechとの共同研究(NIH)

並列アクセス可能なSRAMと差動シリアル通信を実装

FPGA: Field-Programmable Gate Array

幸せな時代:1万~10万程度のLUTで任意の論理回路を構成するLSI

十分な数のFP演算が構成できるようになっていた

NoC型(16スレッド) SSA-FPGAの構造

FP- ヒープ+NoC (2007)

Multiplier D D

FPGA PRNG

A

B

FP- C D D C

Logarithm

E

入力 出力

ReCSiP-3 board (2006) LUT: LookUpTable 0000 1

Xilinx Virtex-4 XC4VLX100- 出力をカスタム可能 0001 0

C F C

11FF1136 ….. 4..

1111 1](https://image.slidesharecdn.com/myoshimi-extreme-130218005519-phpapp02/85/Myoshimi-extreme-4-320.jpg)