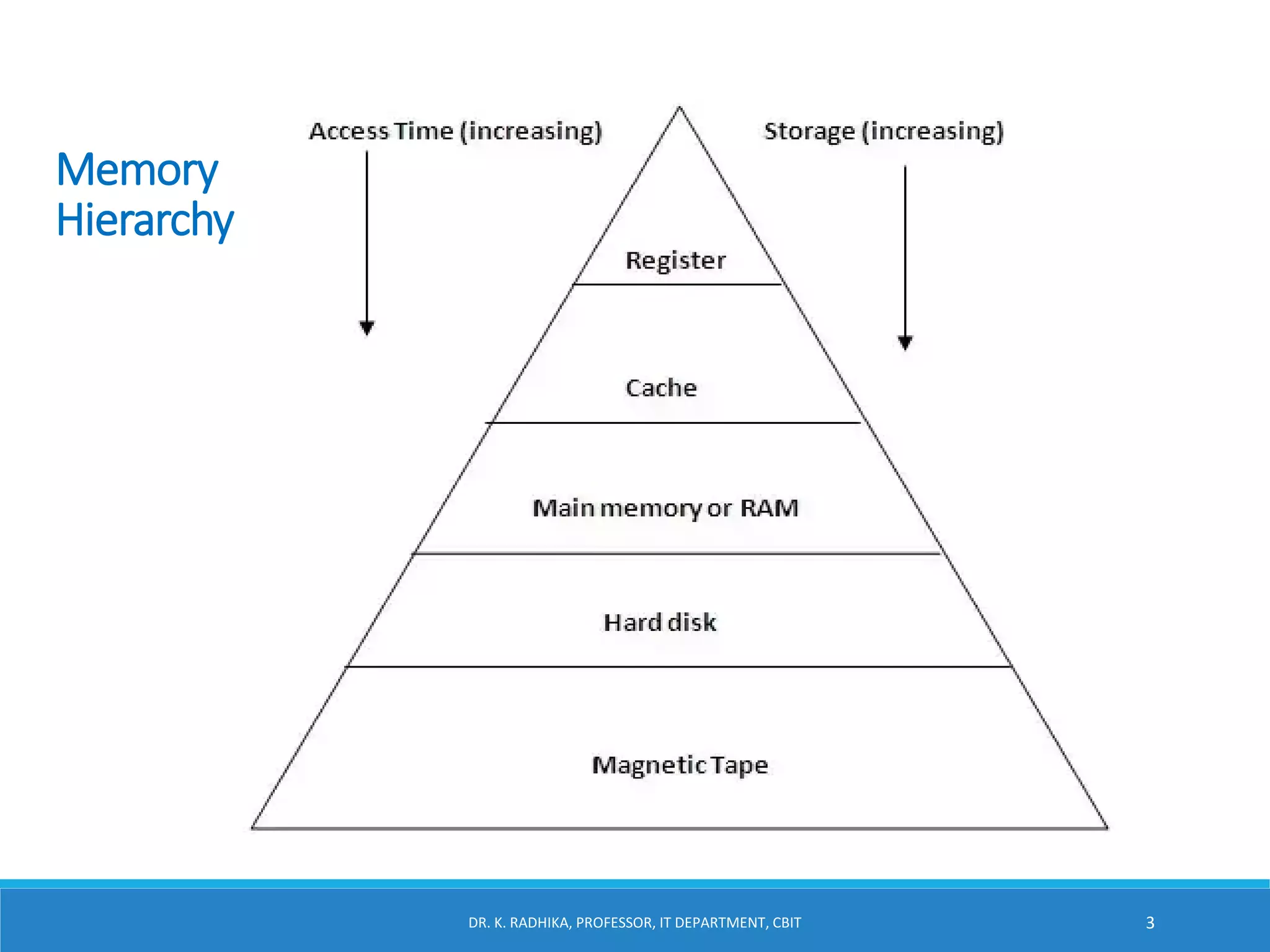

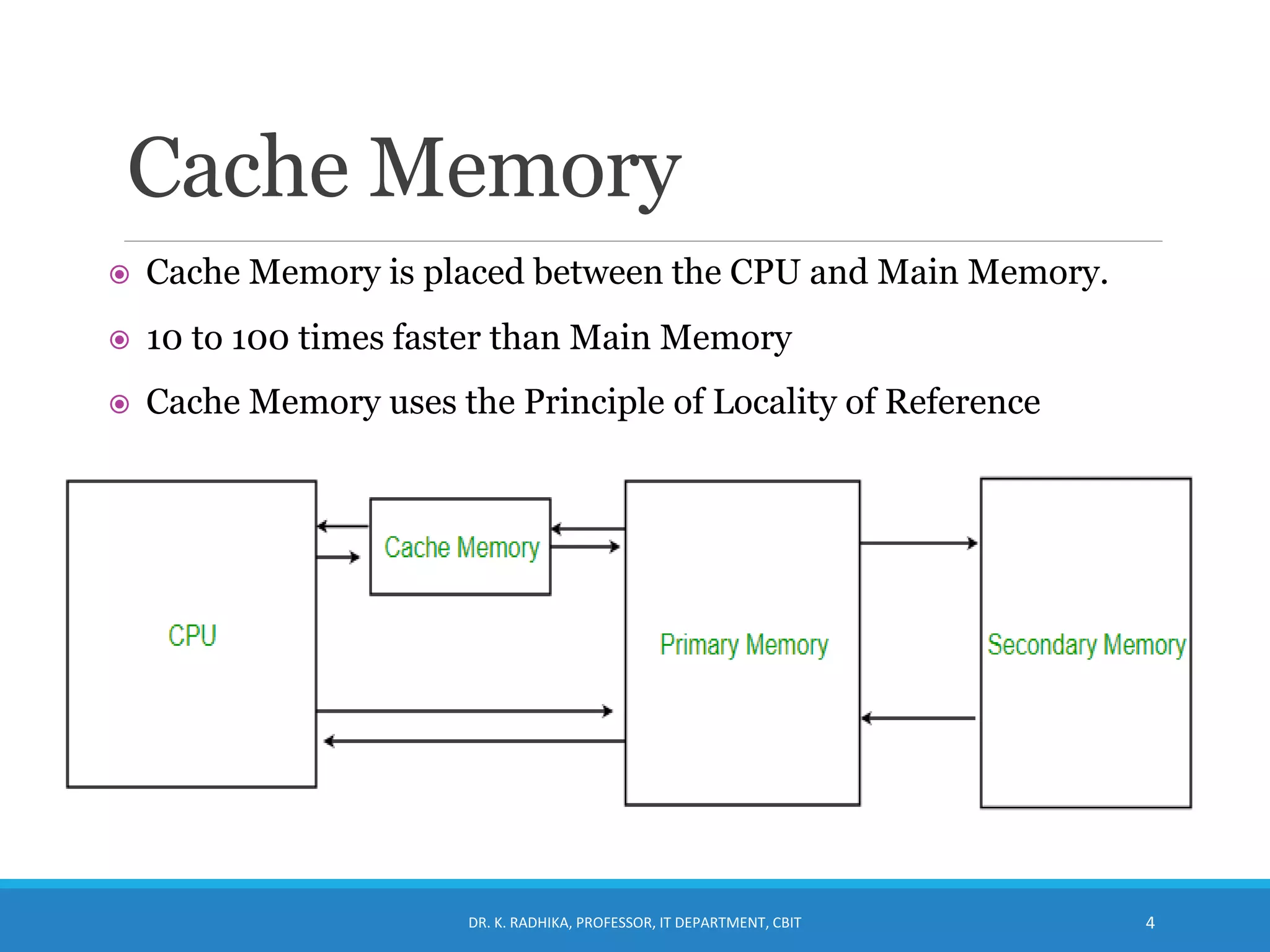

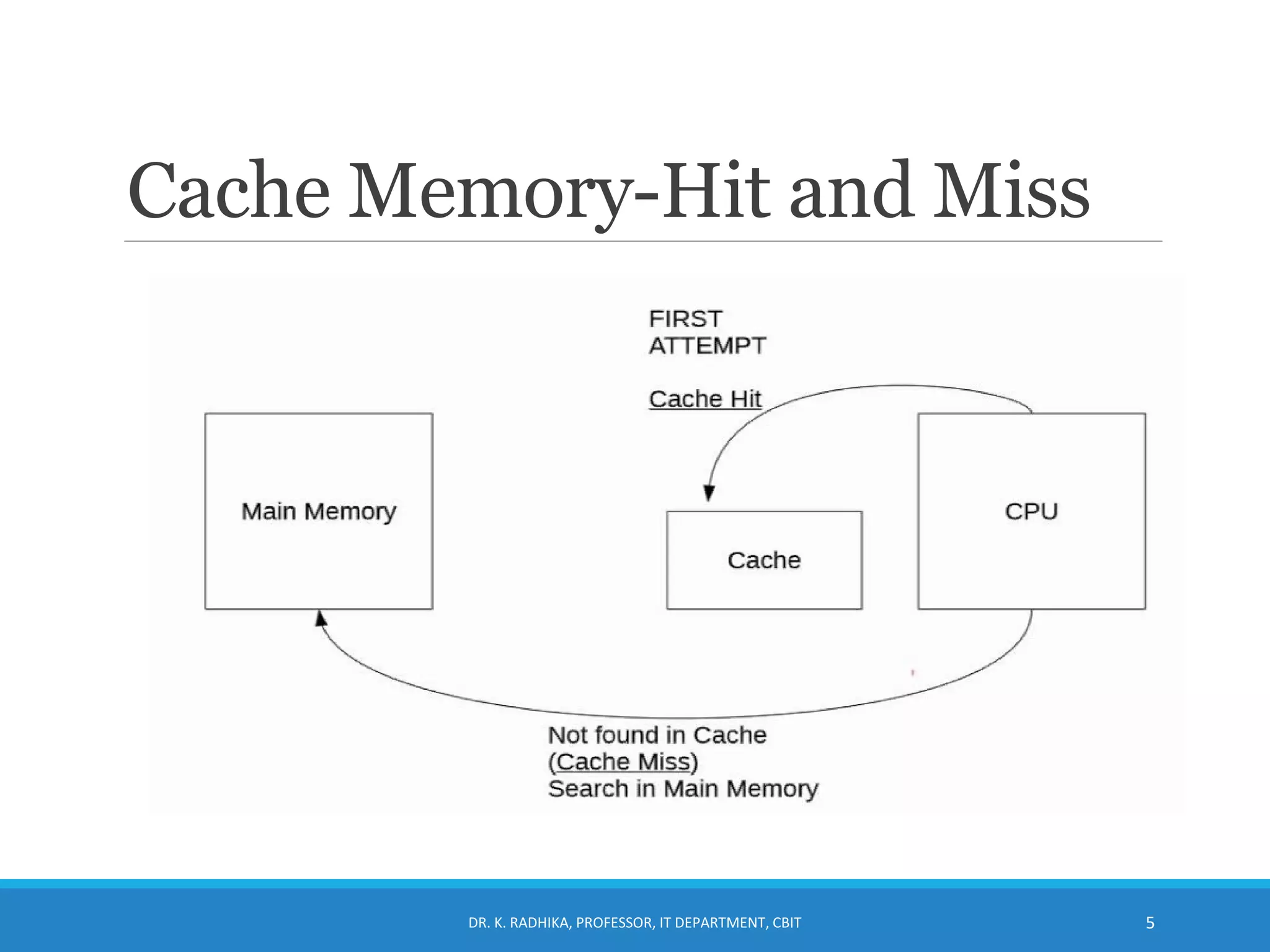

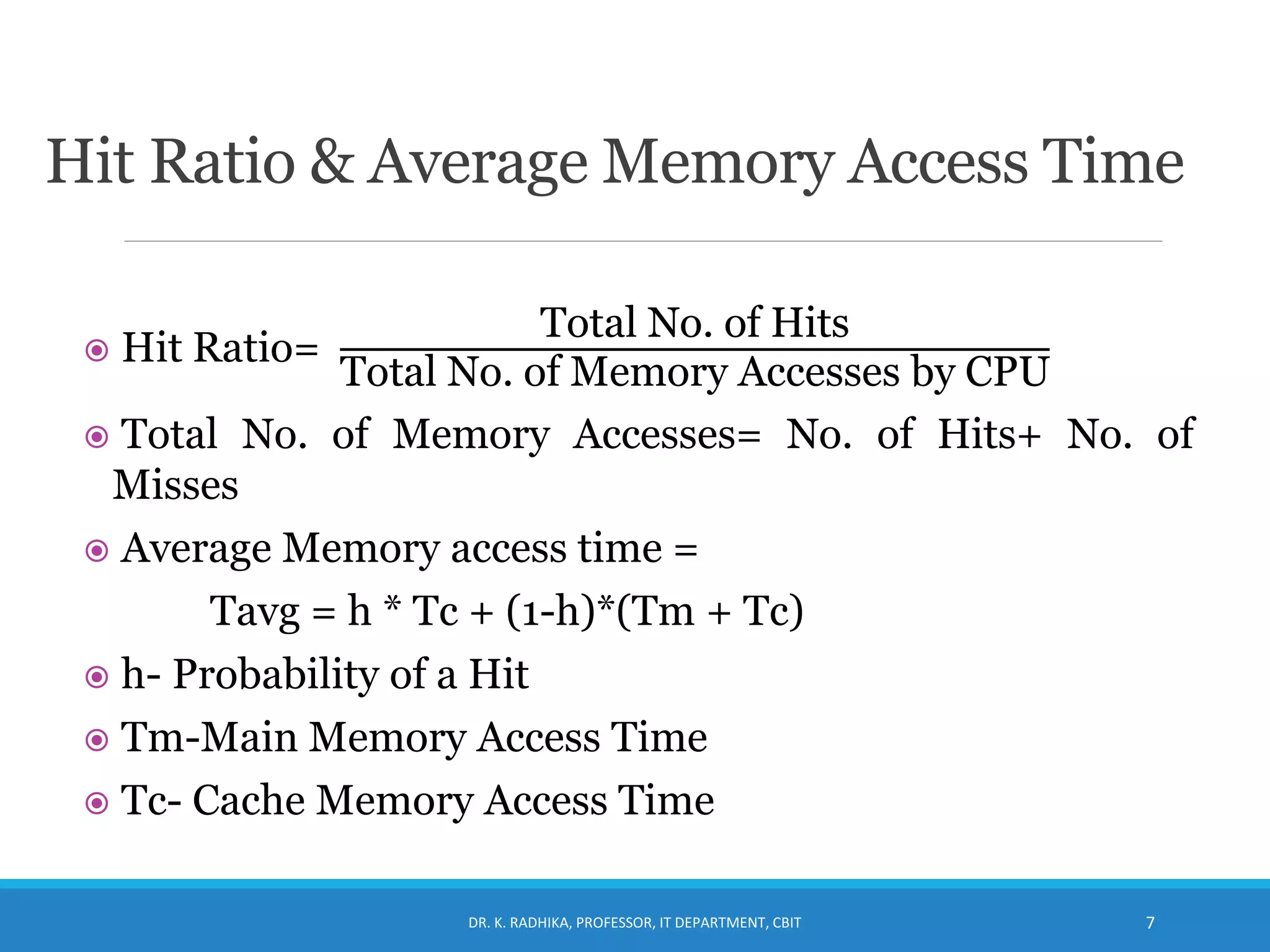

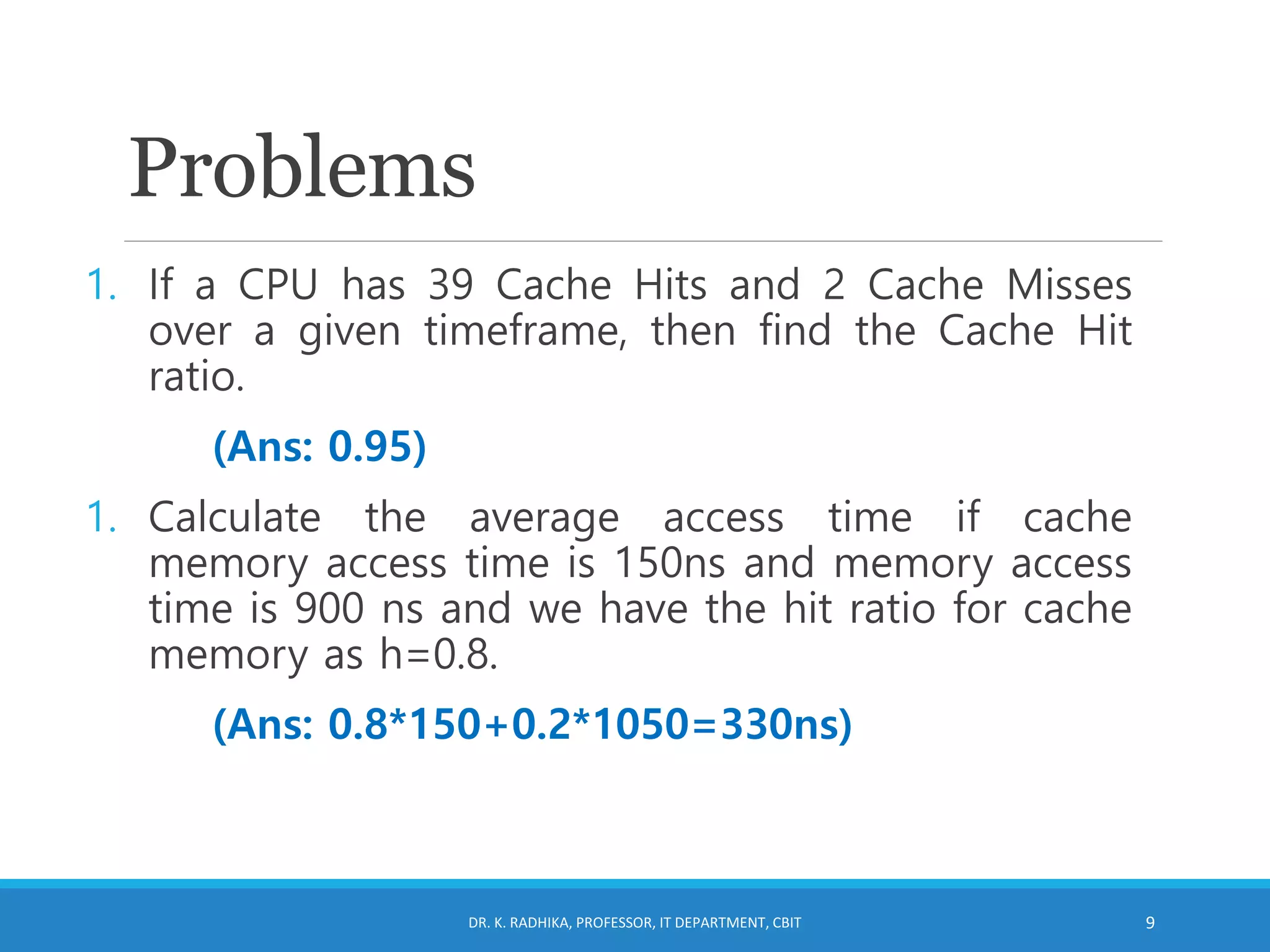

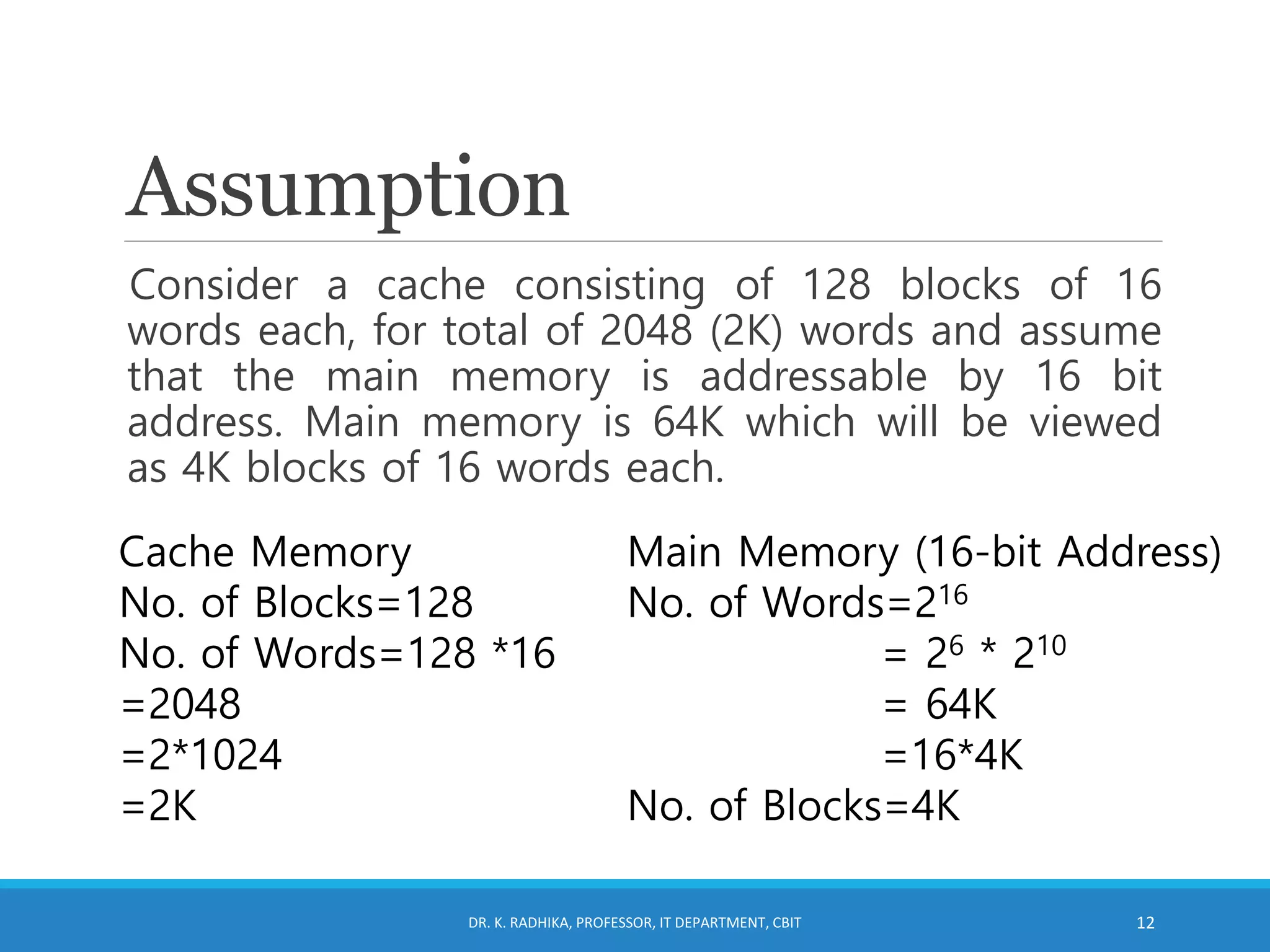

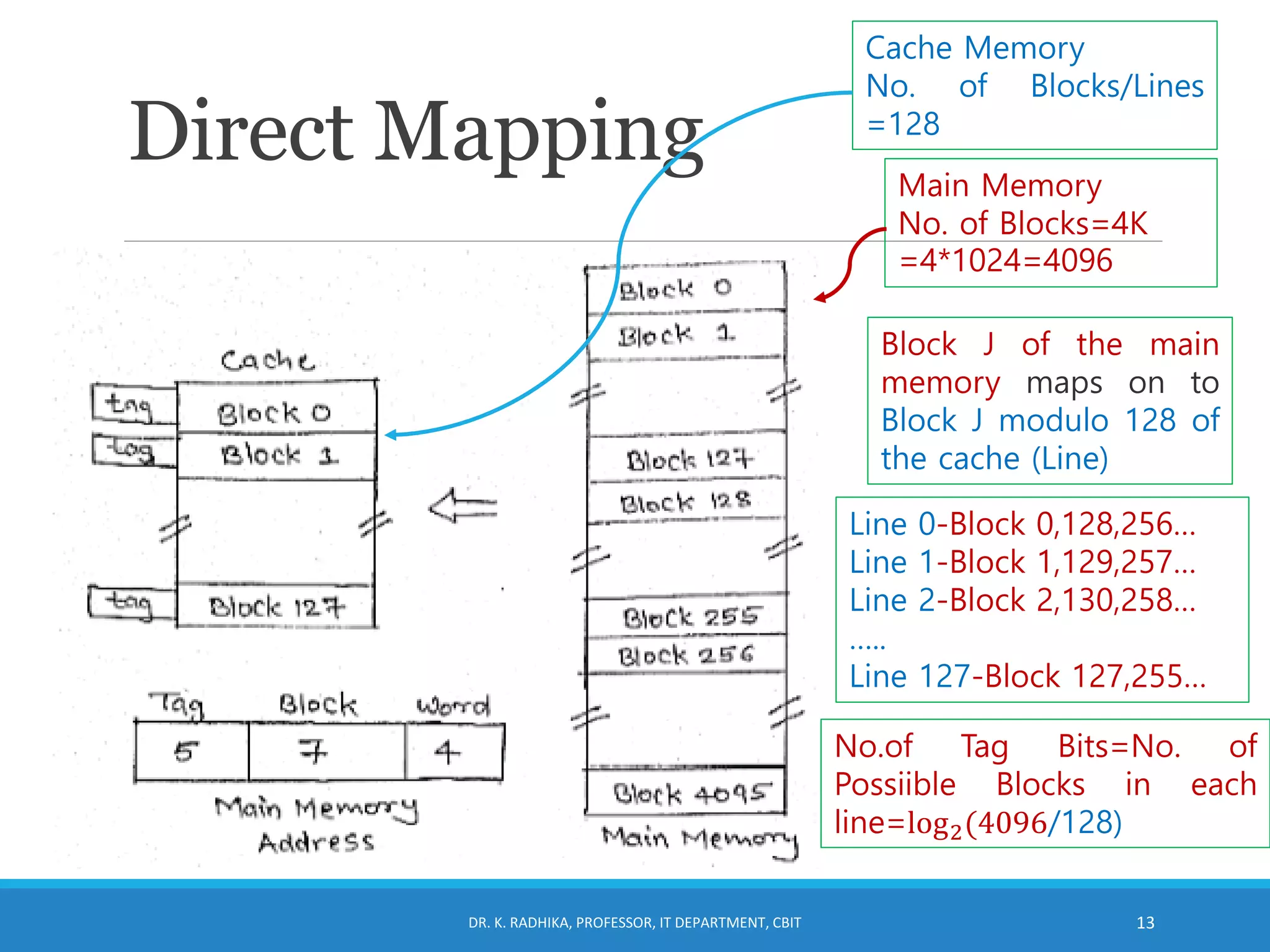

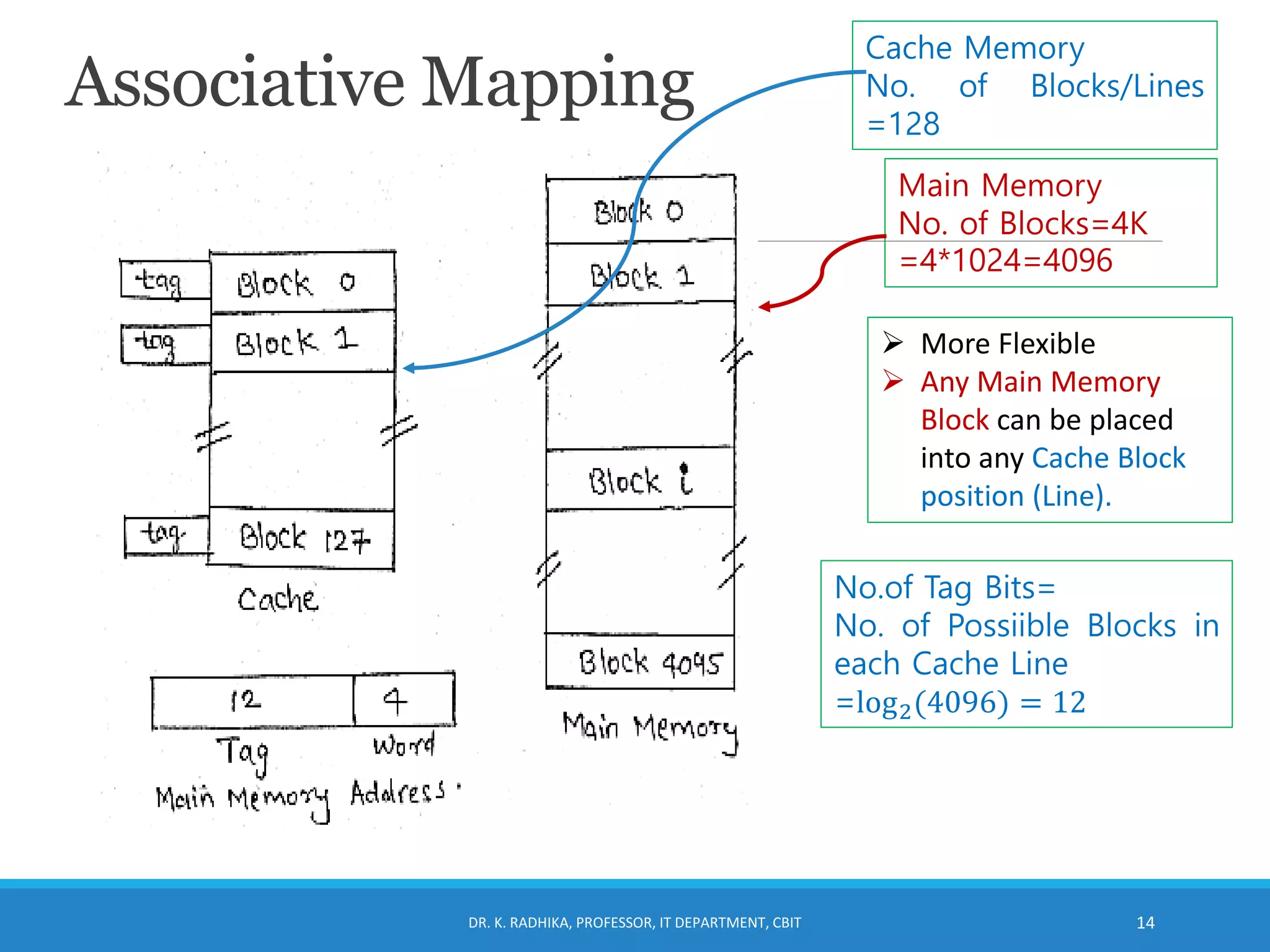

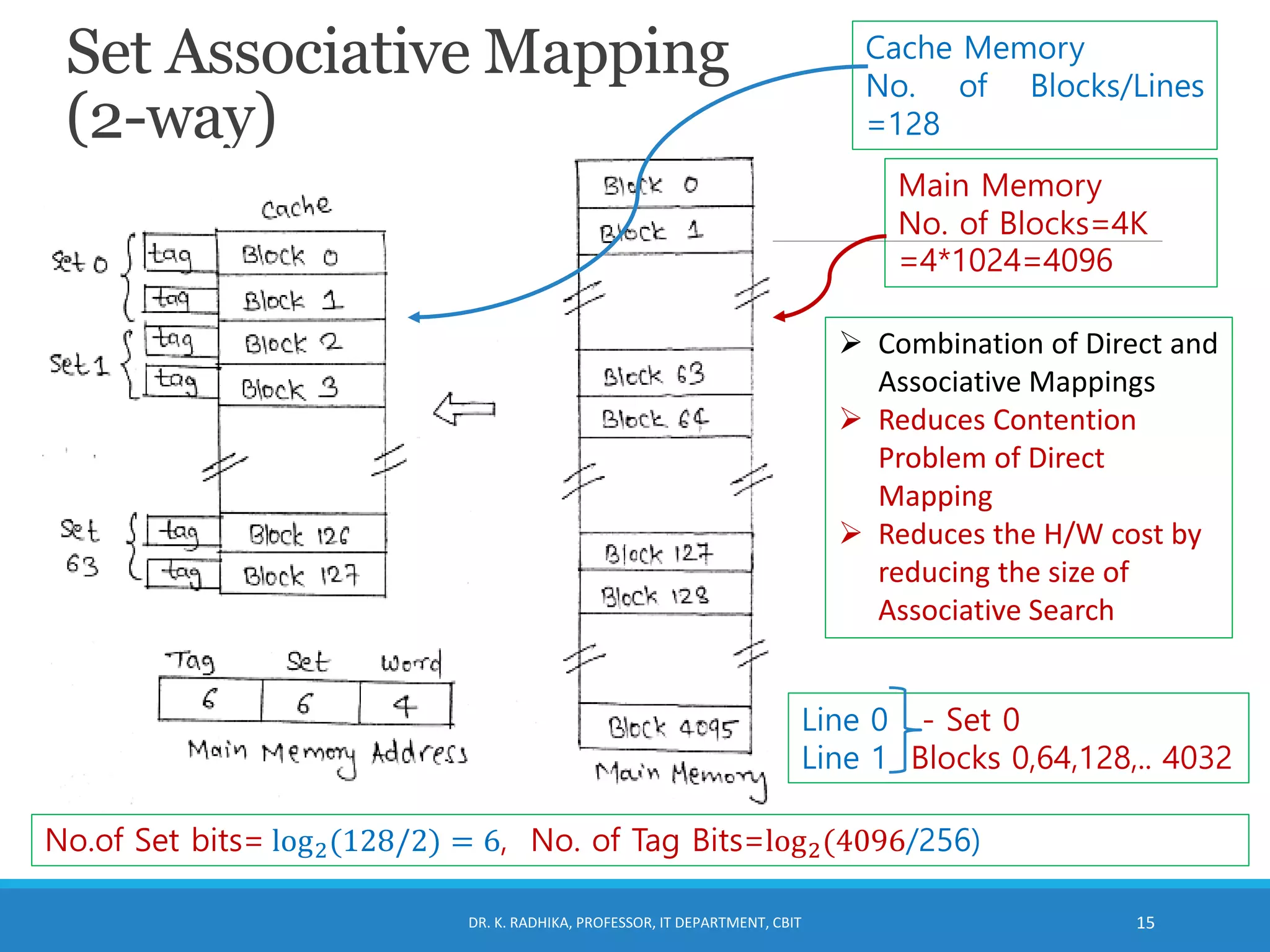

The document discusses cache memory organization. It describes how cache memory uses the principle of locality of reference to improve memory access time. It is placed between the CPU and main memory and is 10-100 times faster. The document introduces cache hit ratio and average memory access time formulas. It then covers different cache mapping techniques - direct mapping, associative mapping, and set-associative mapping which map blocks of main memory to blocks of cache memory. Examples of 2-way set associative mapping are provided.