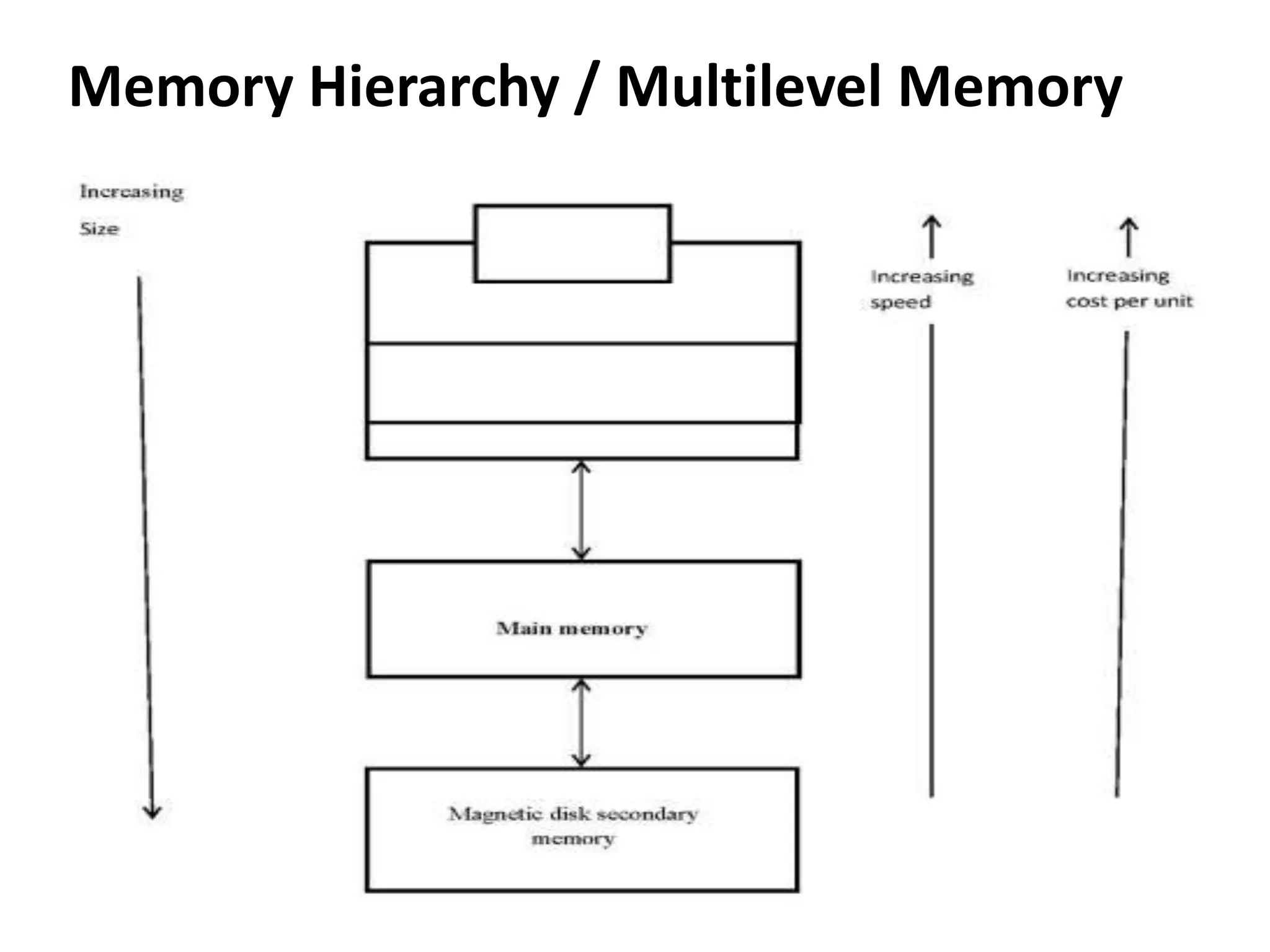

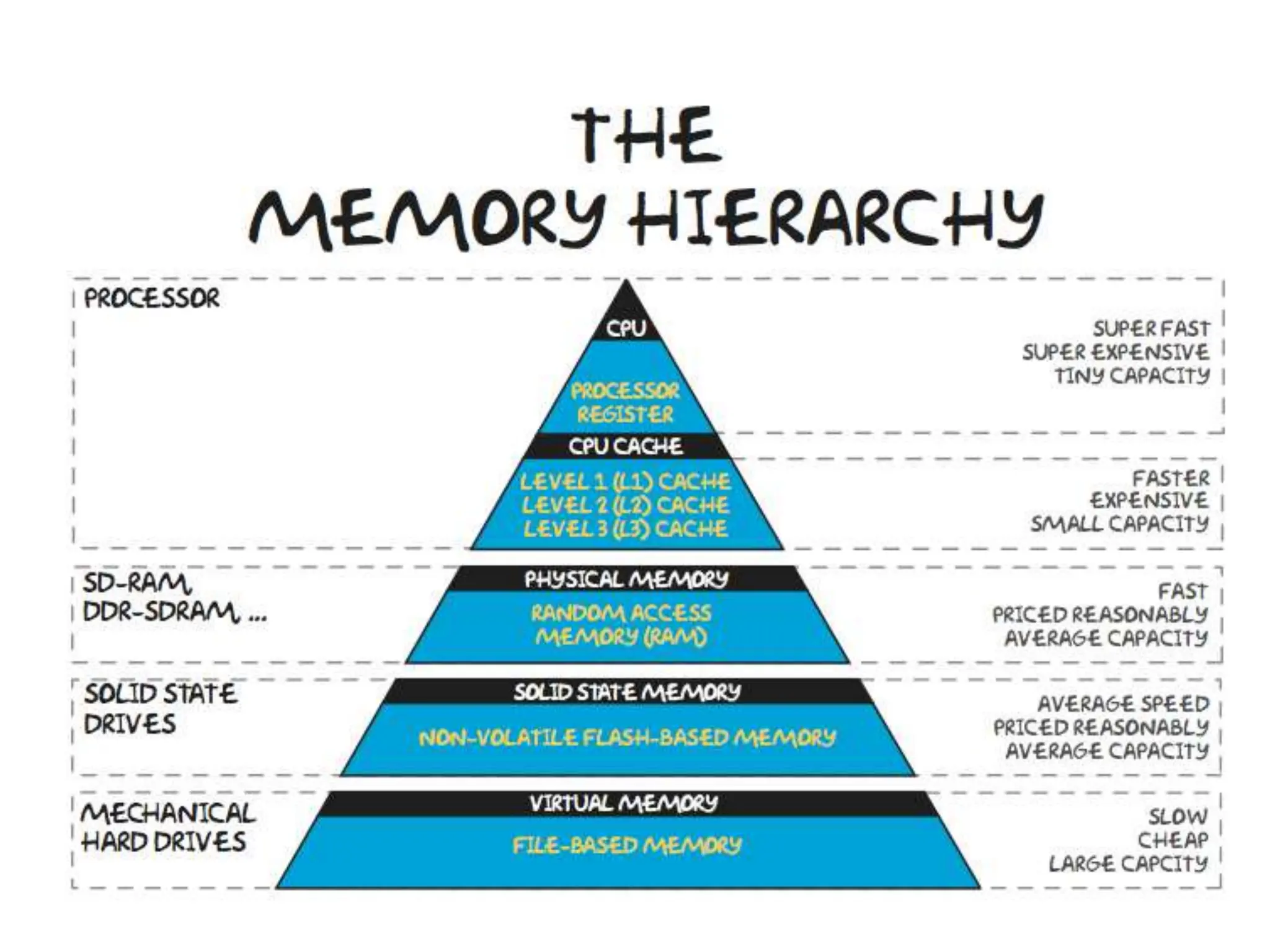

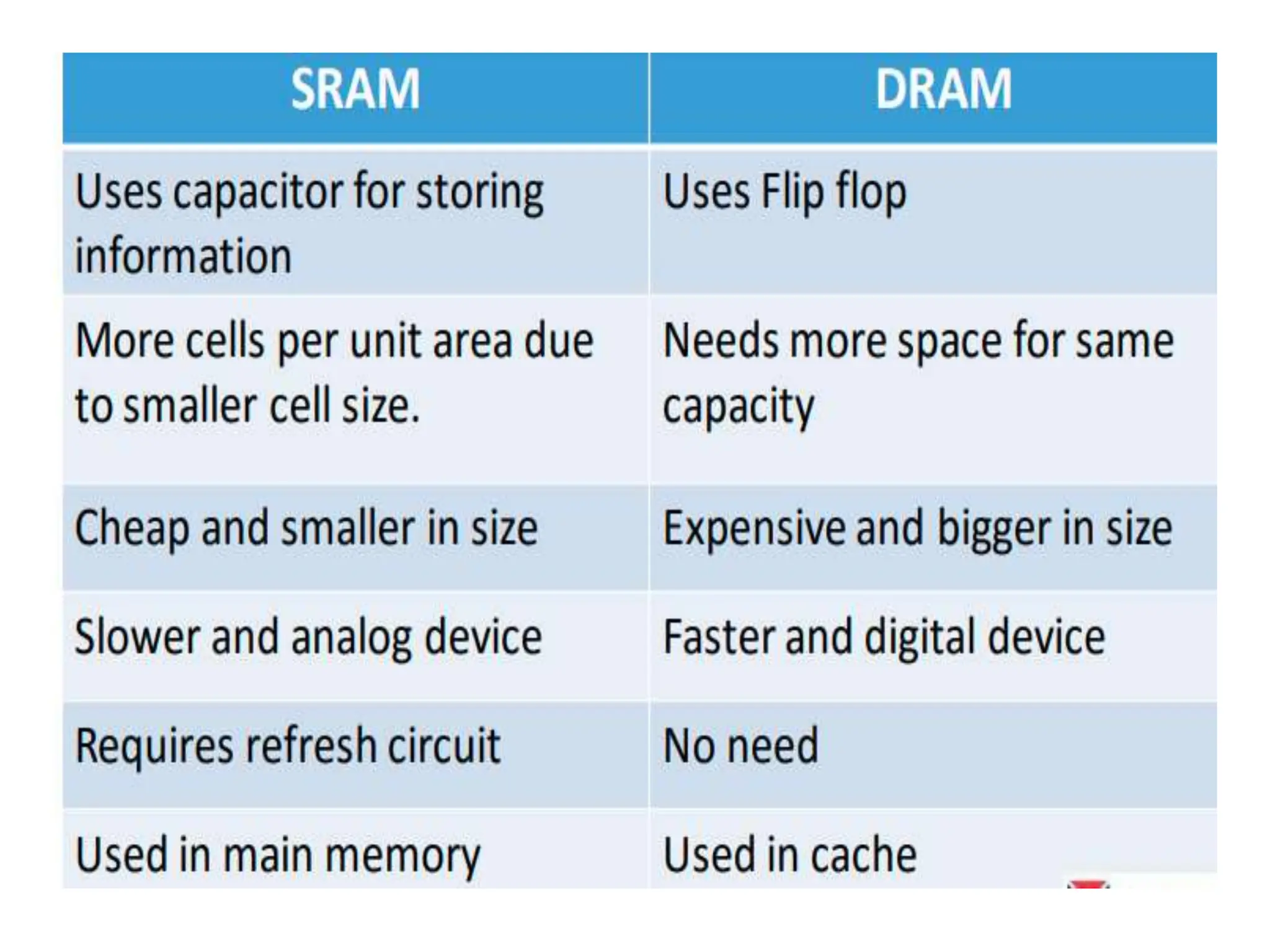

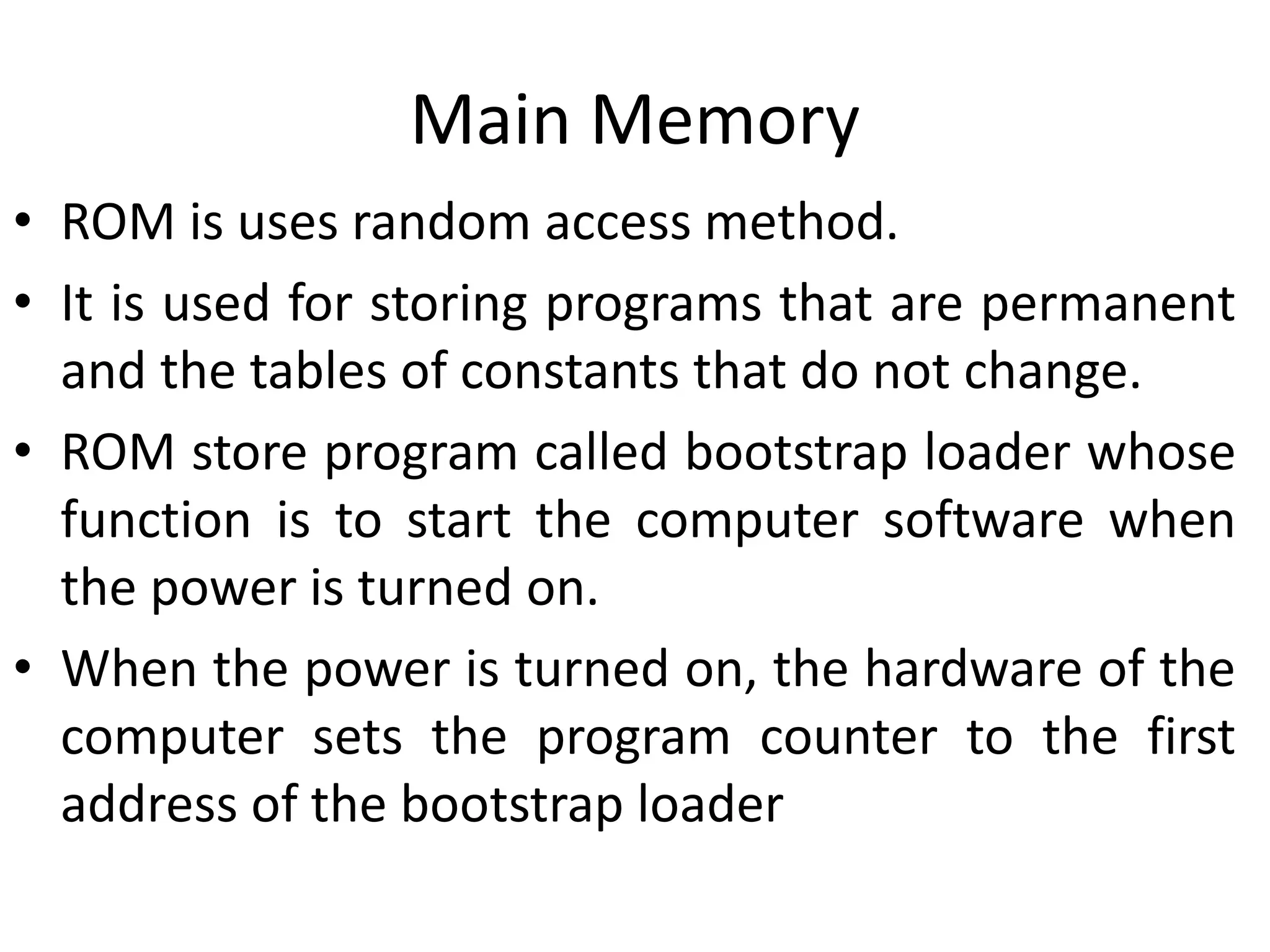

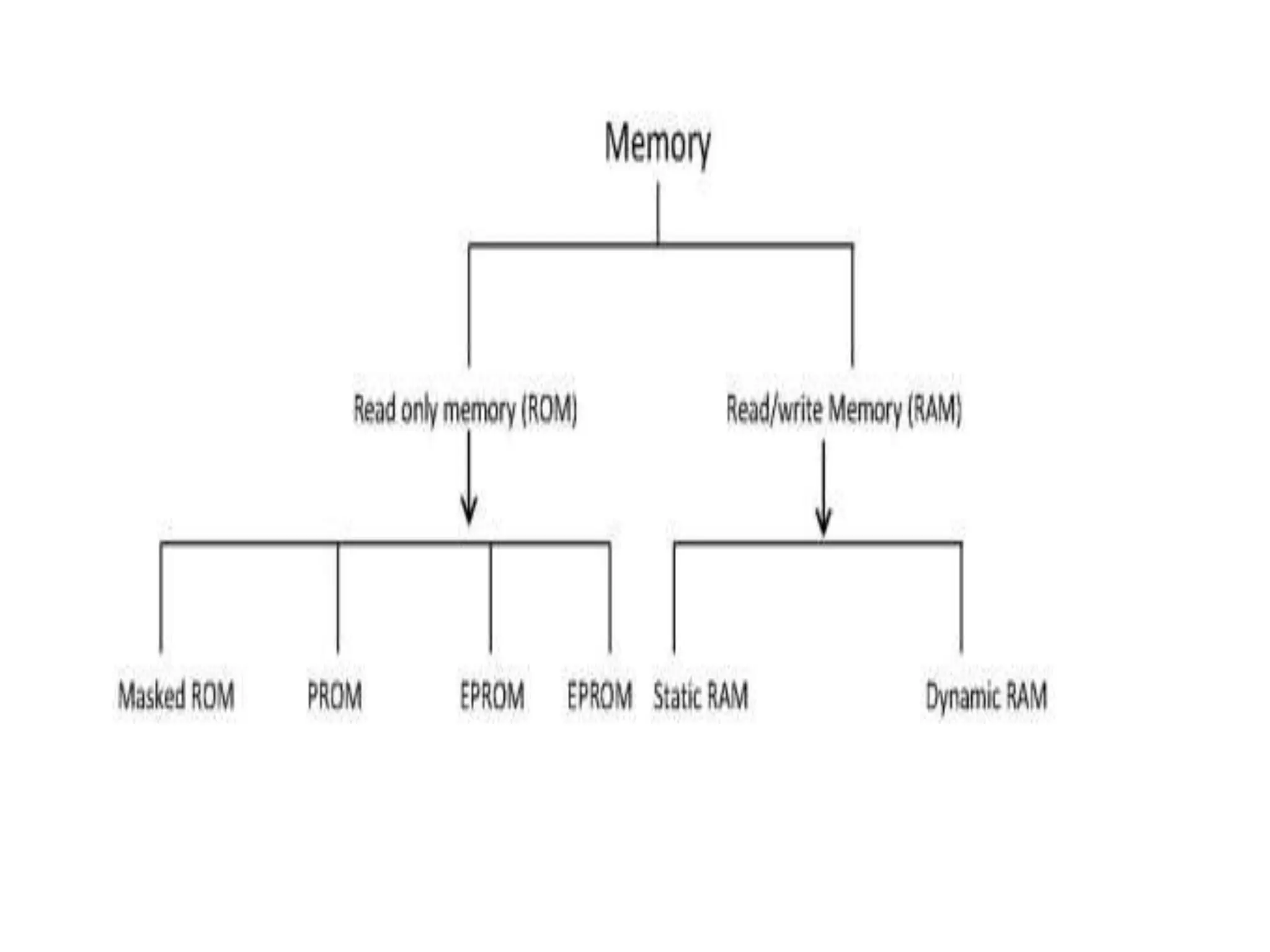

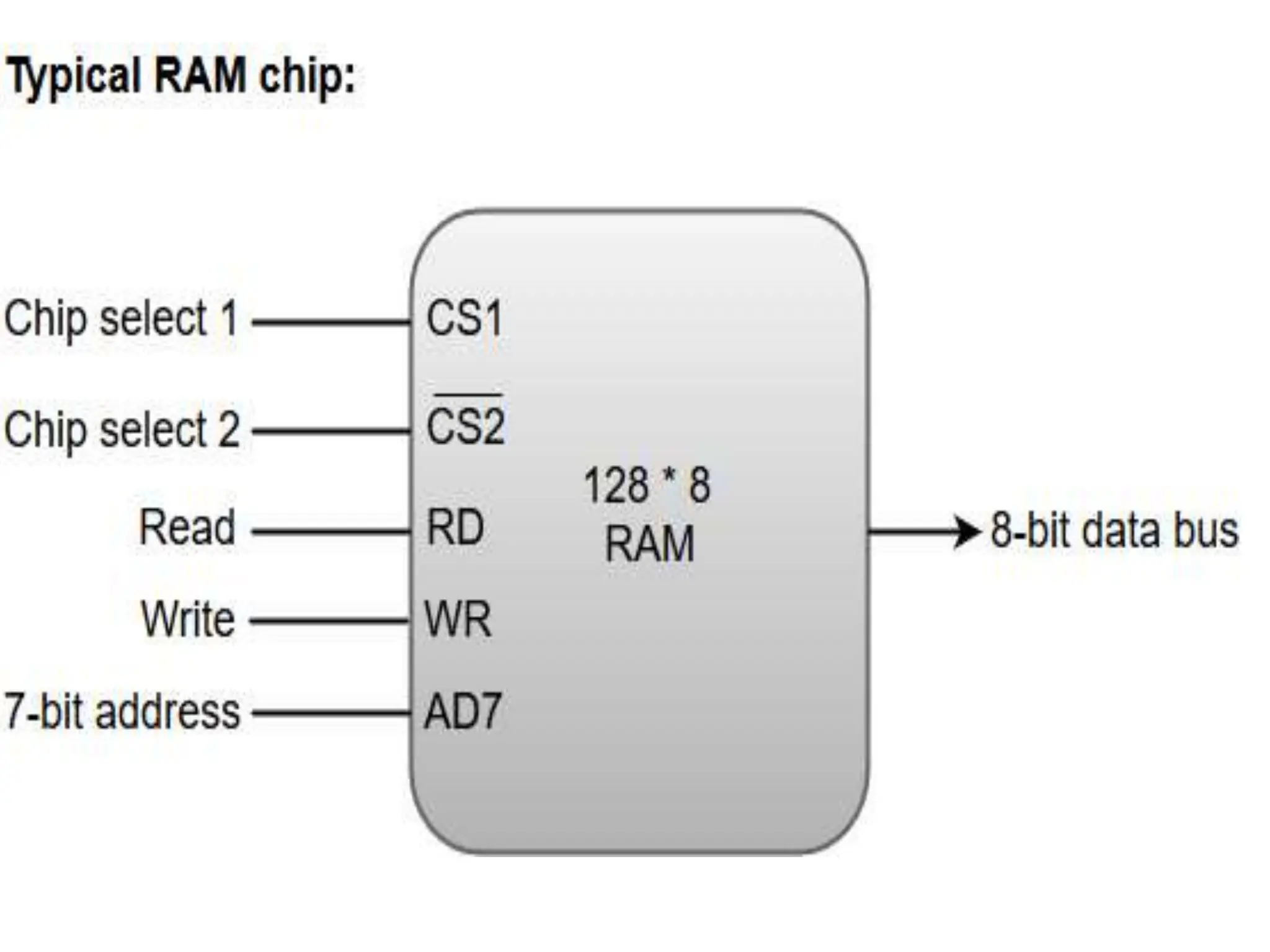

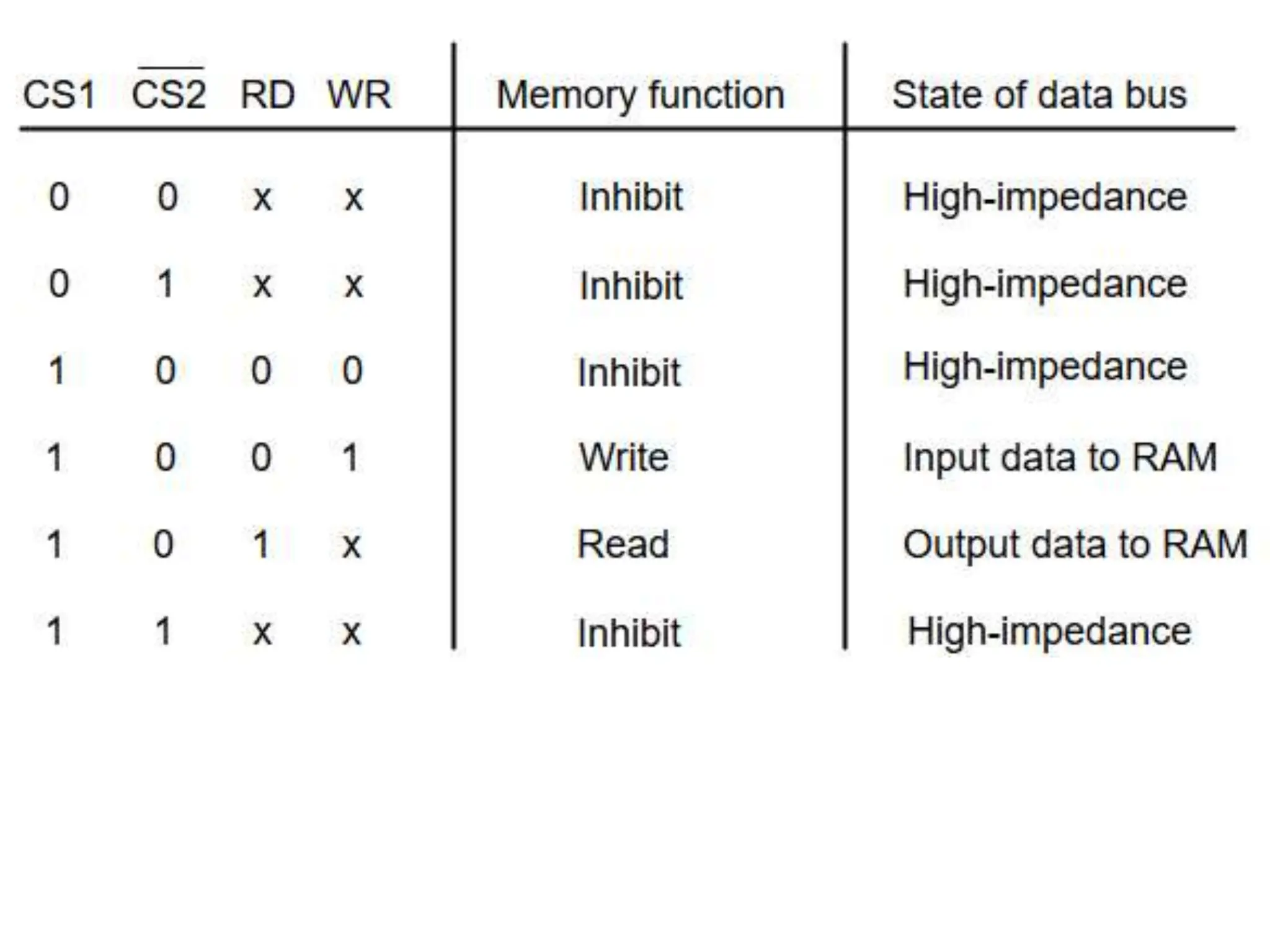

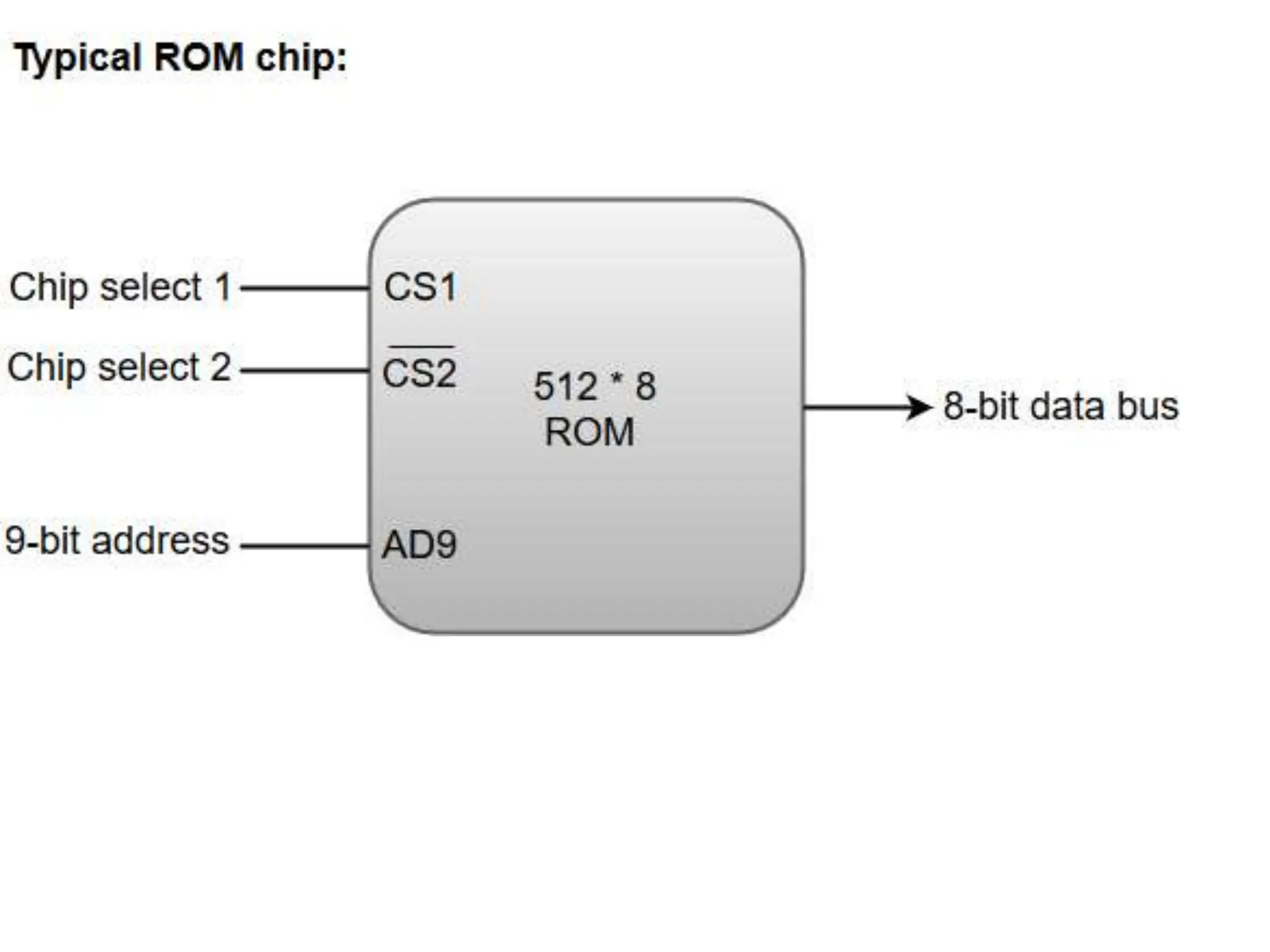

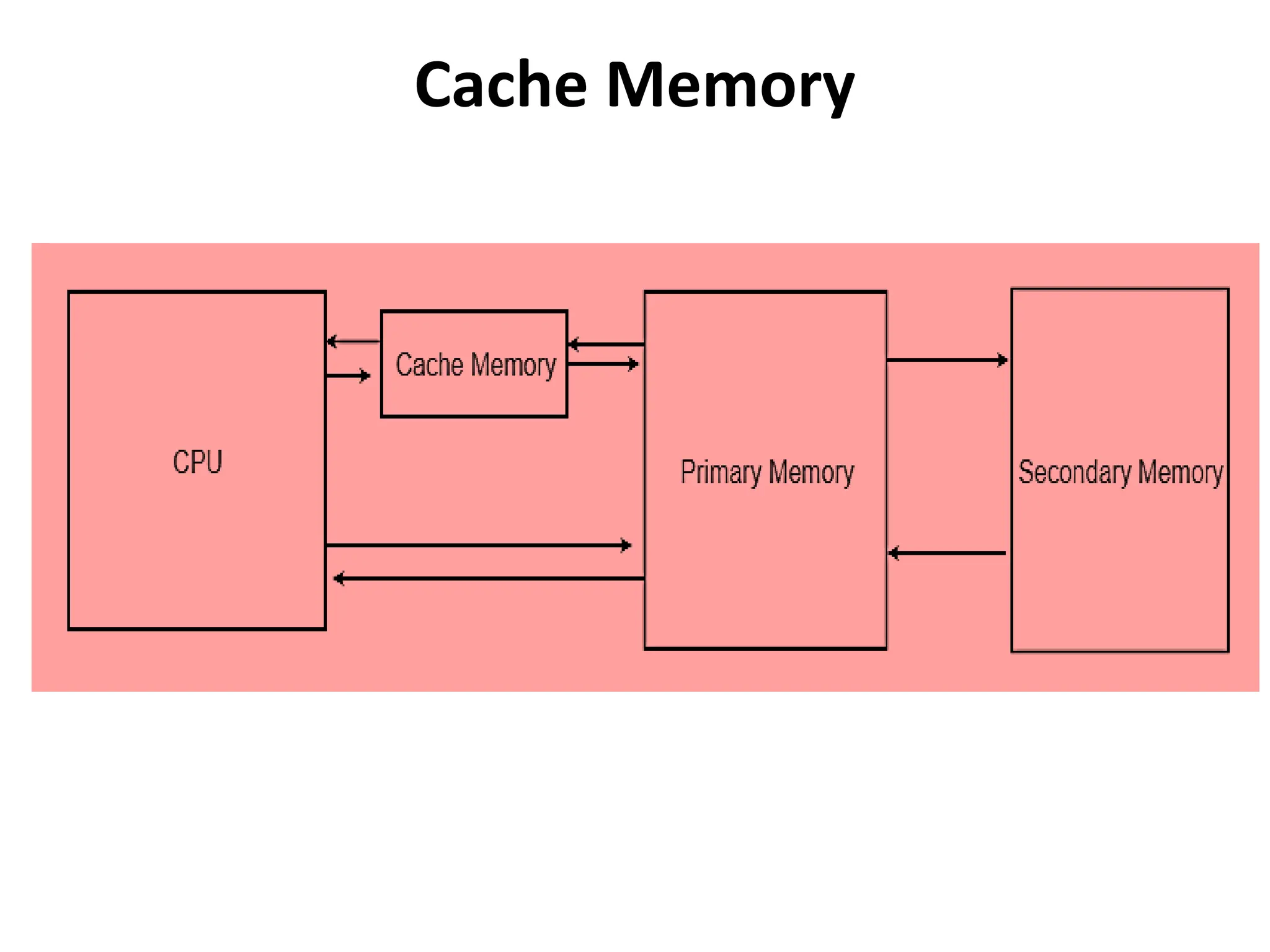

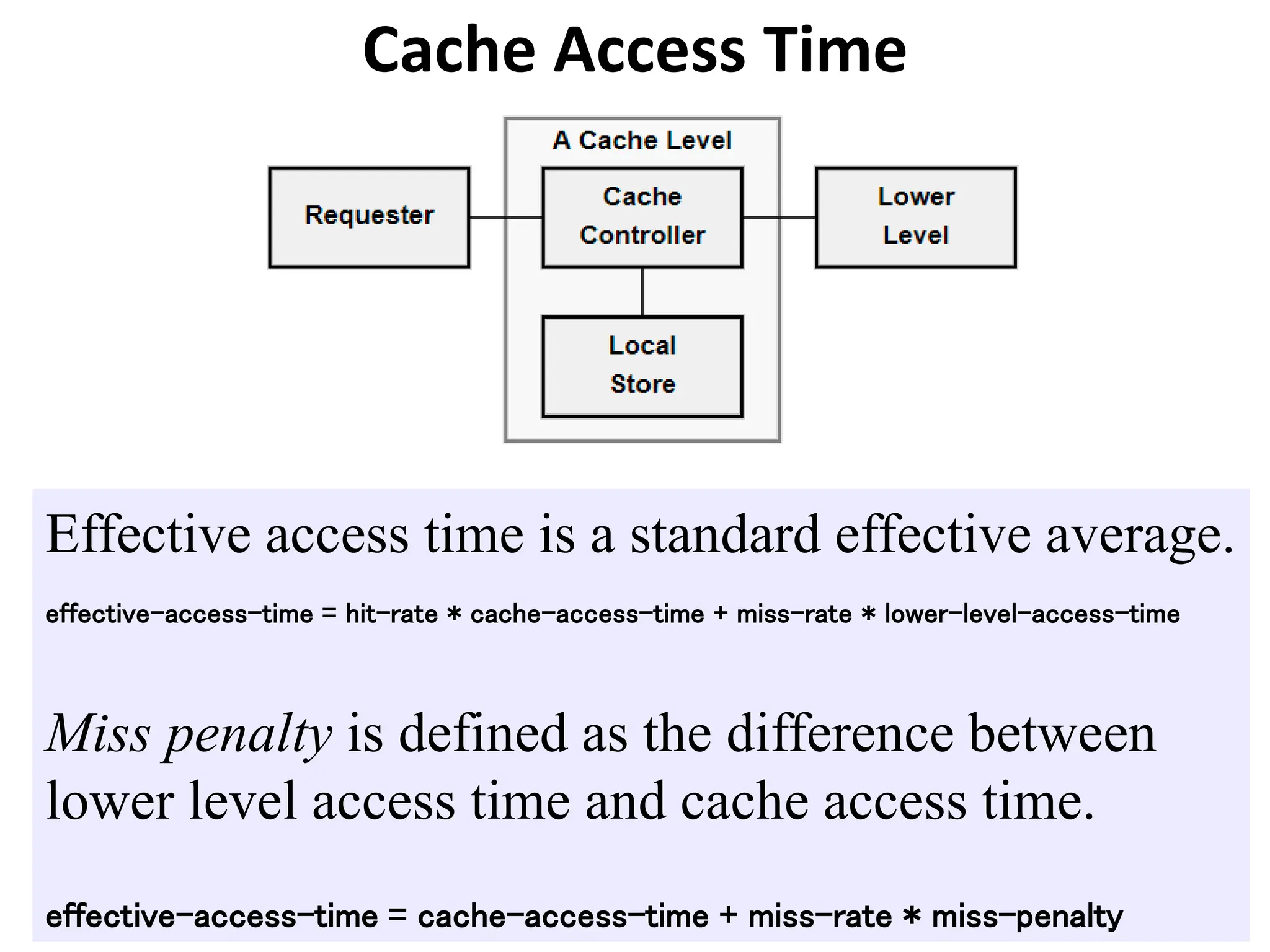

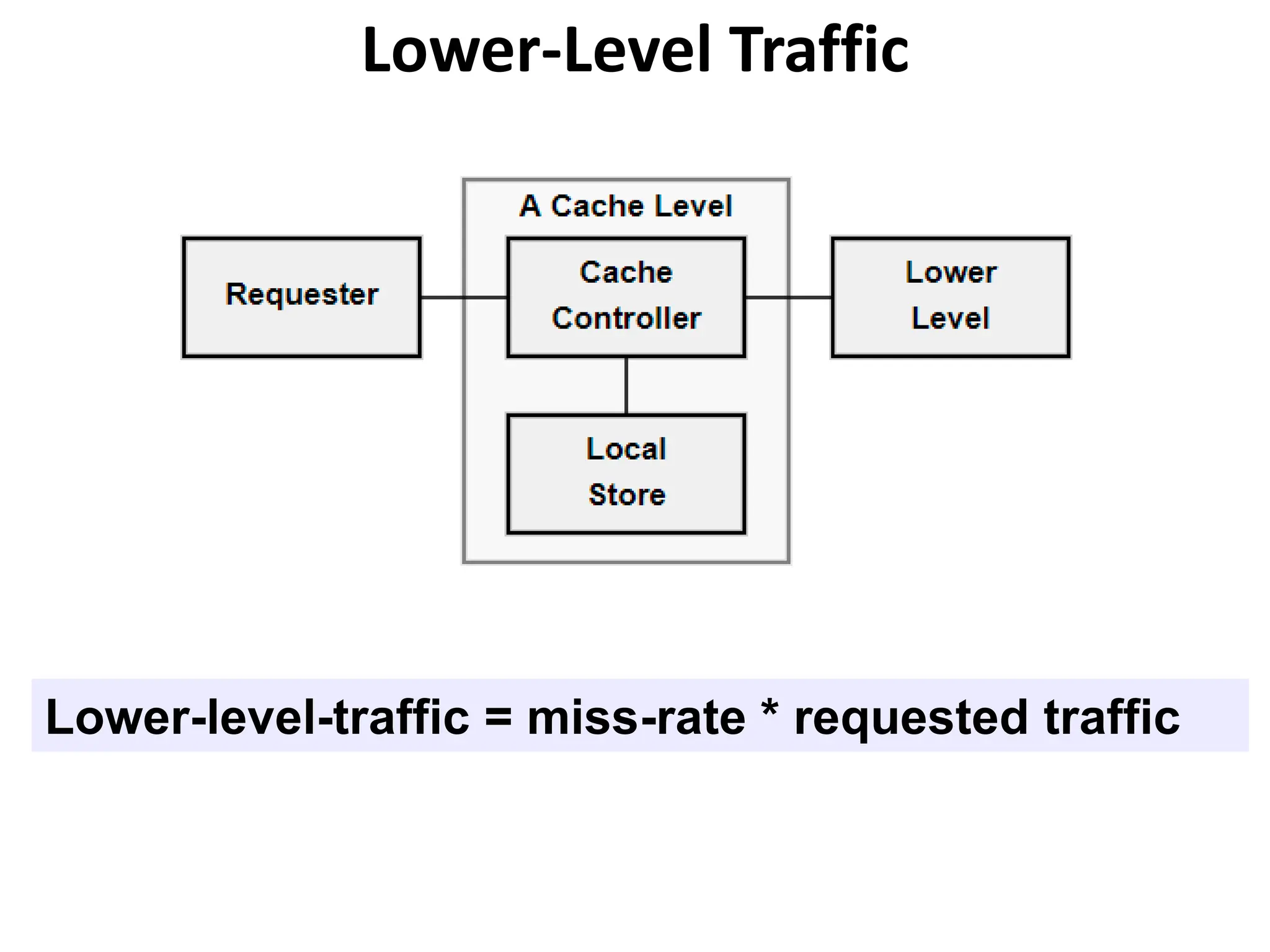

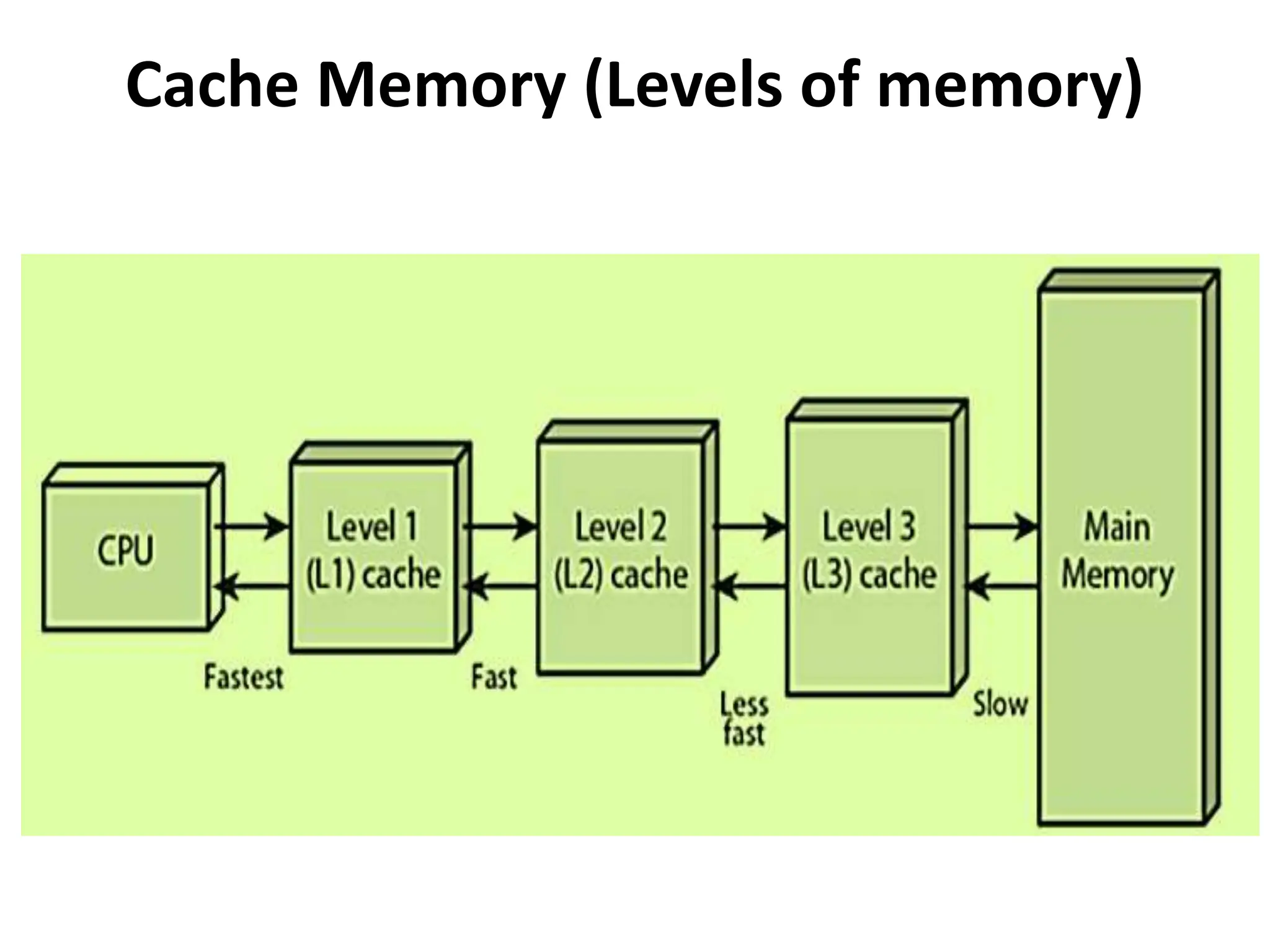

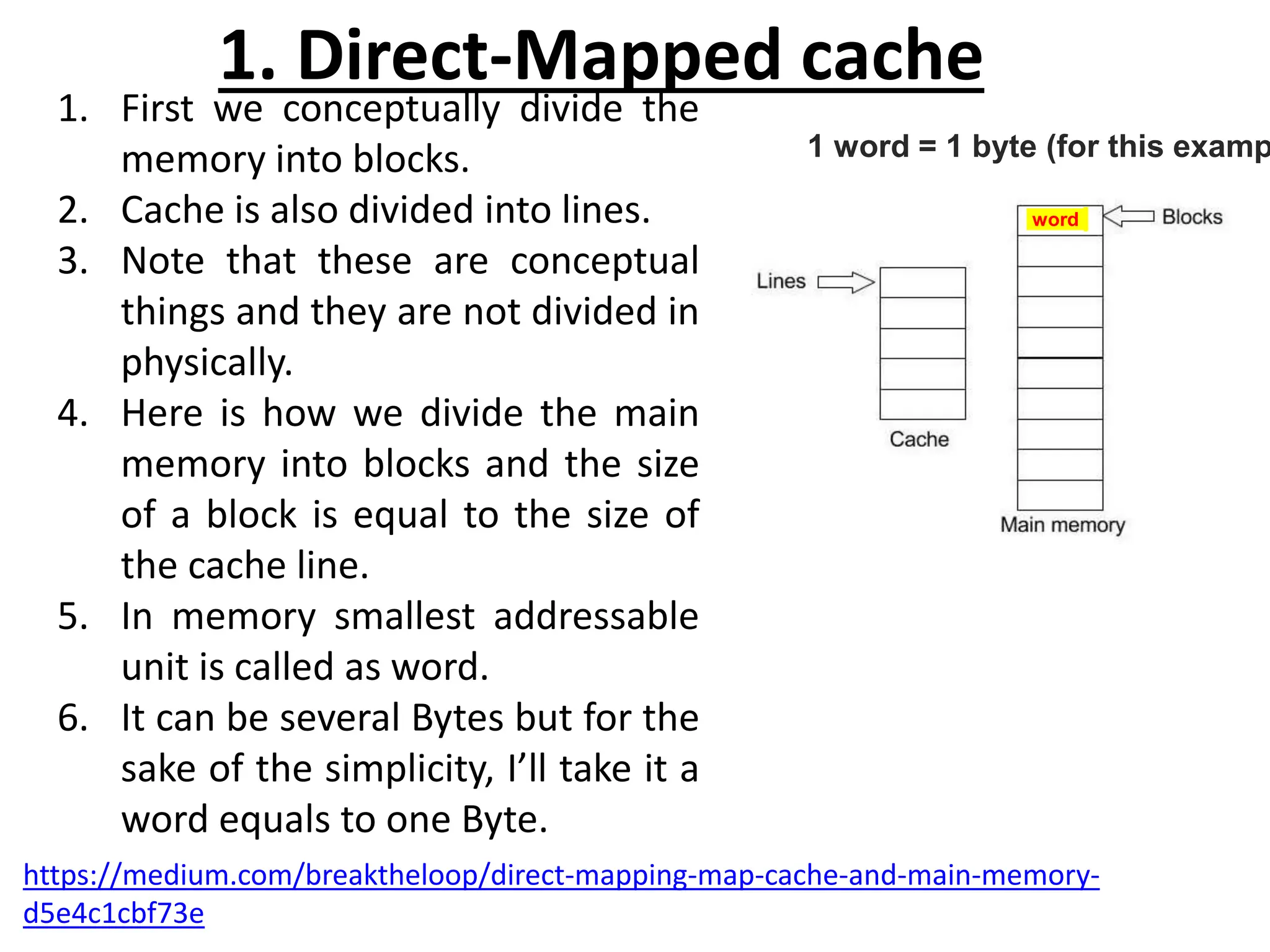

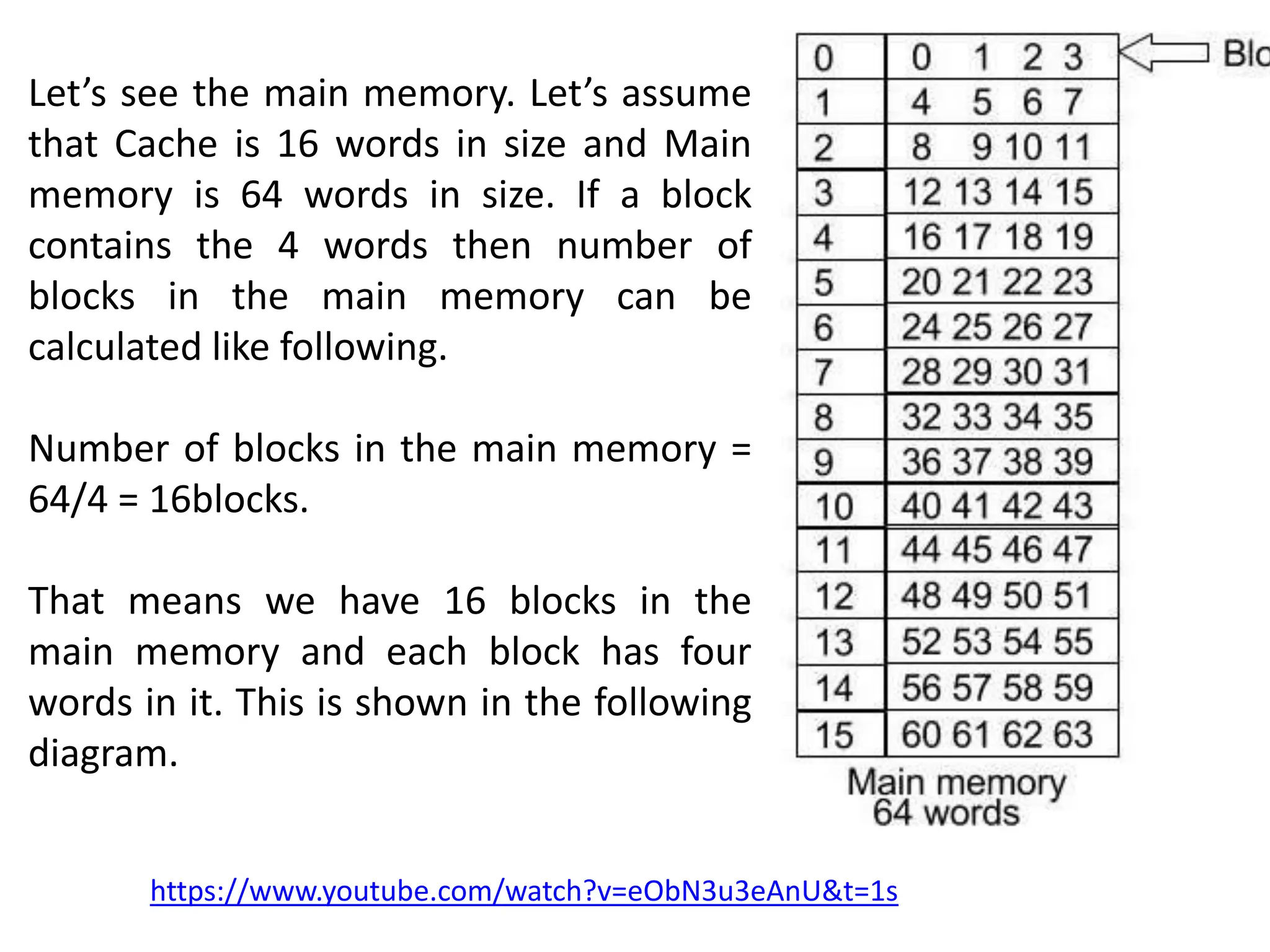

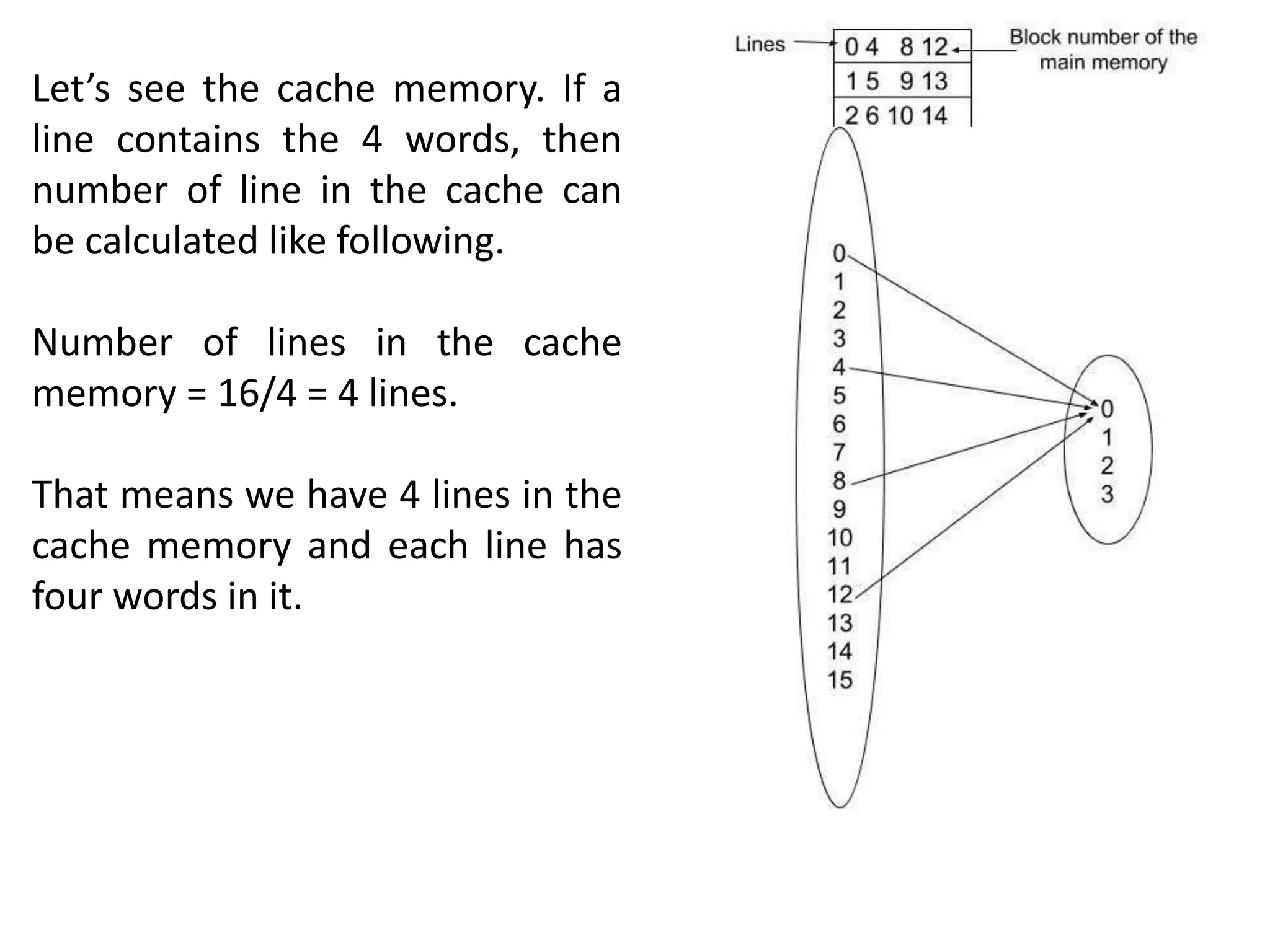

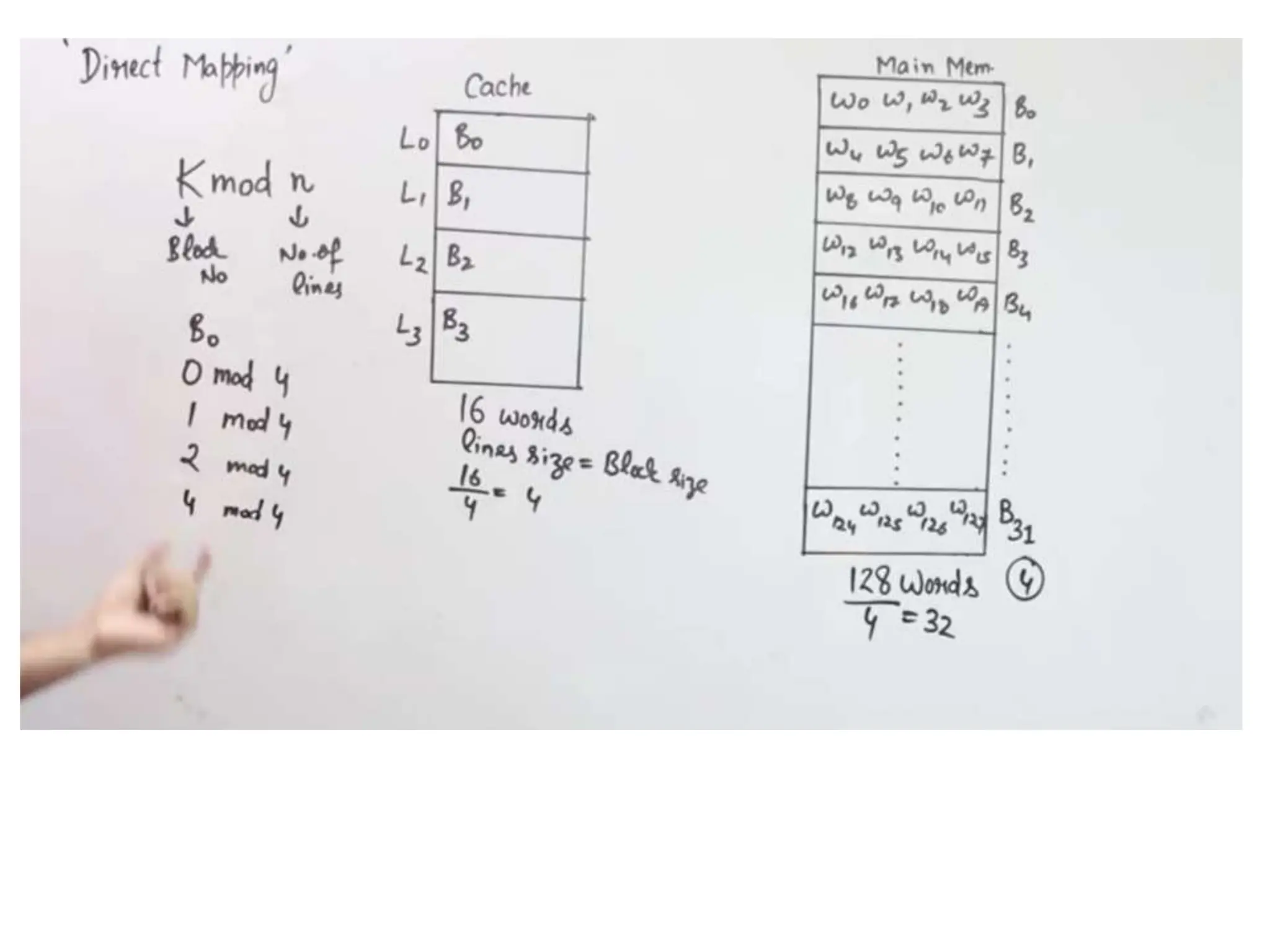

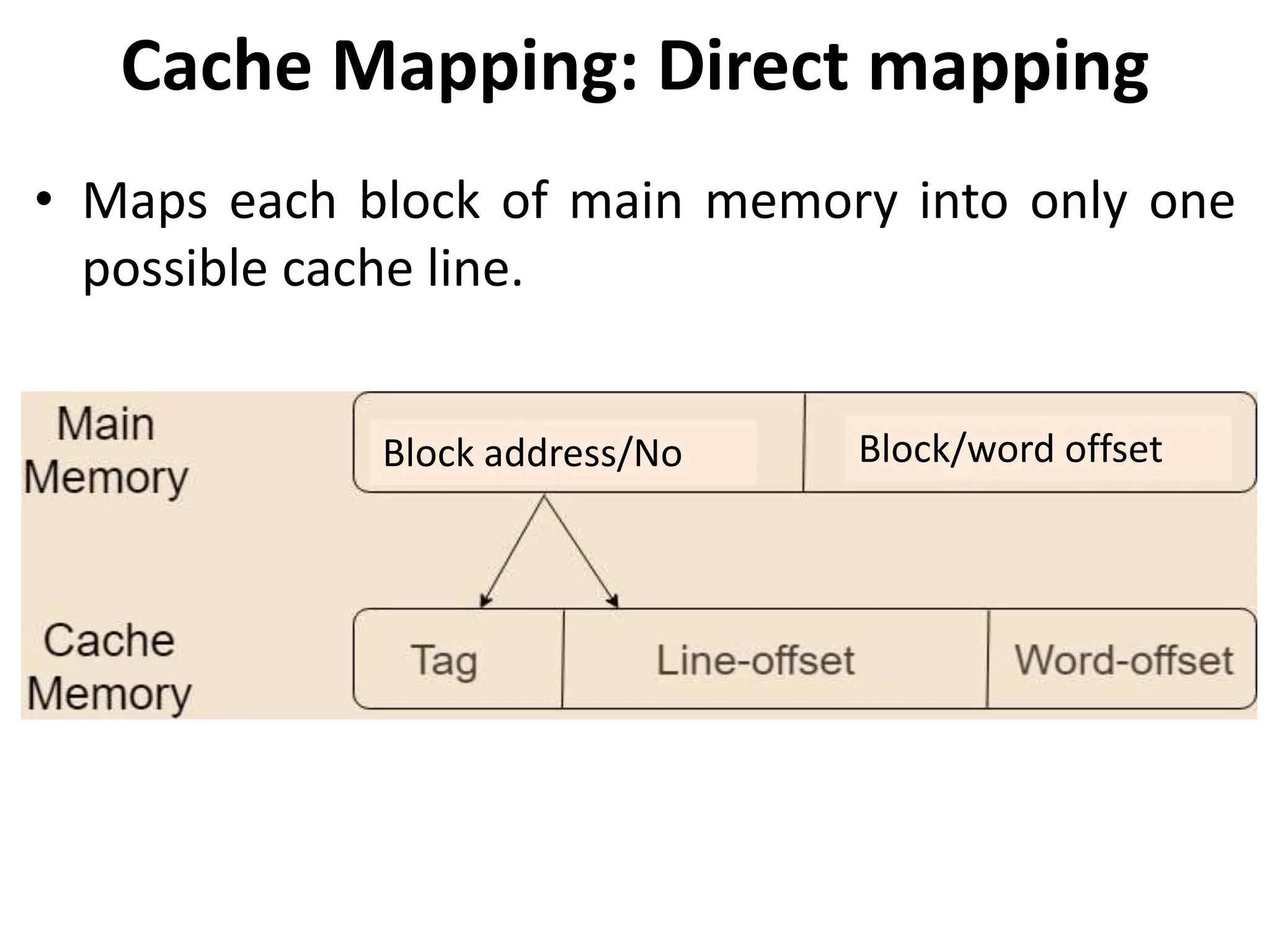

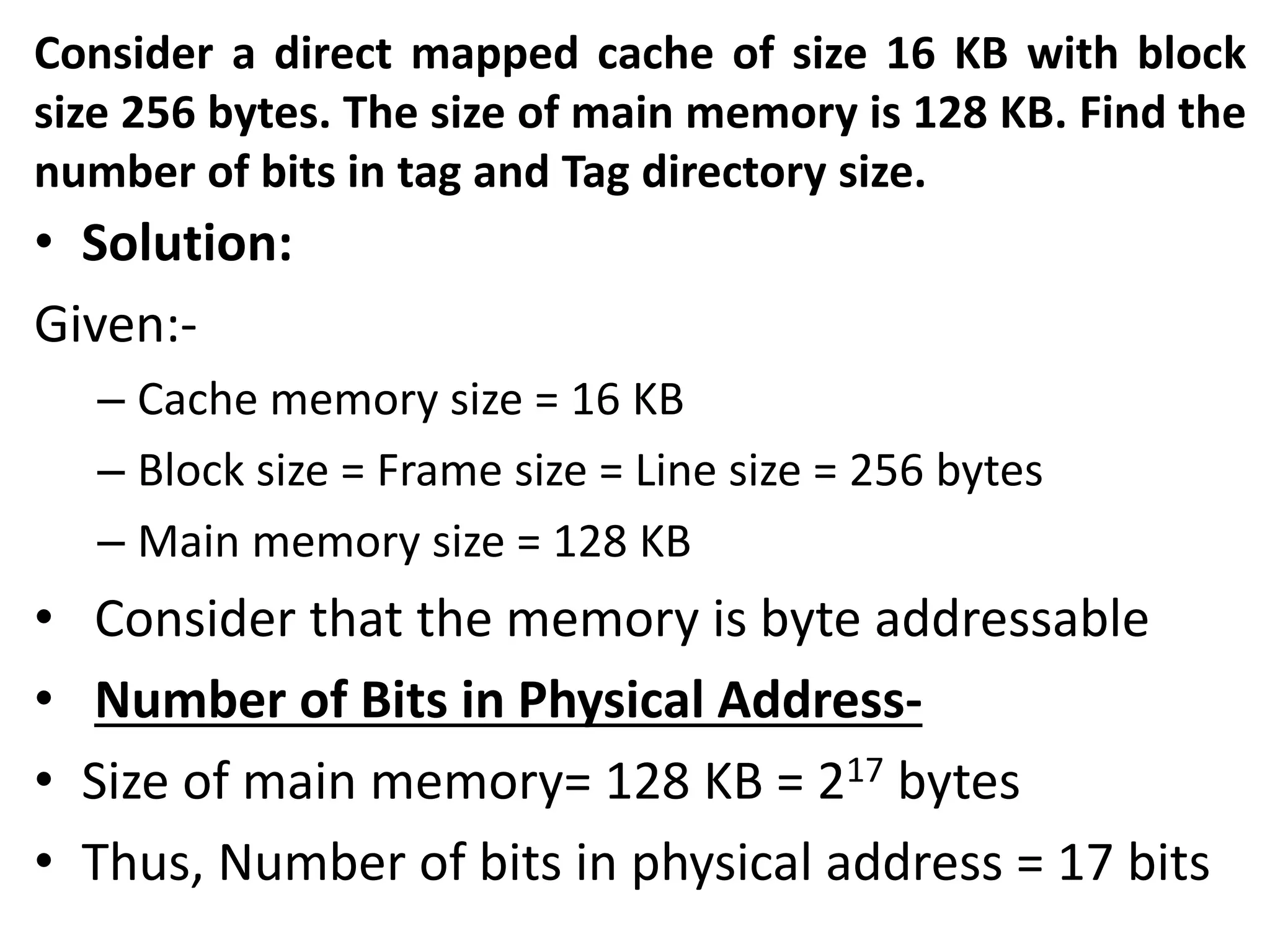

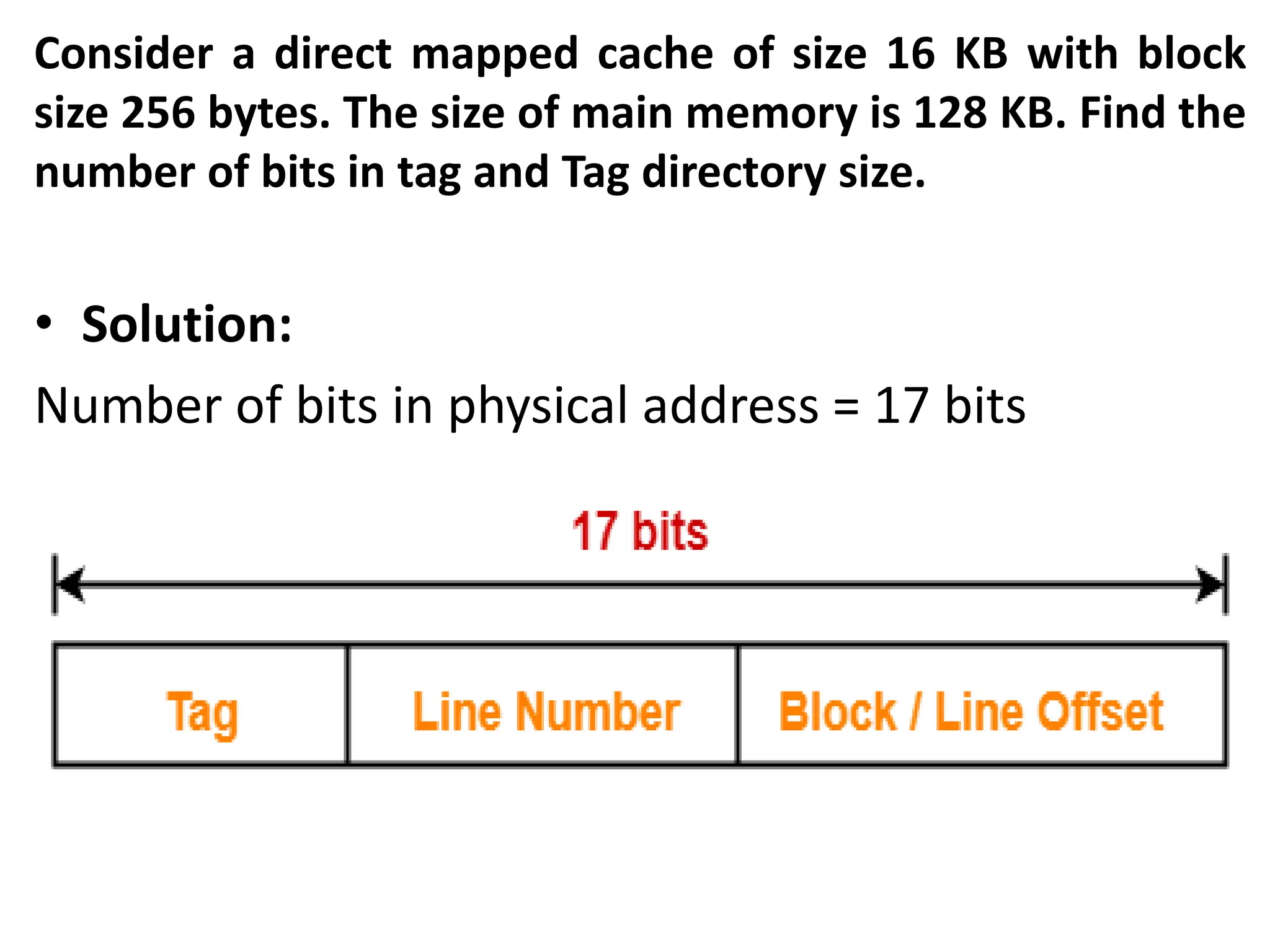

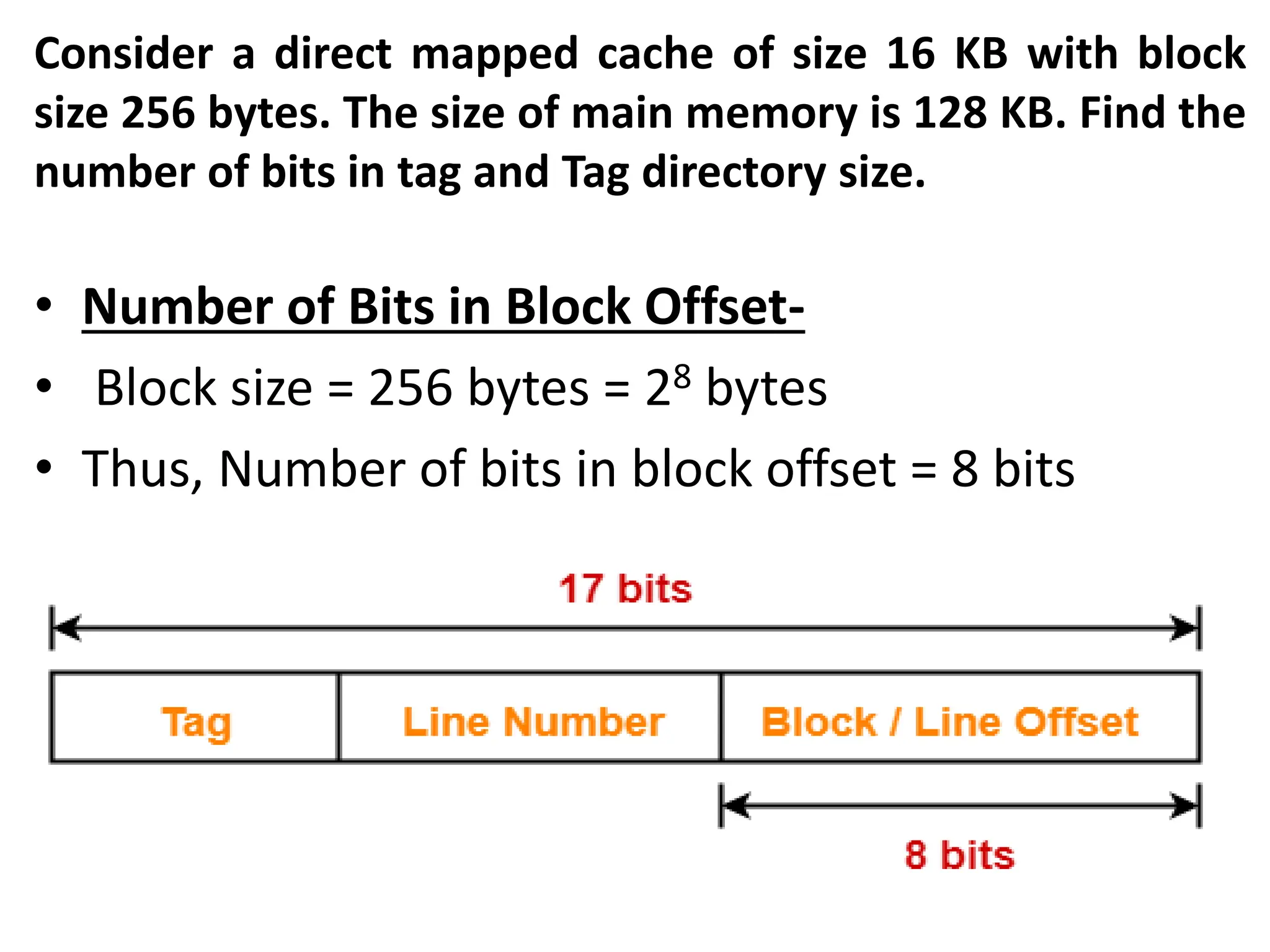

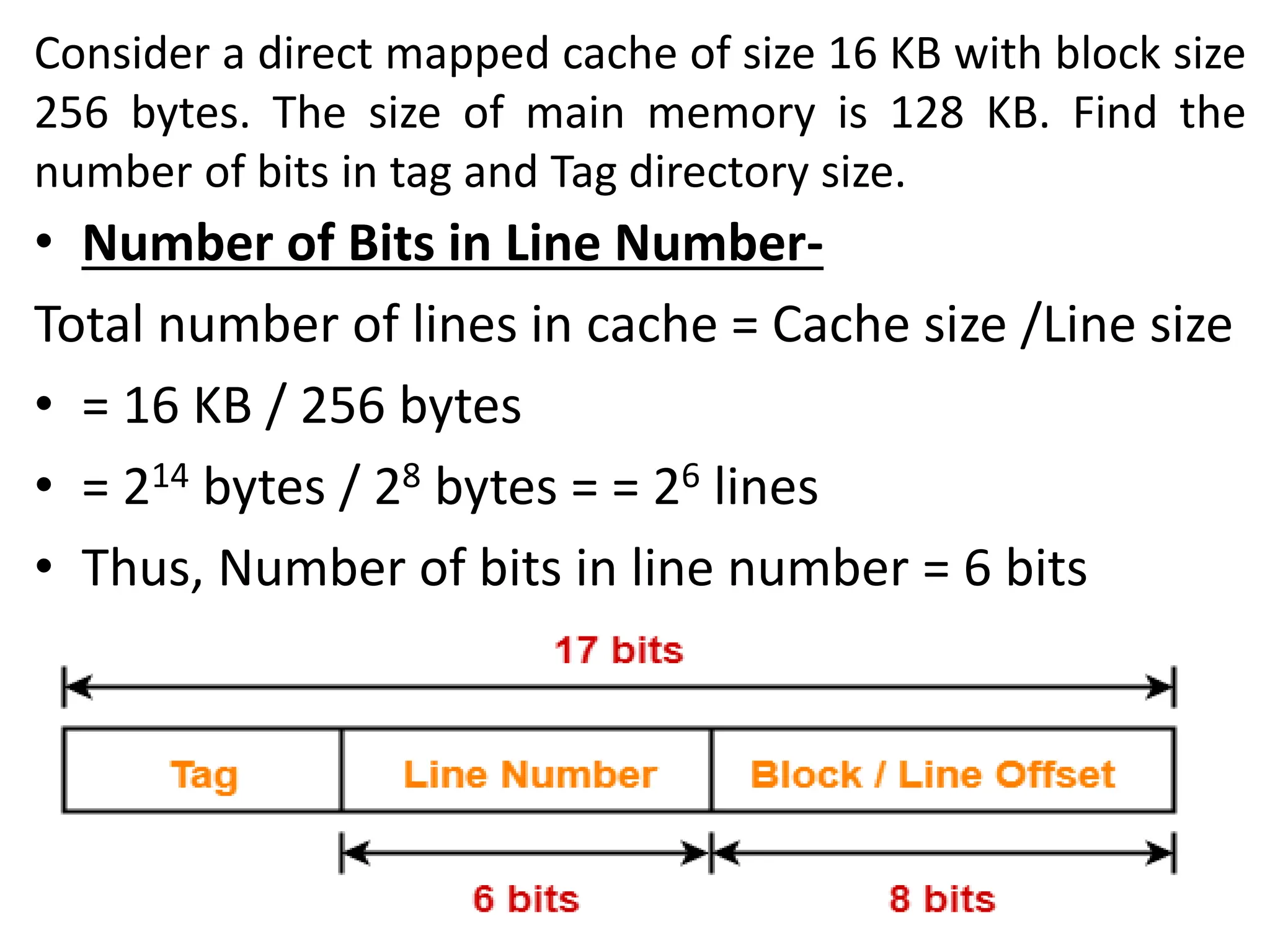

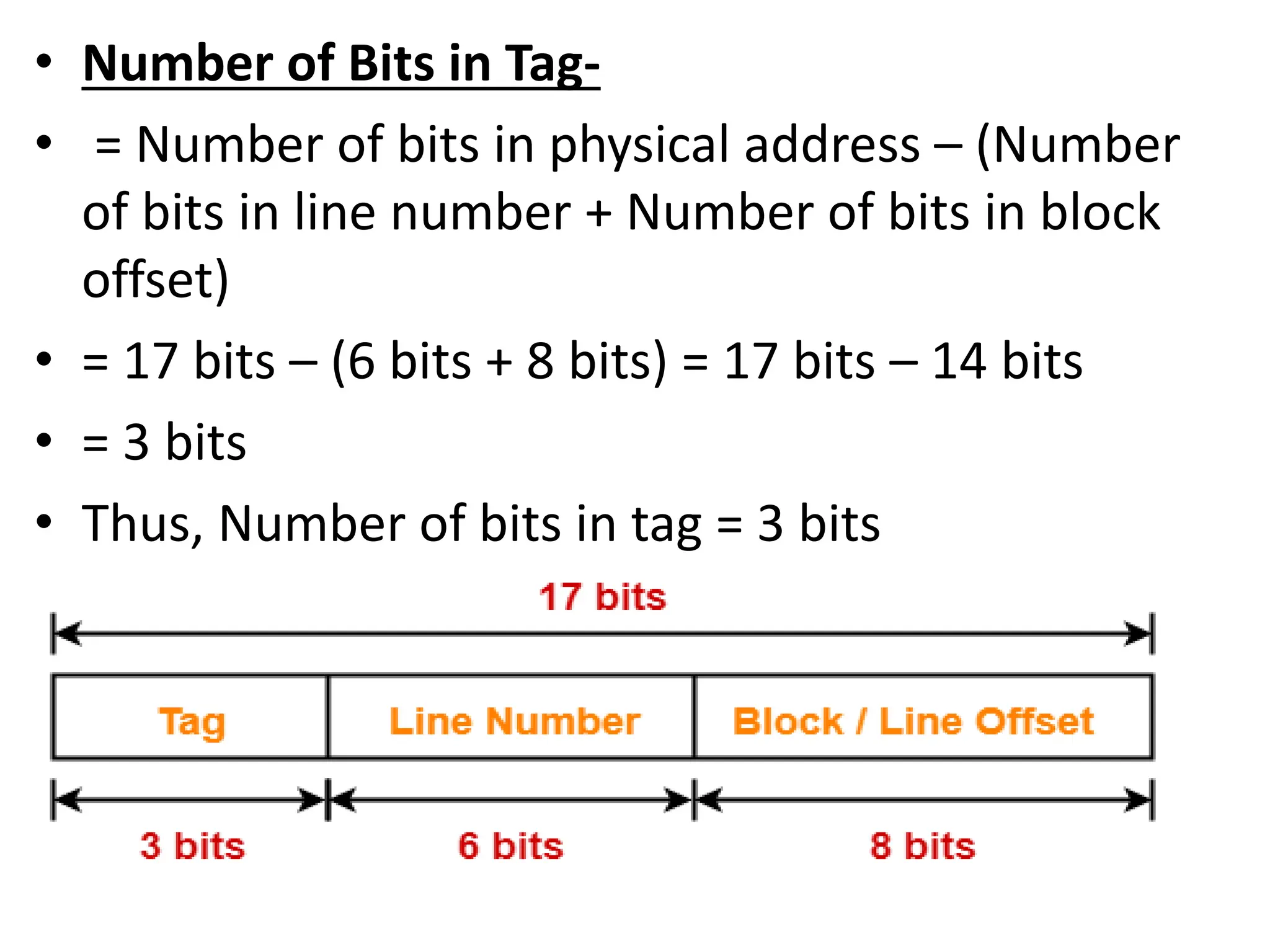

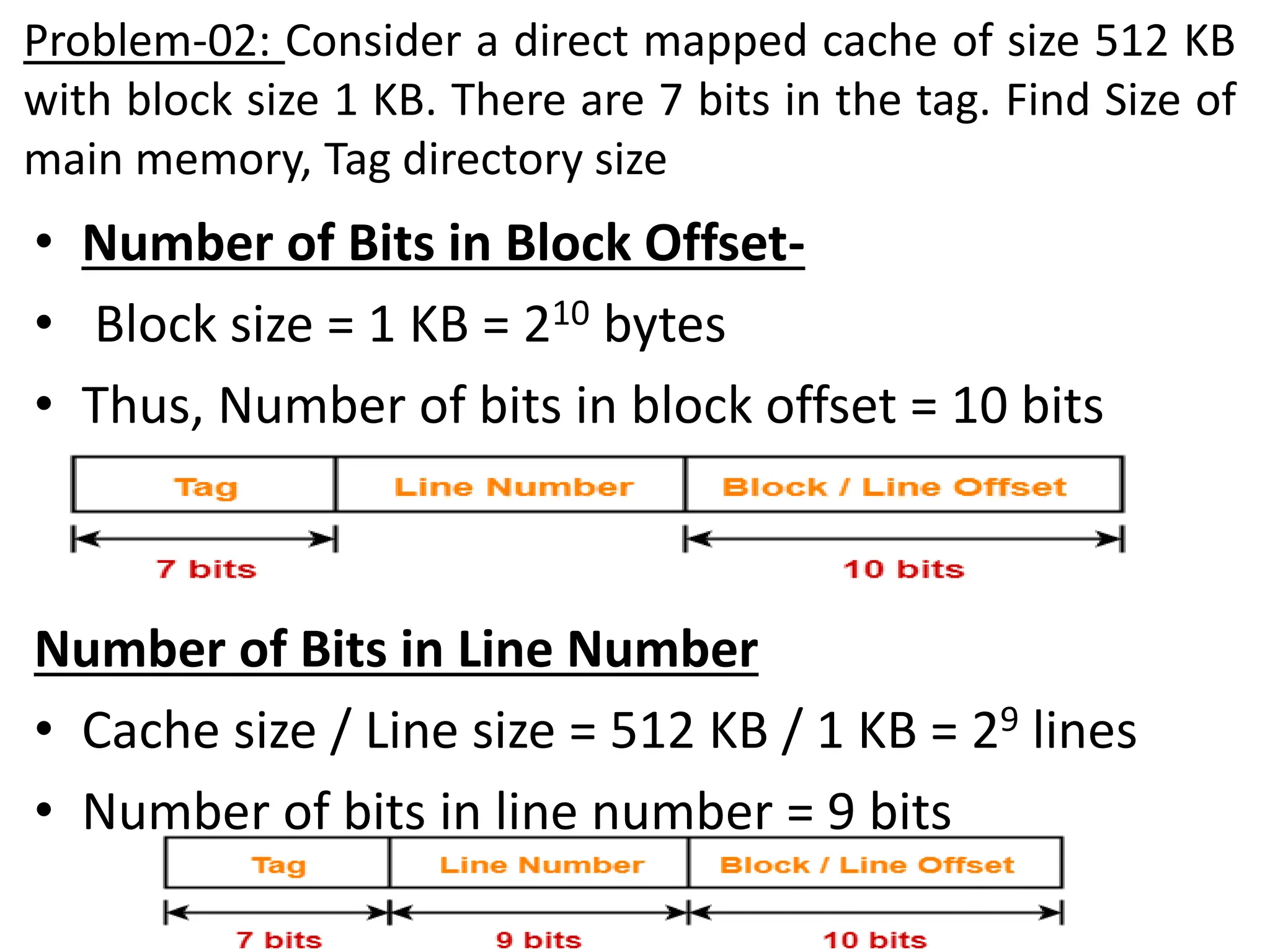

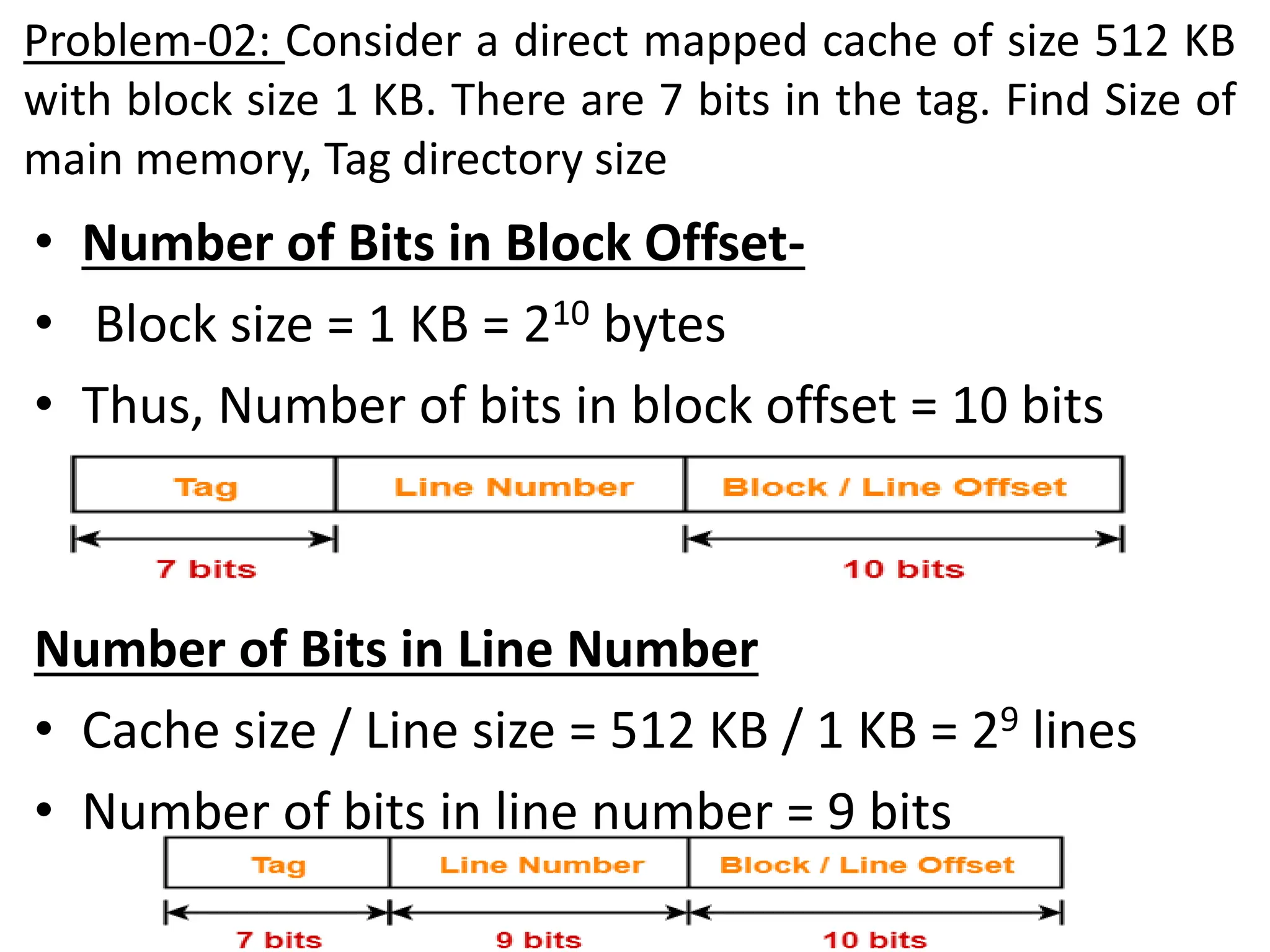

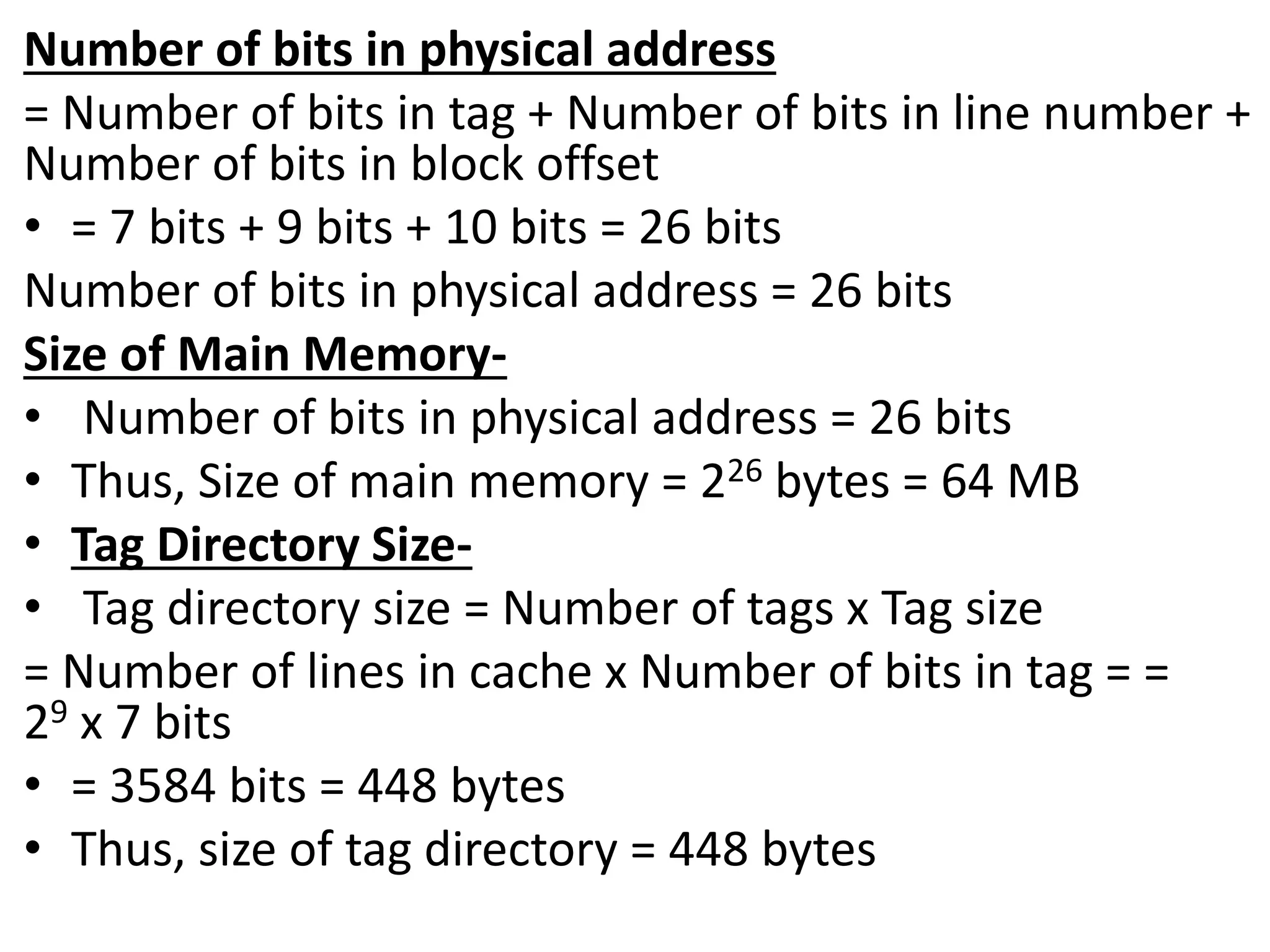

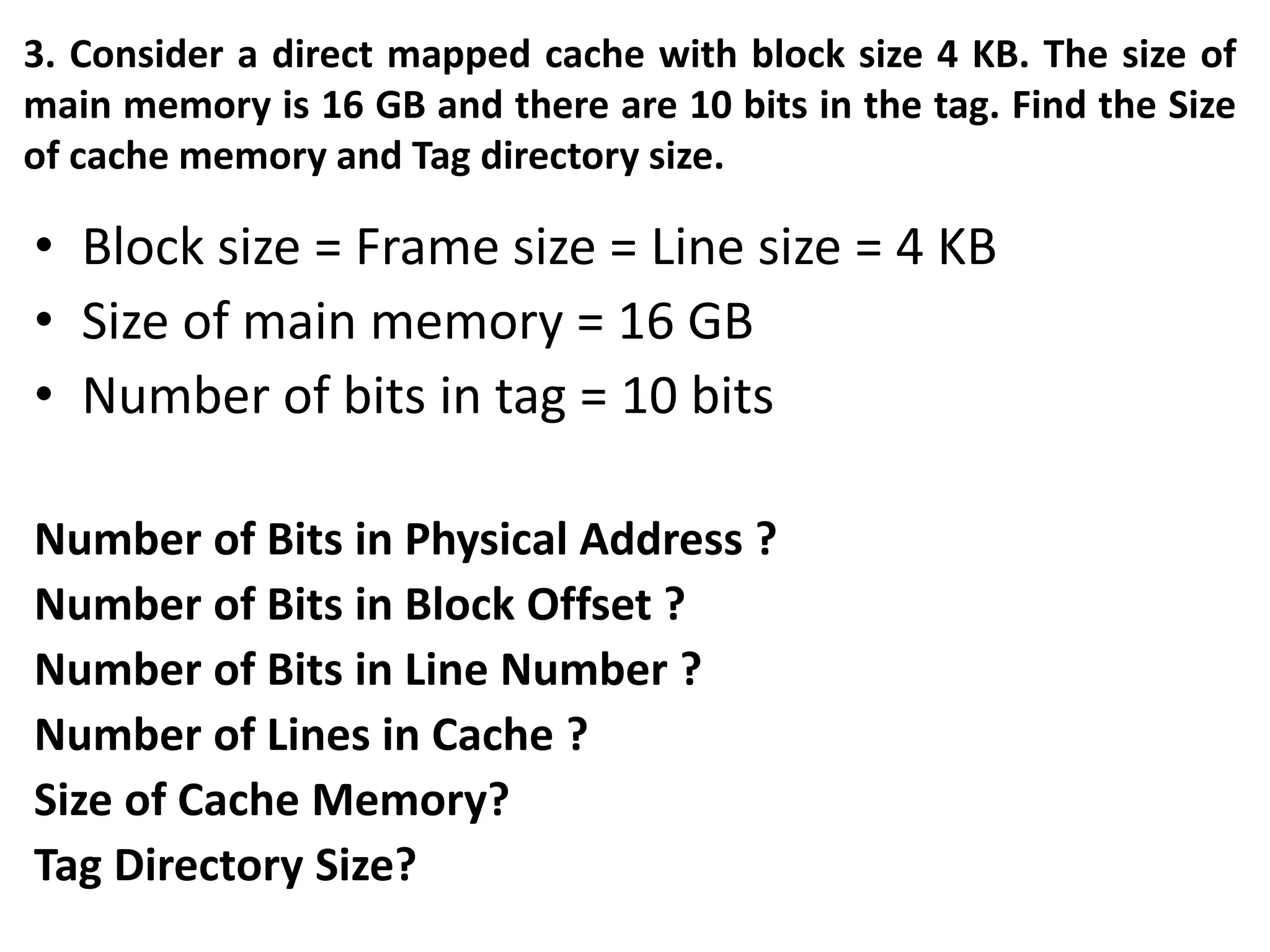

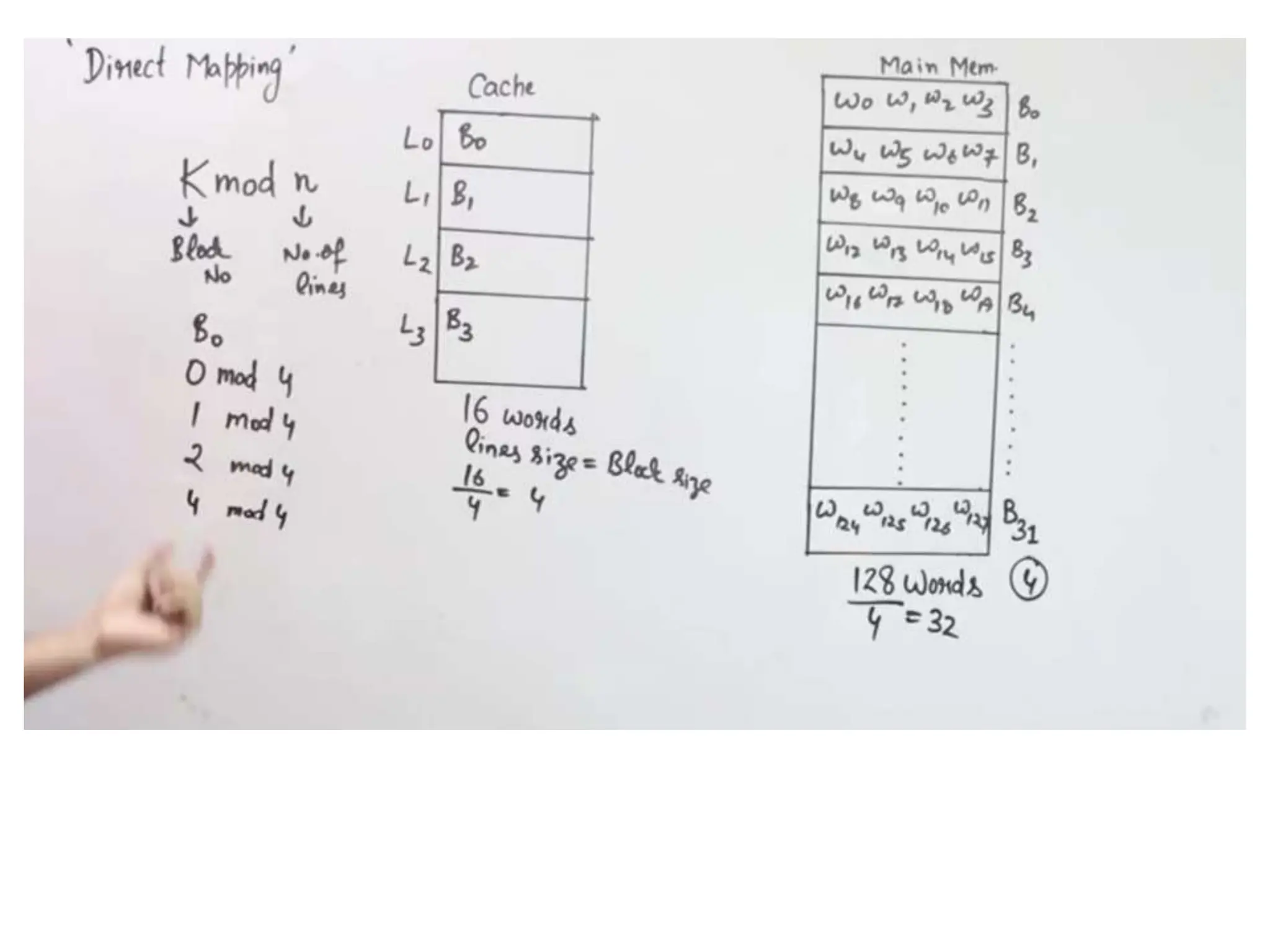

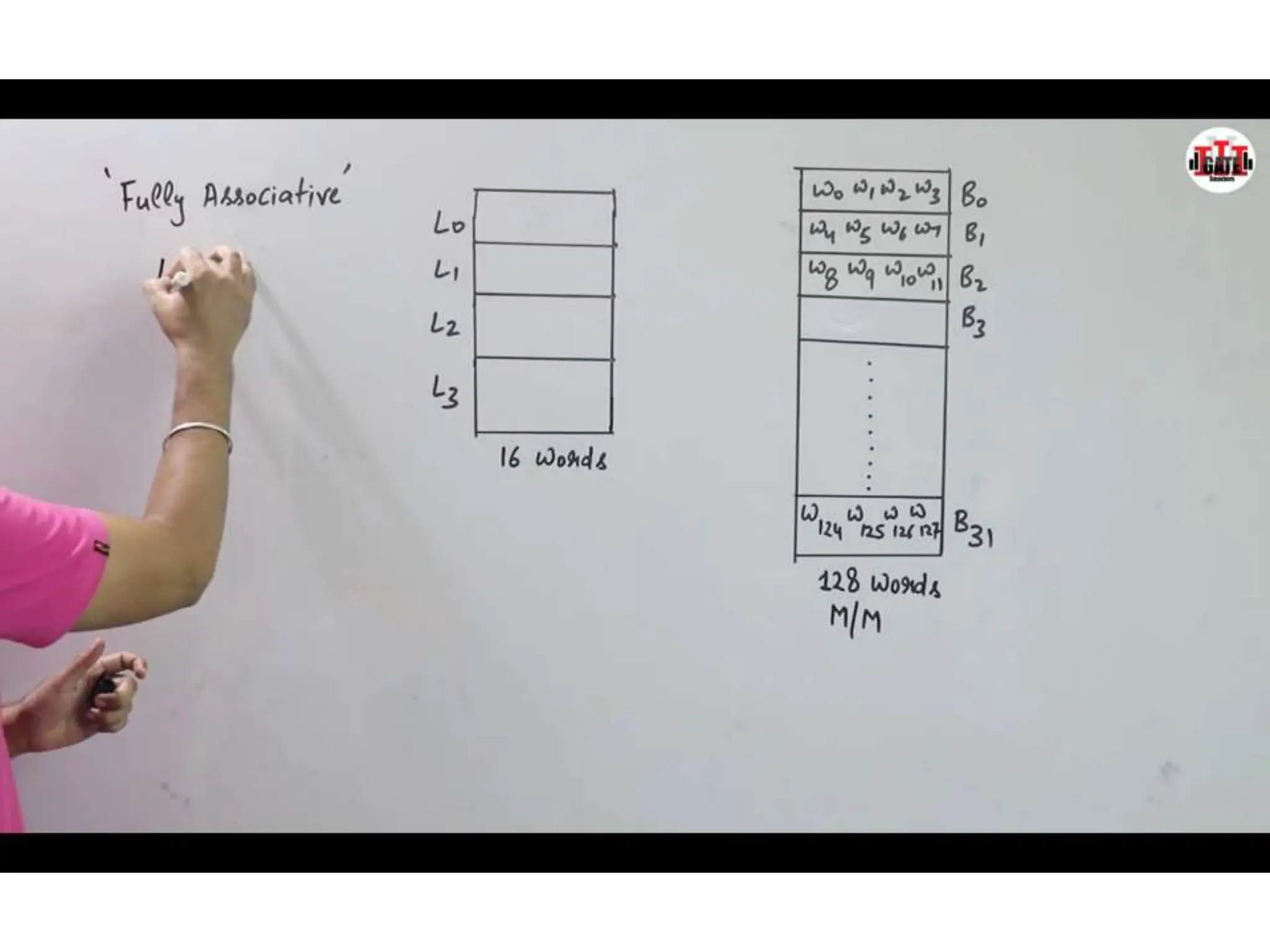

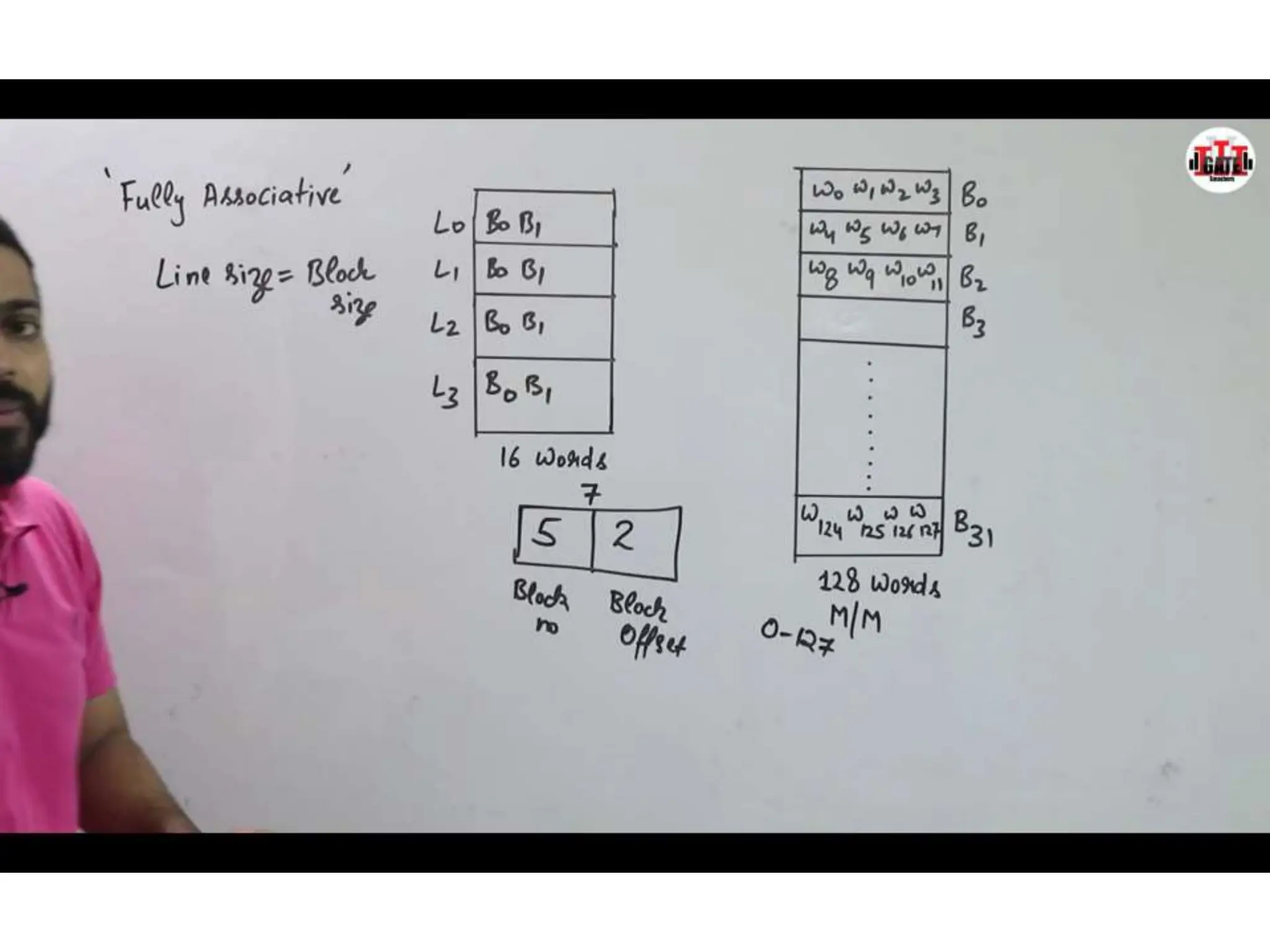

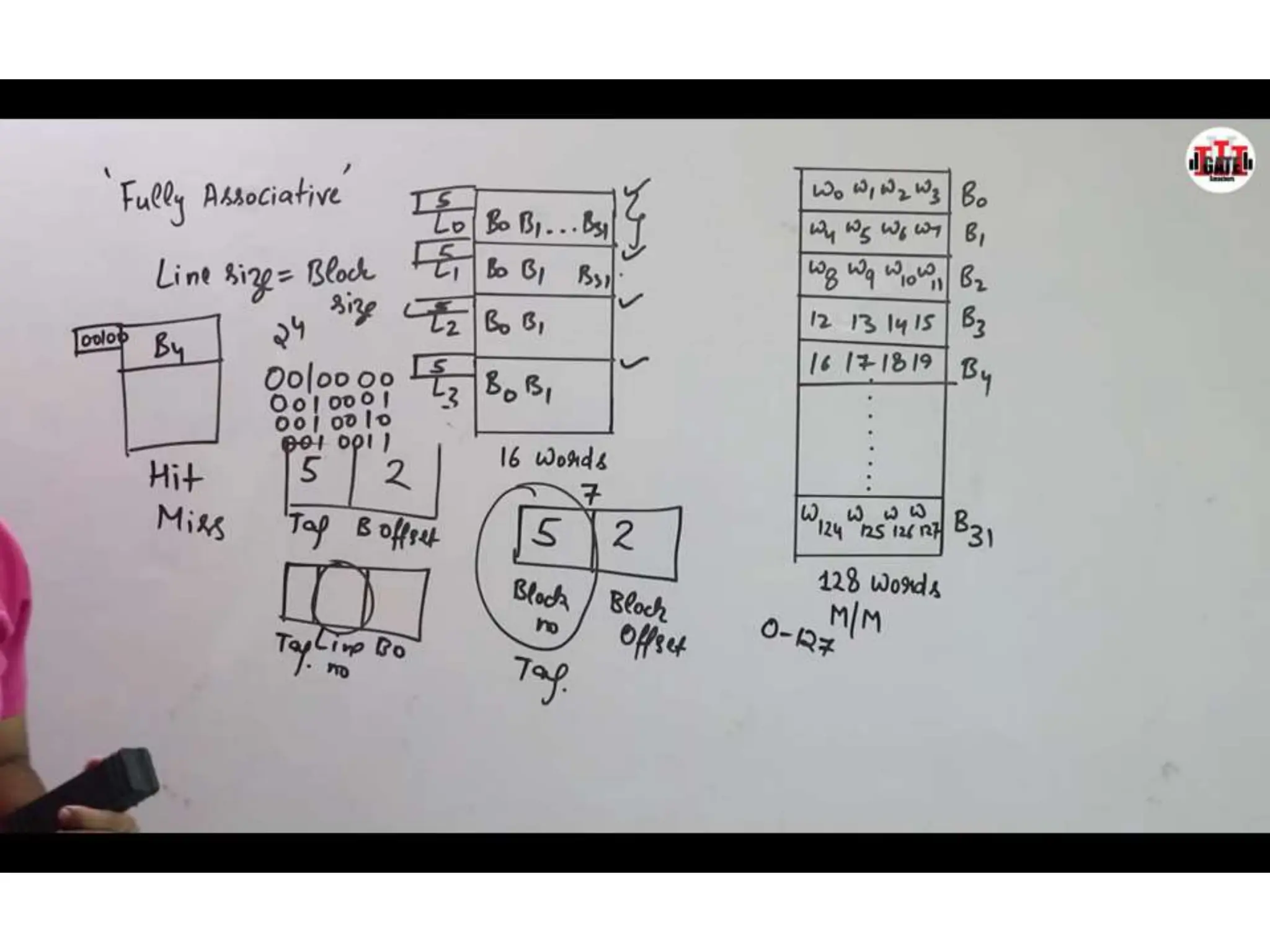

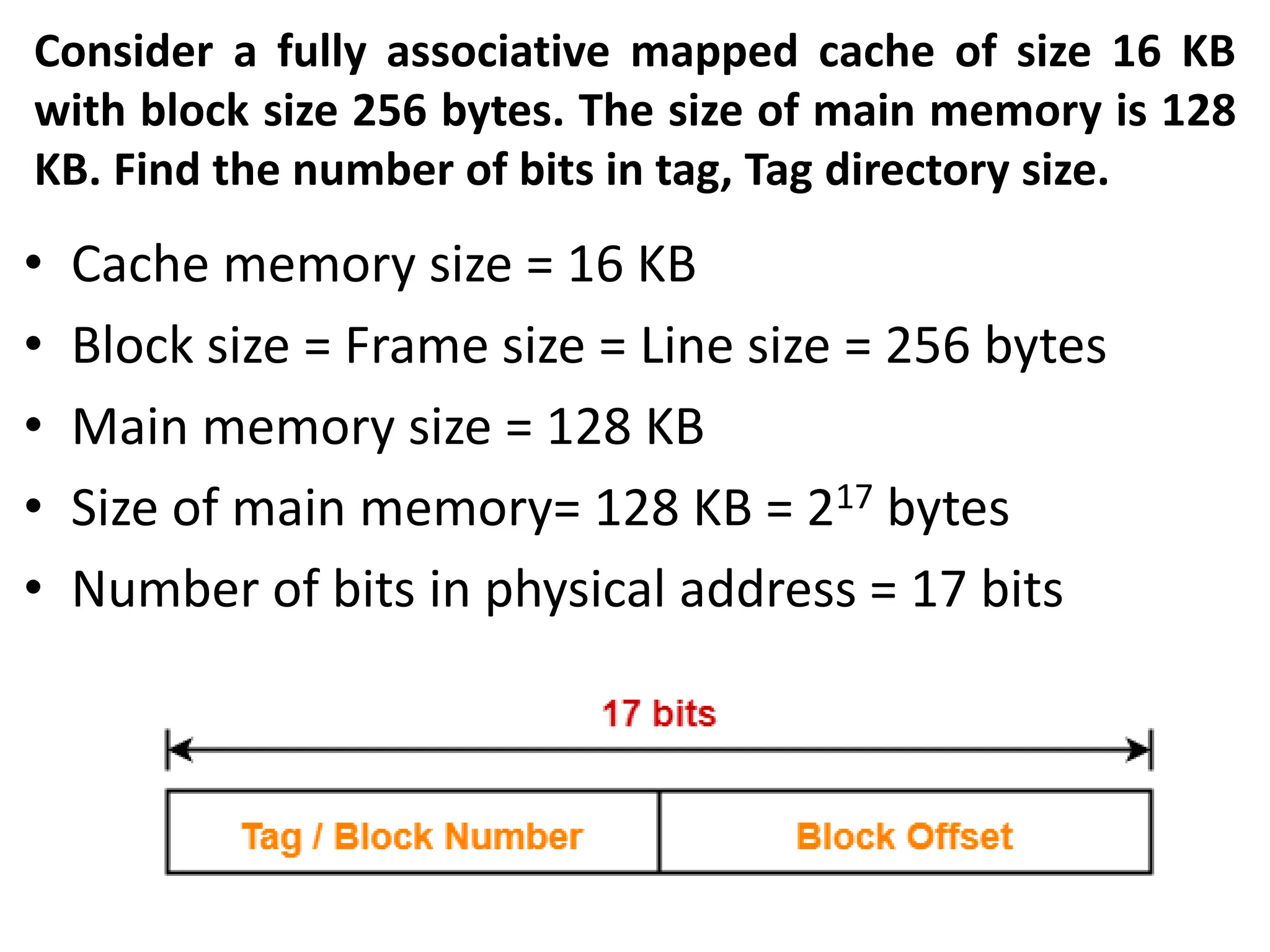

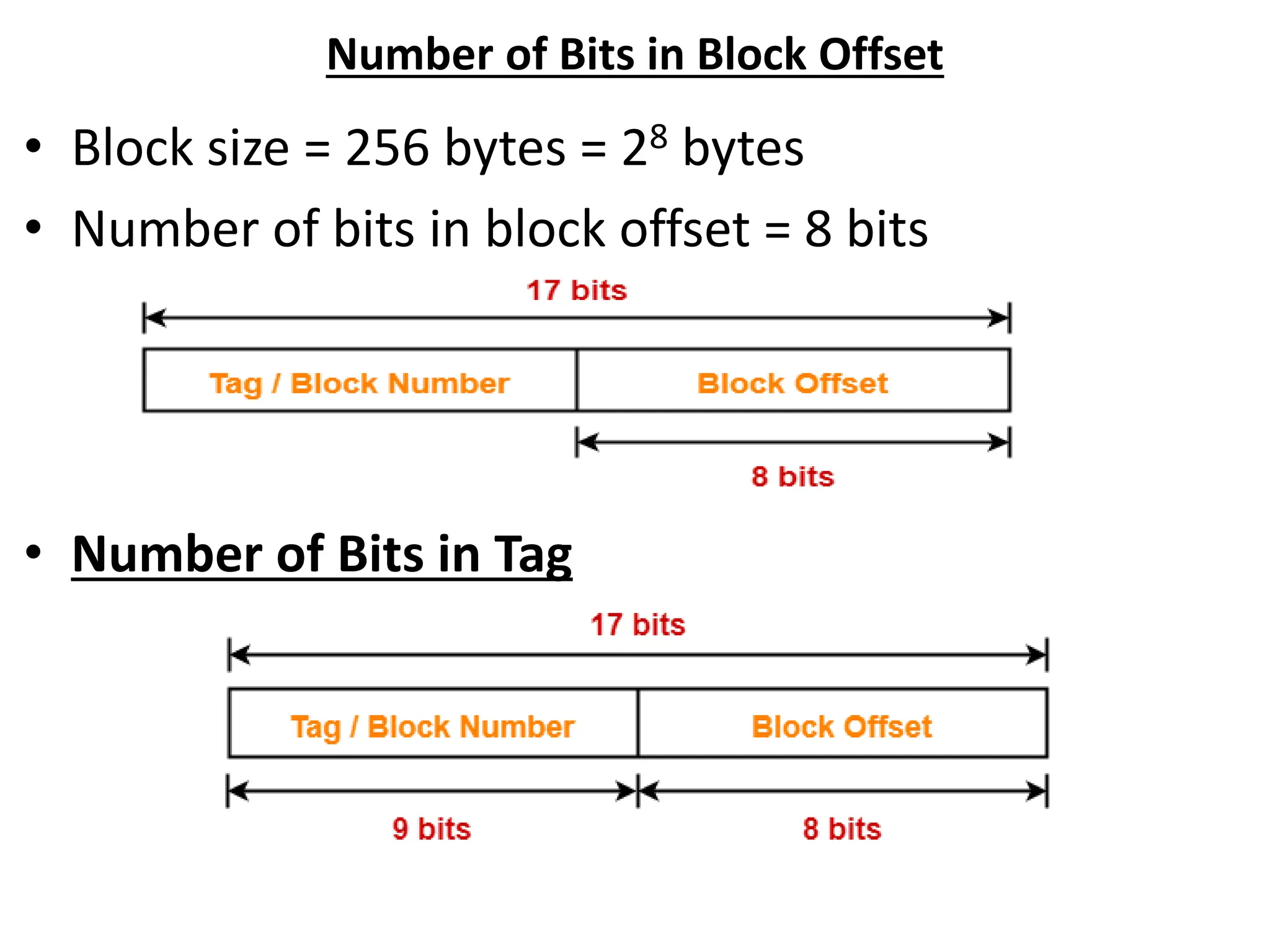

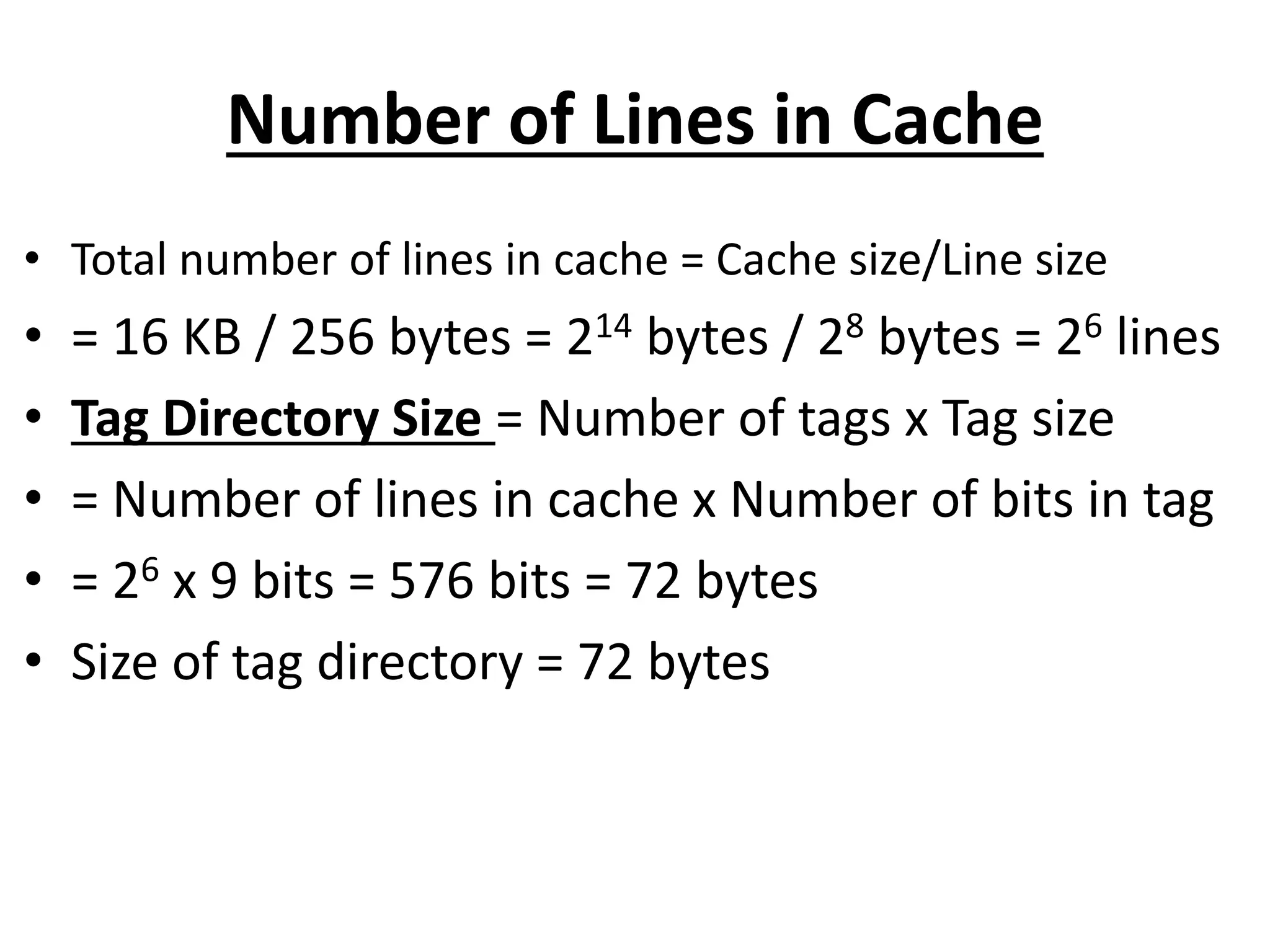

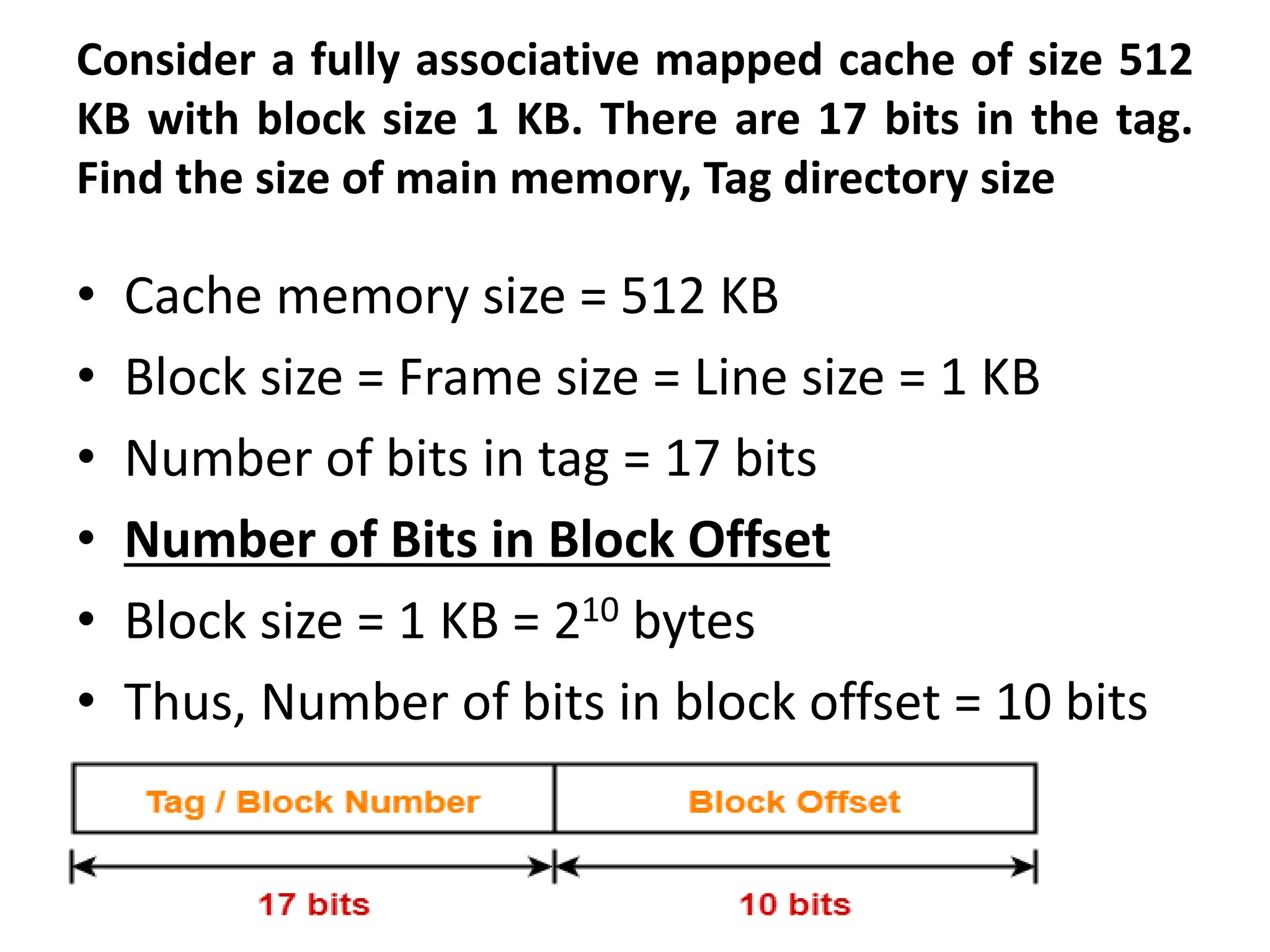

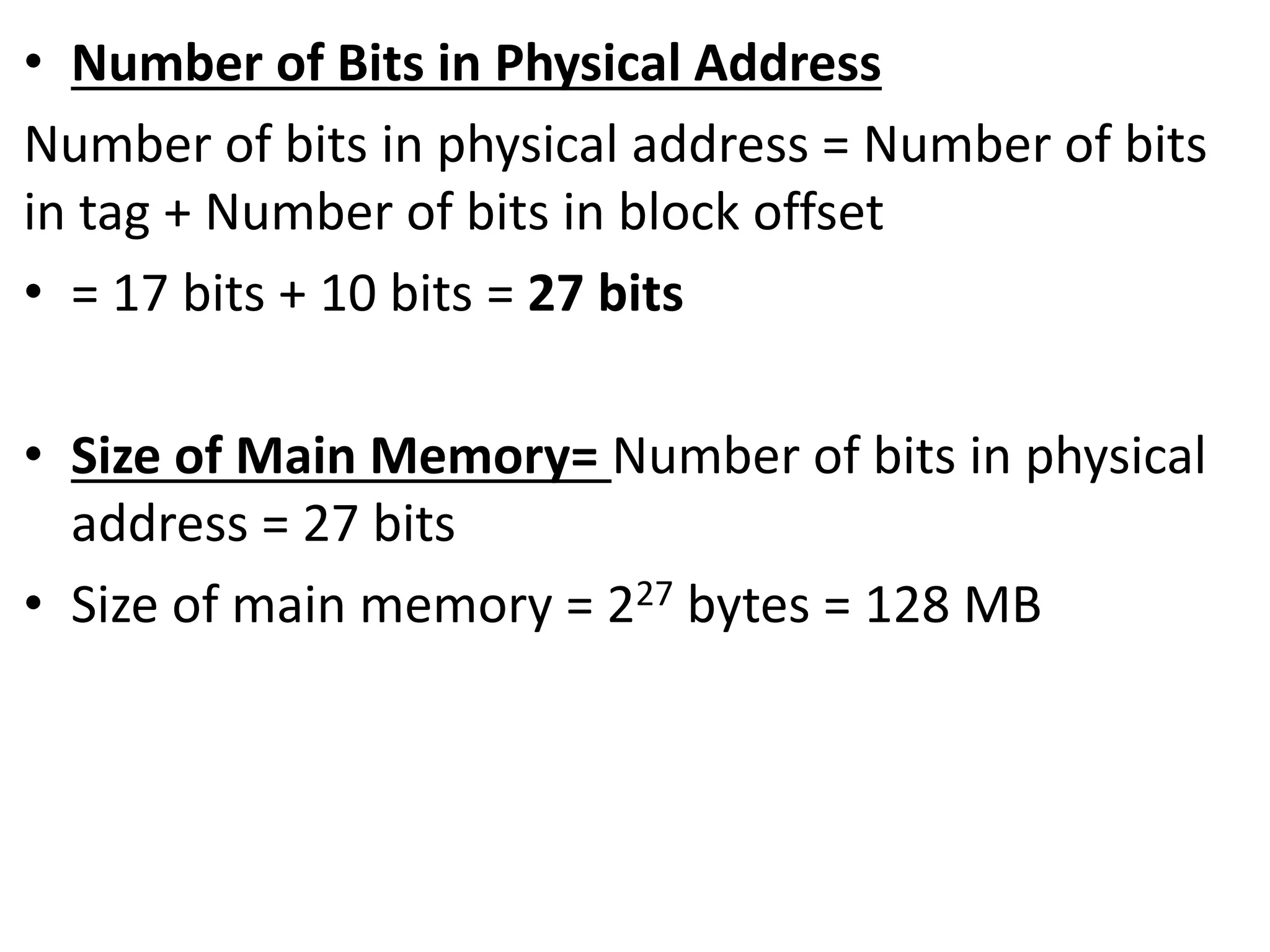

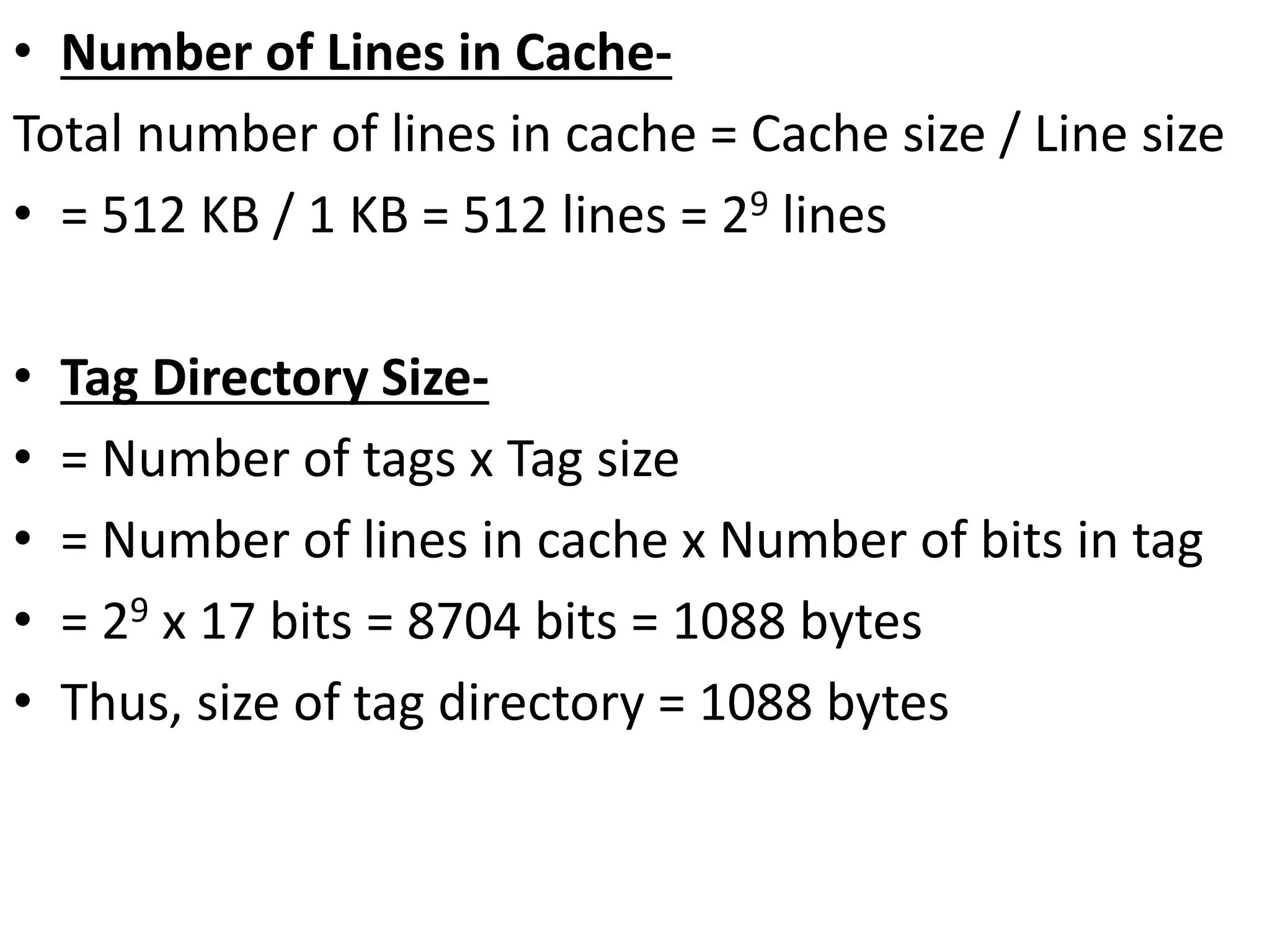

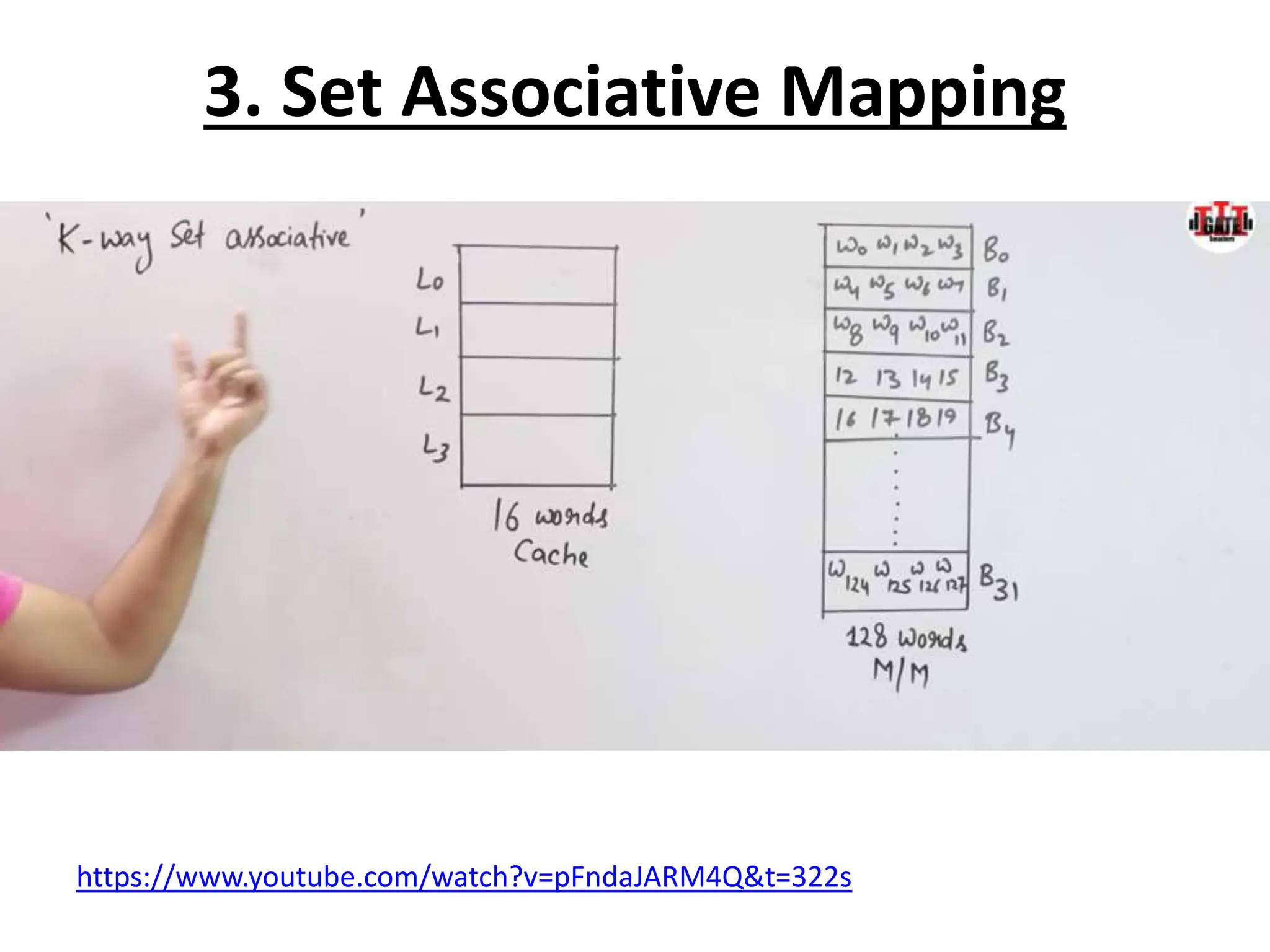

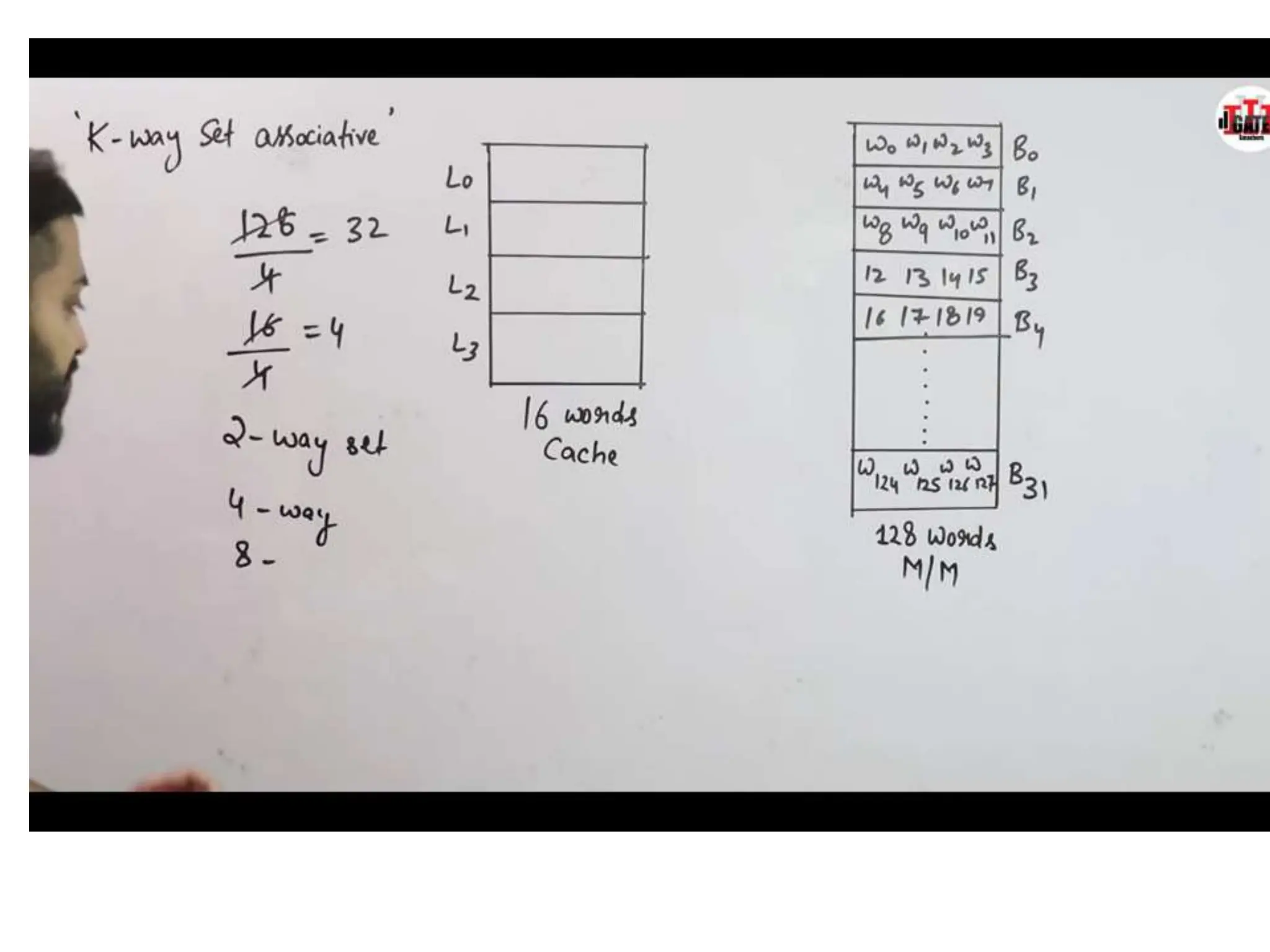

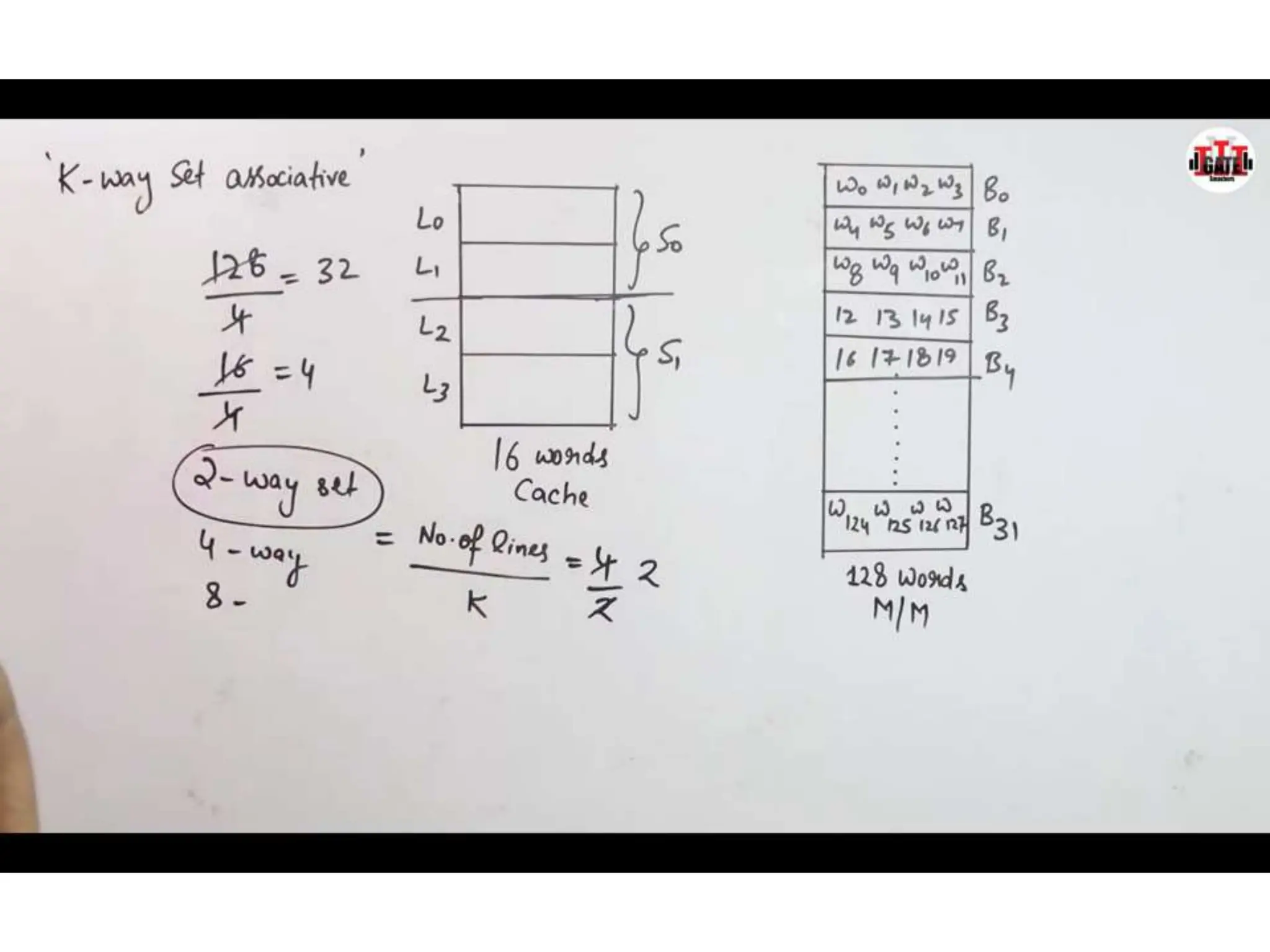

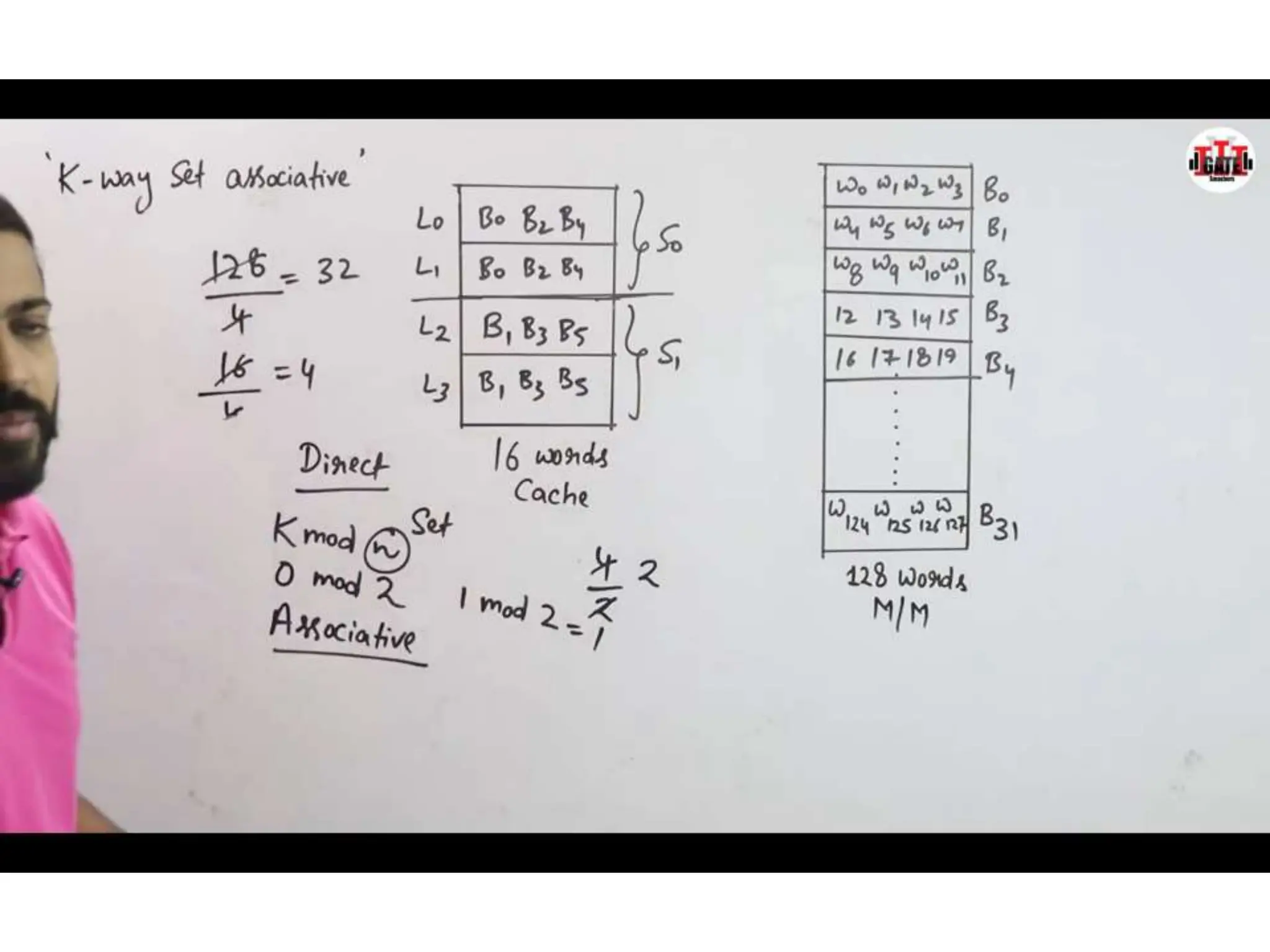

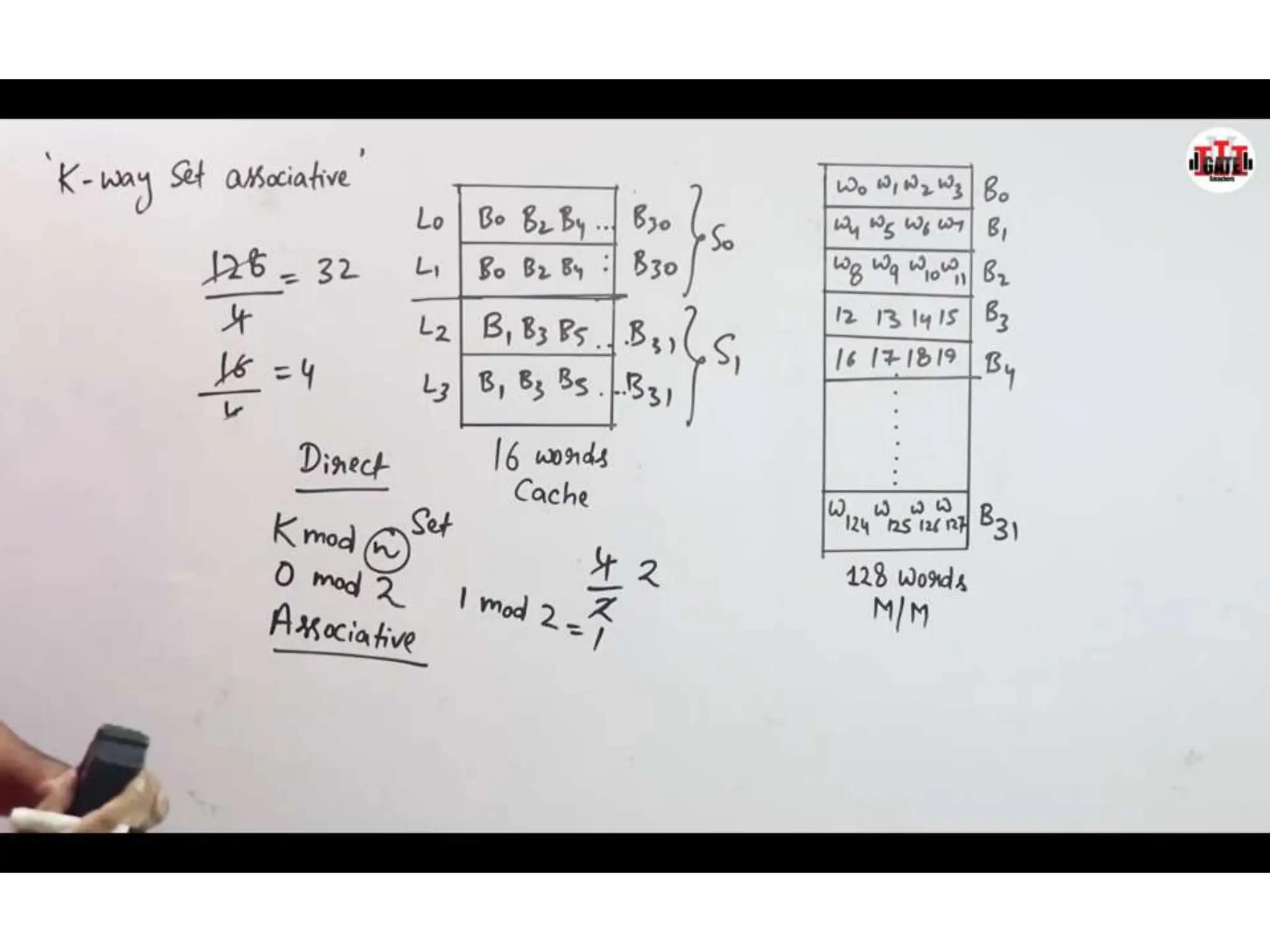

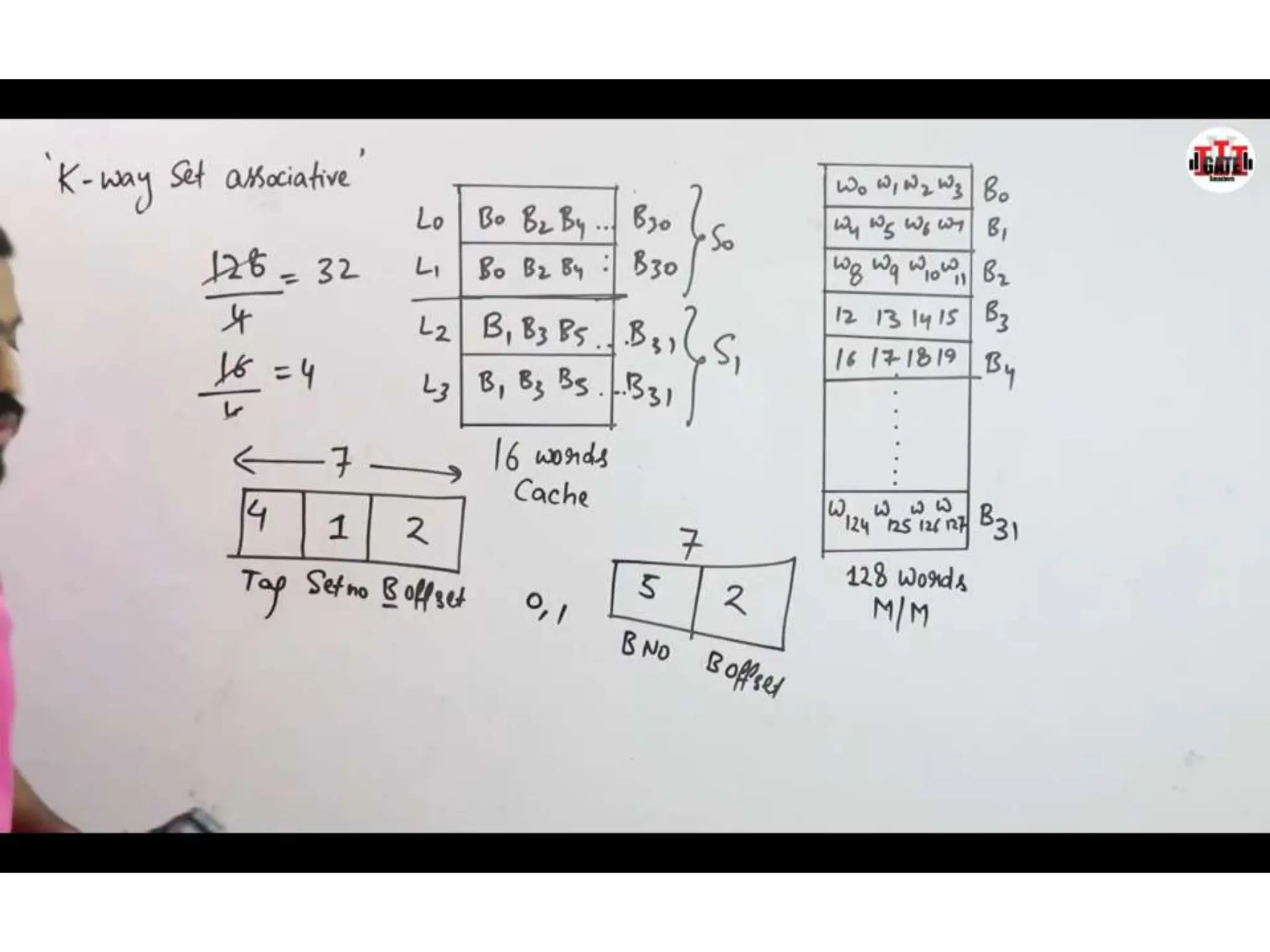

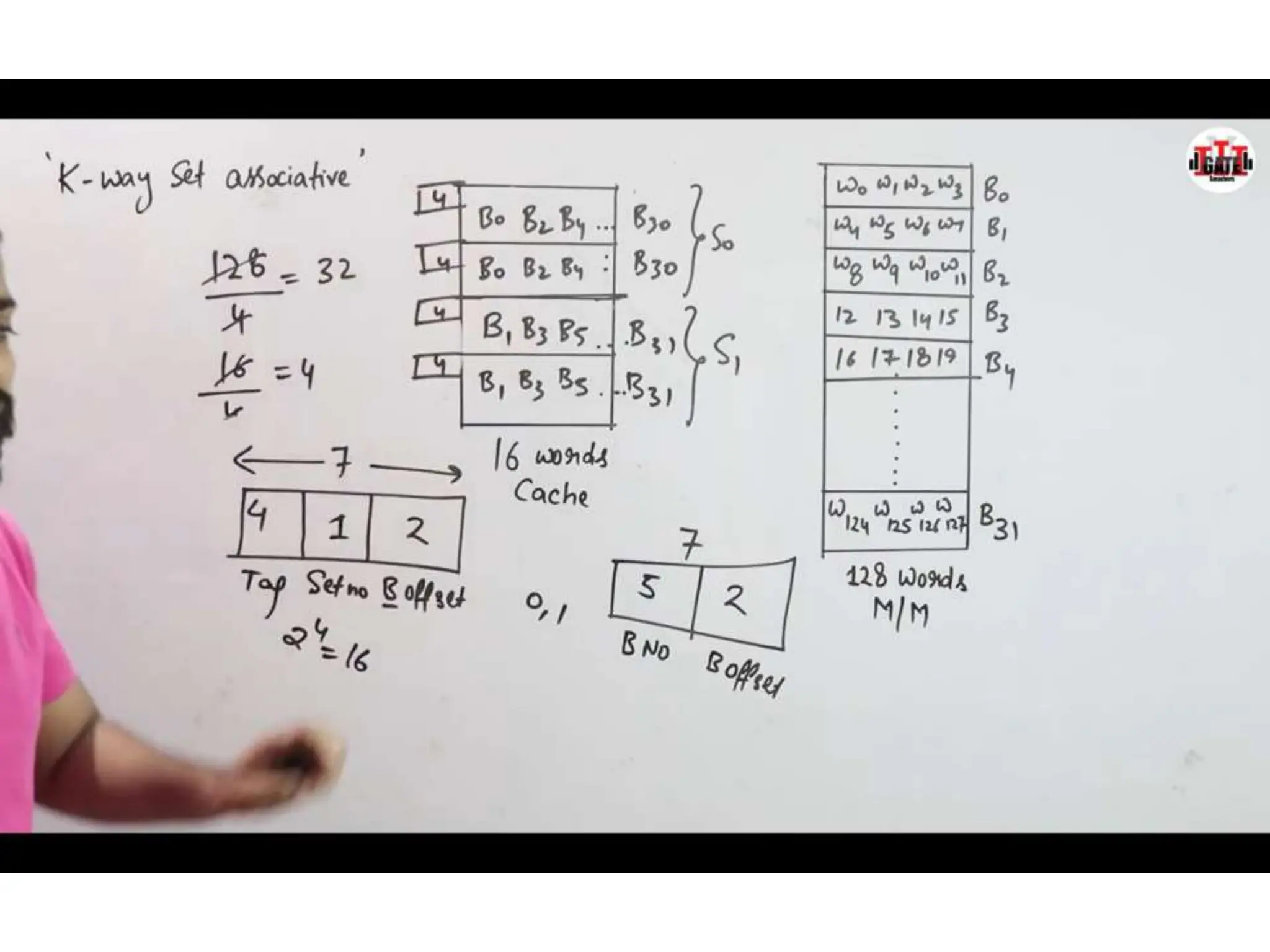

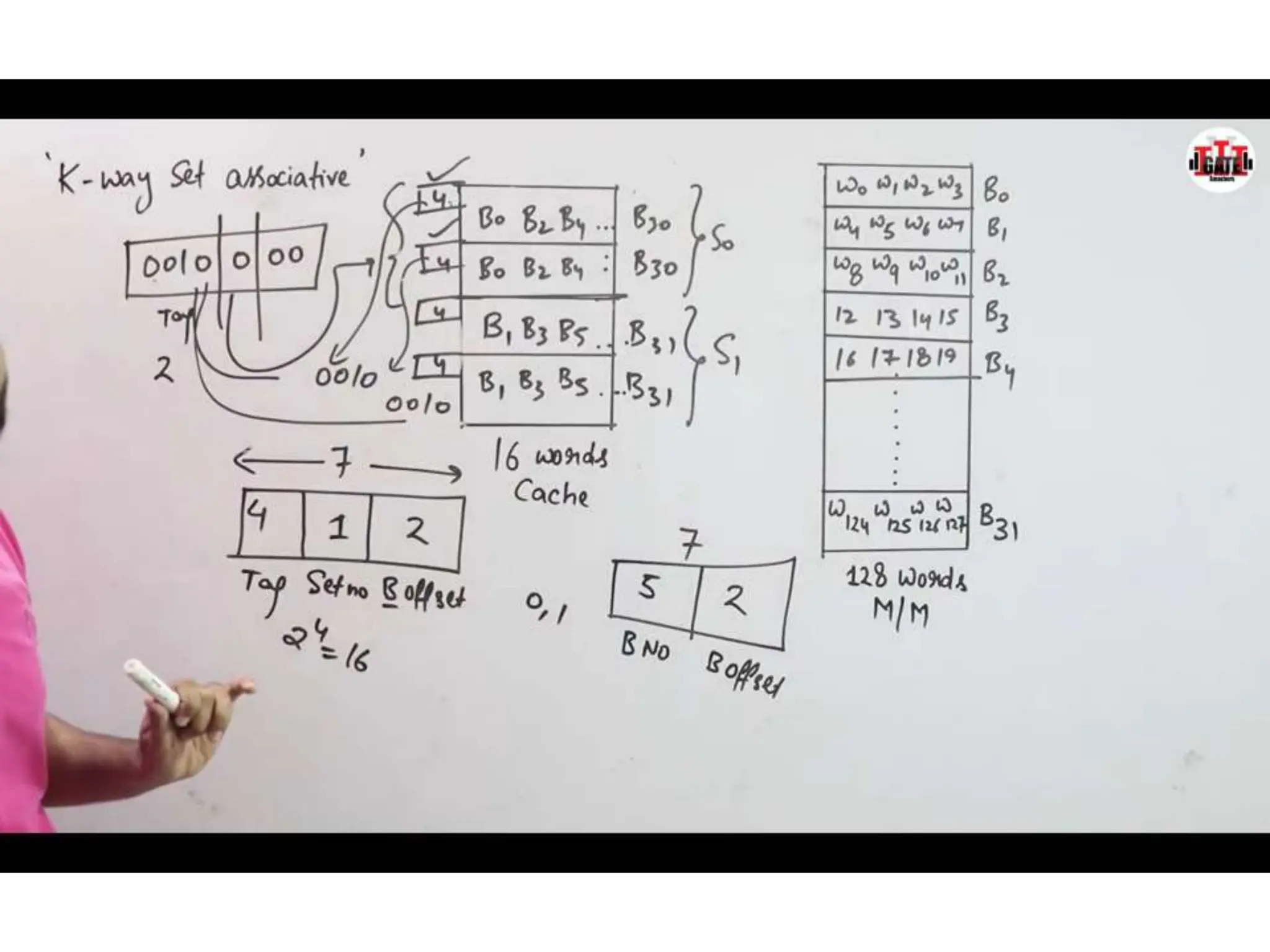

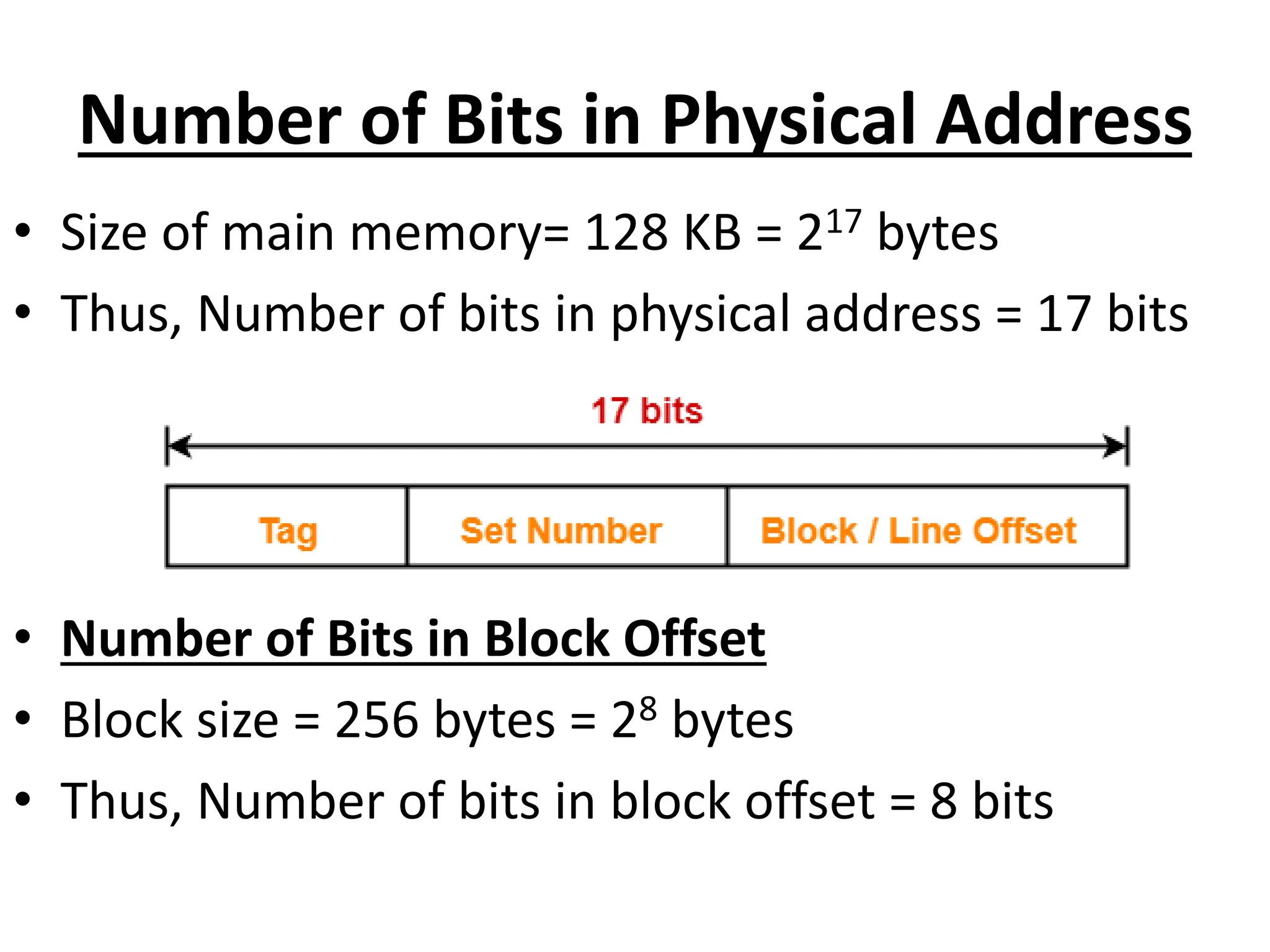

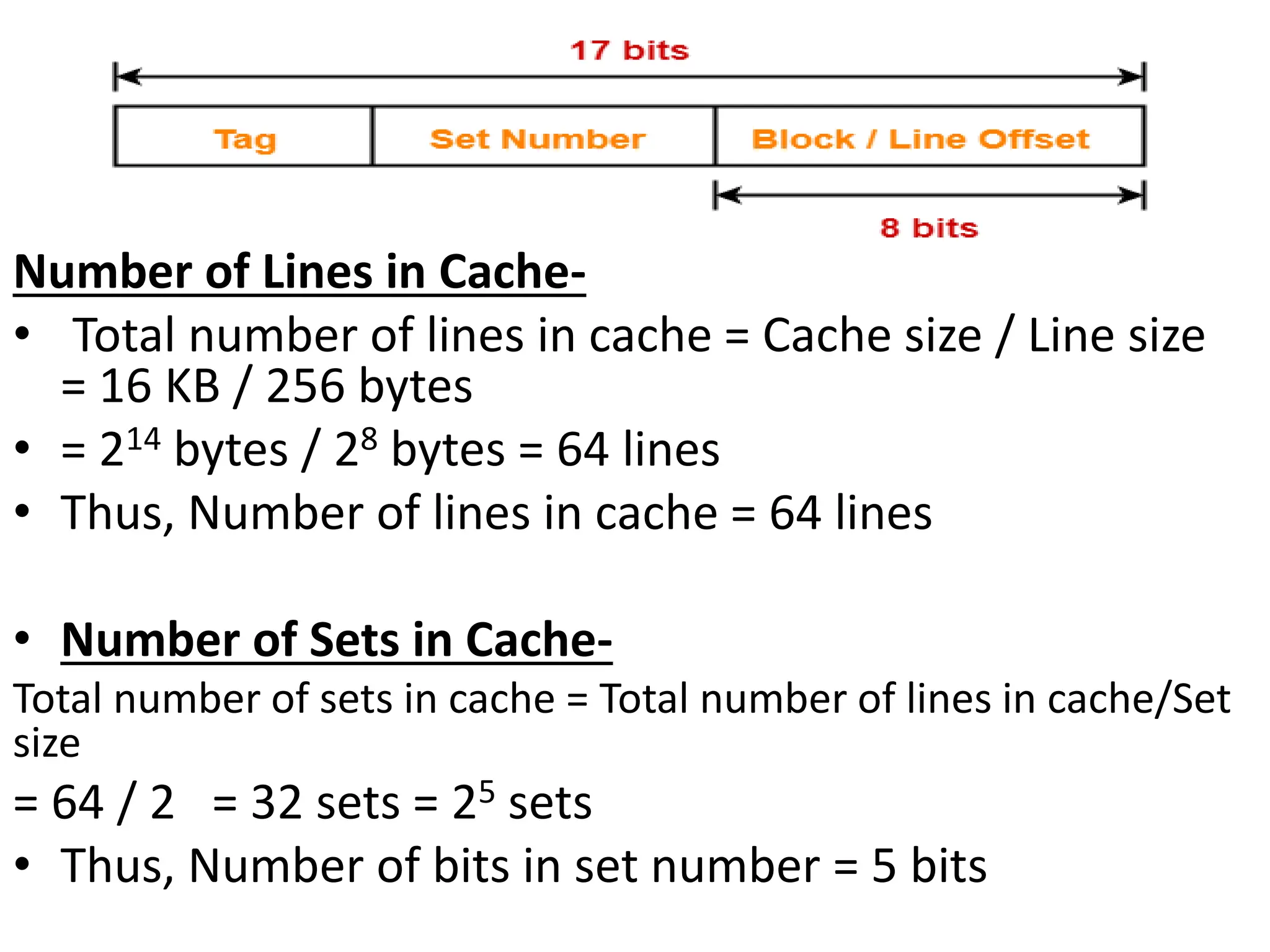

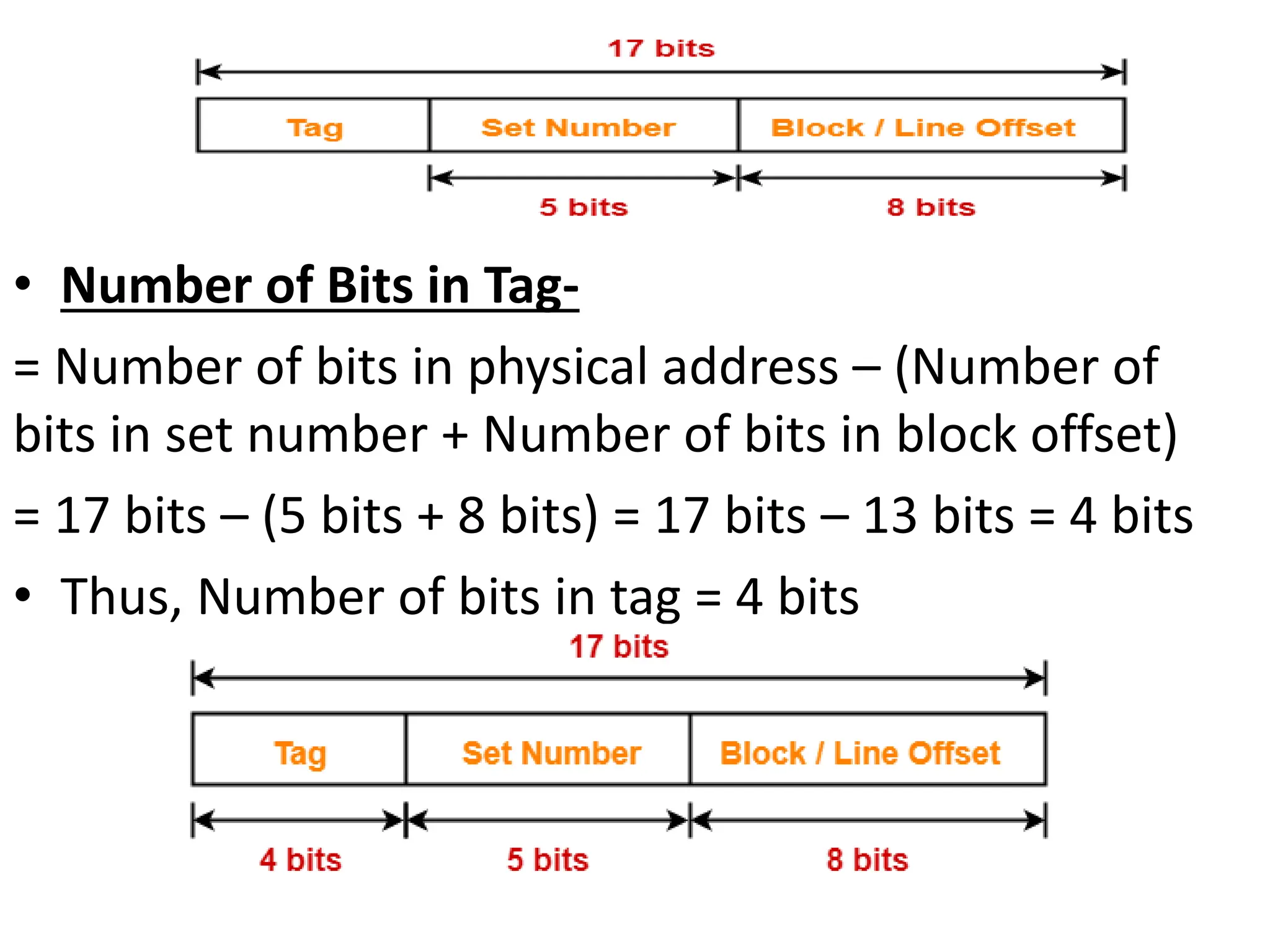

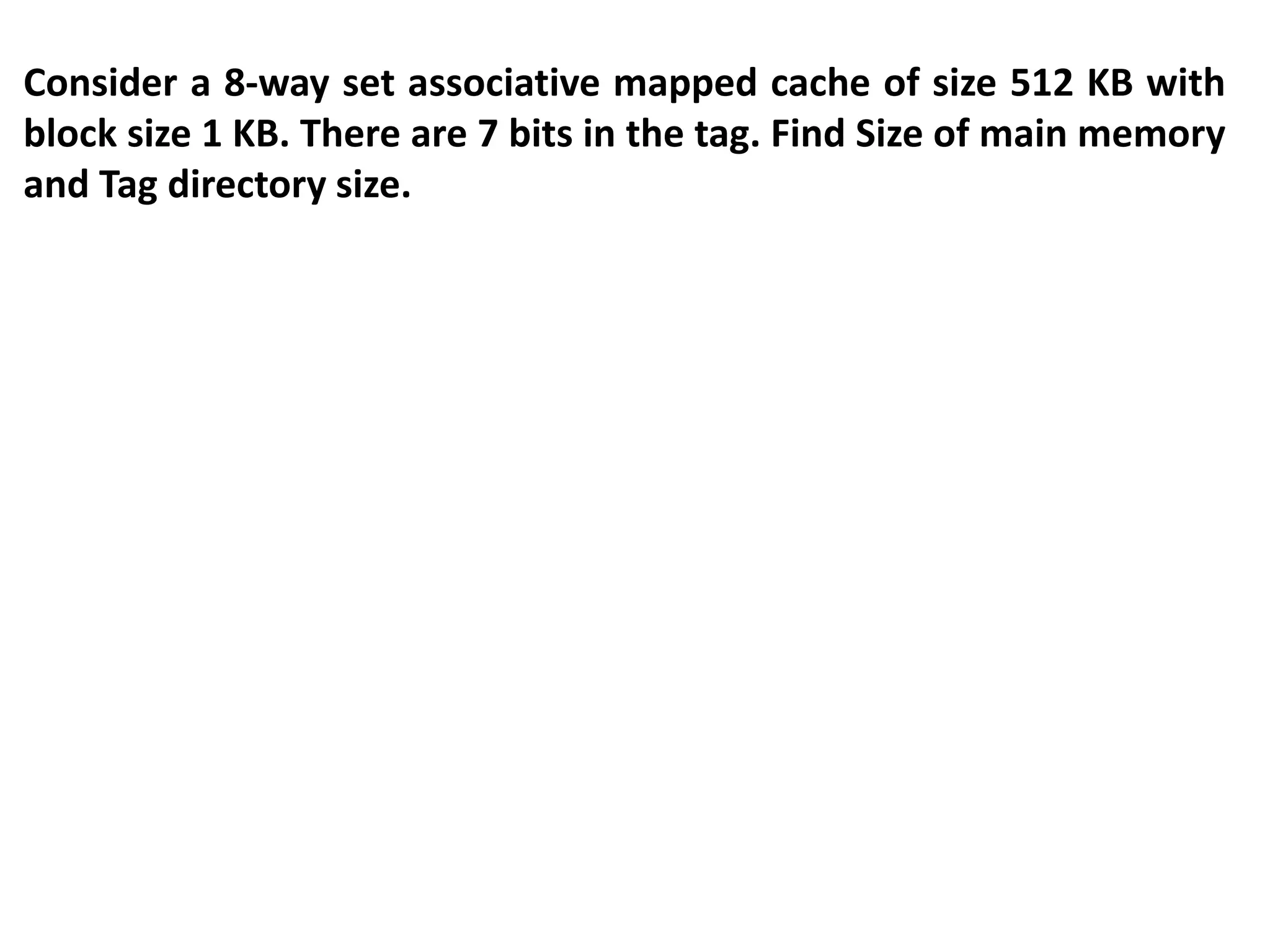

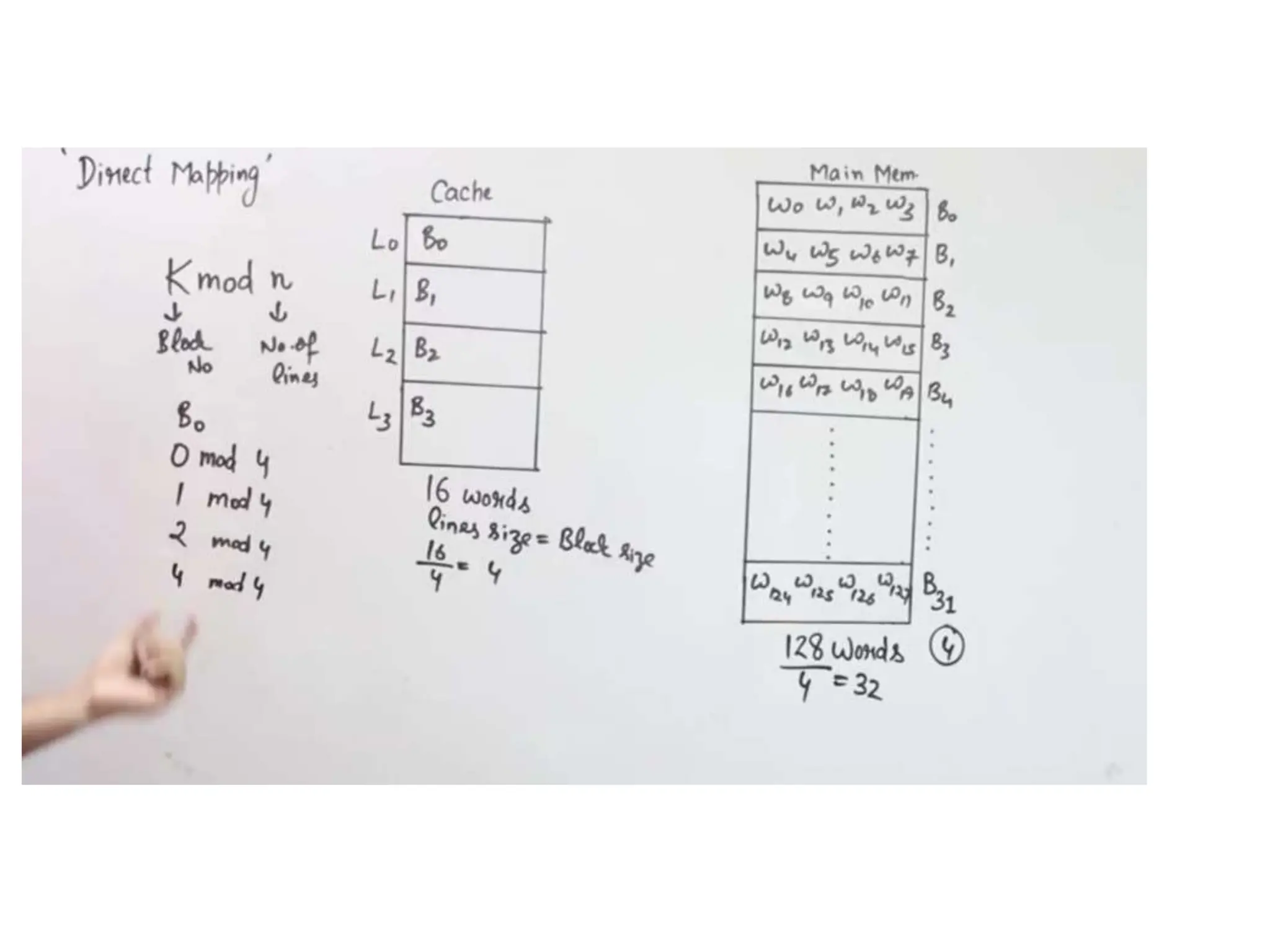

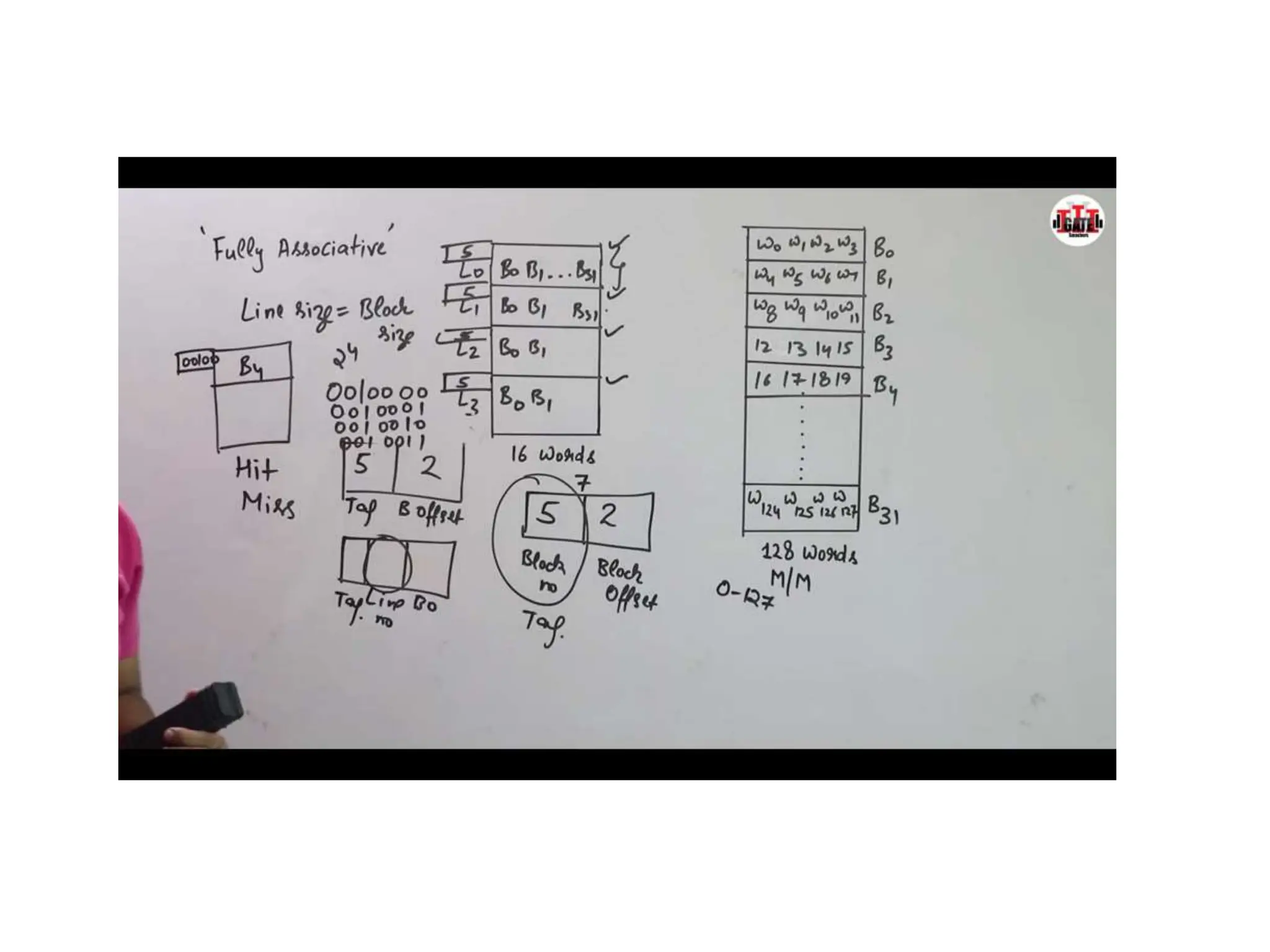

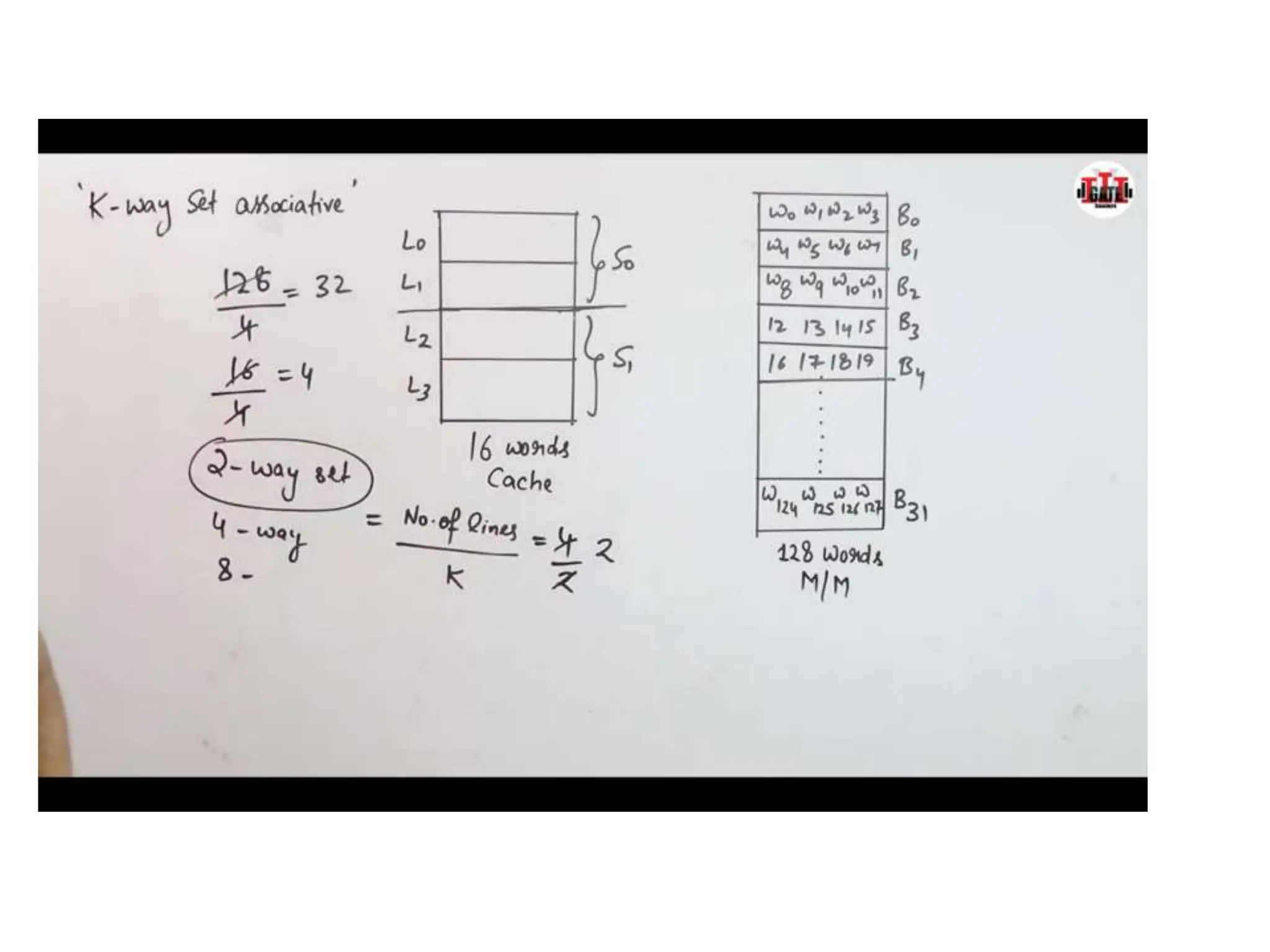

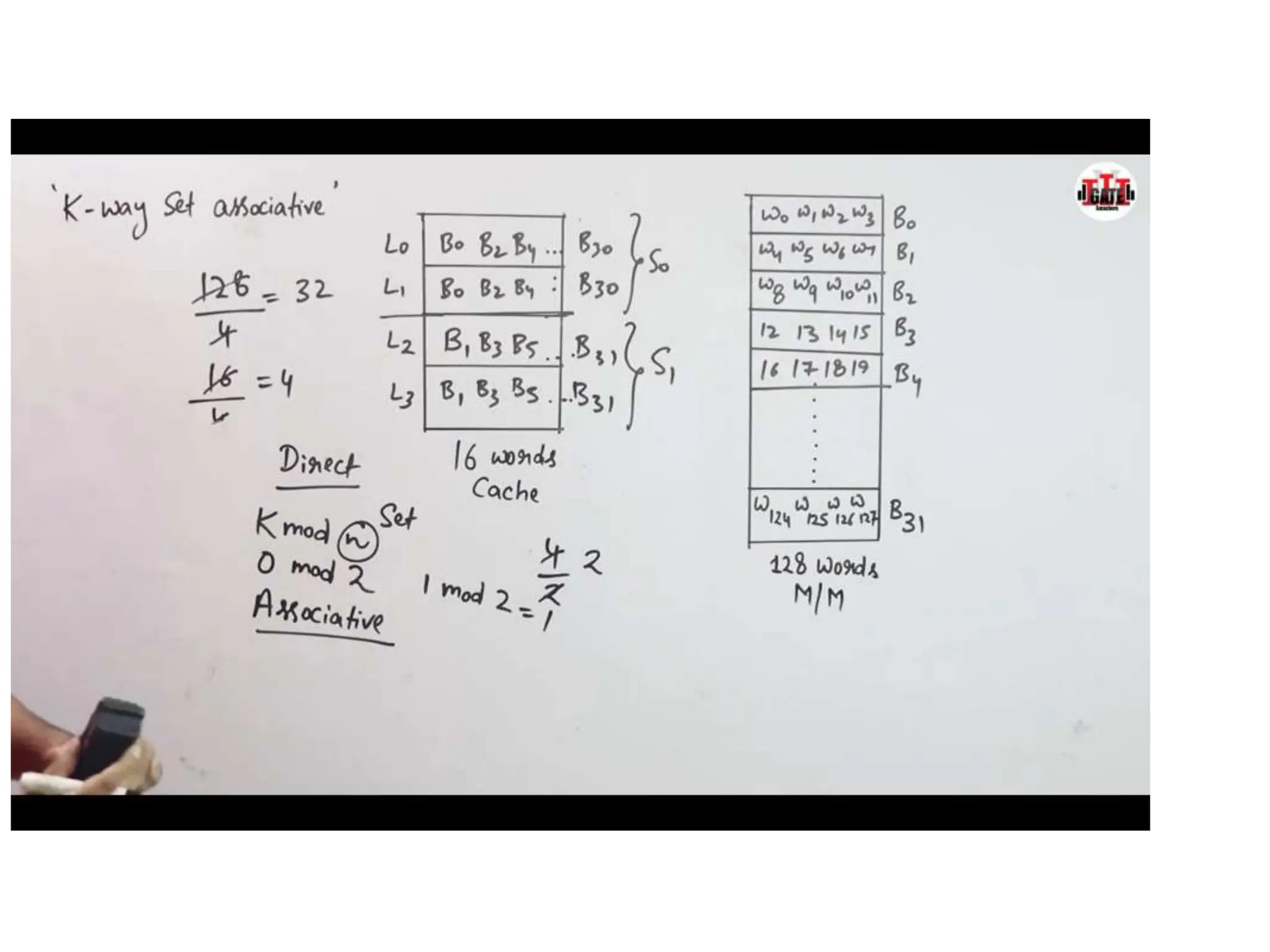

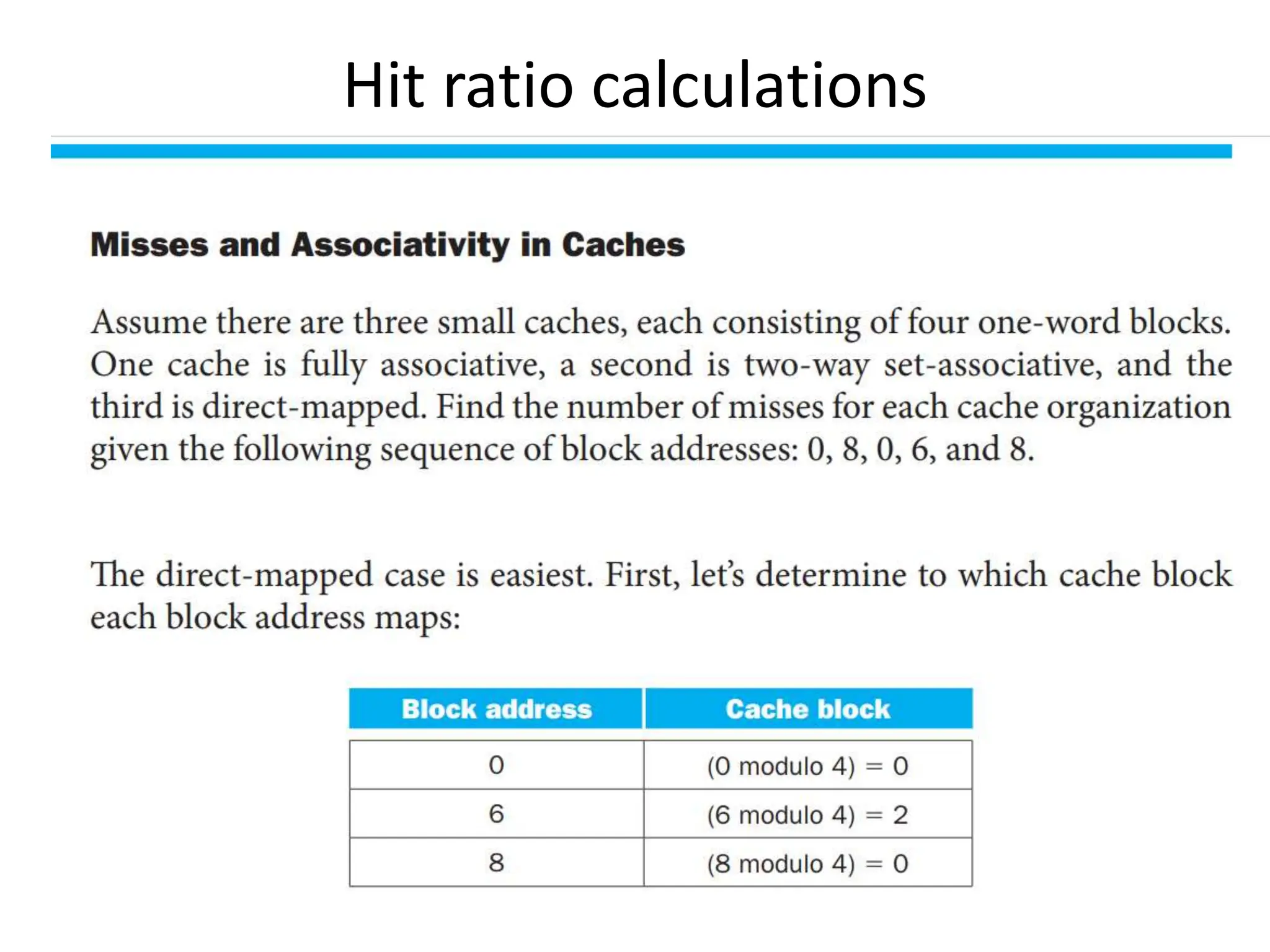

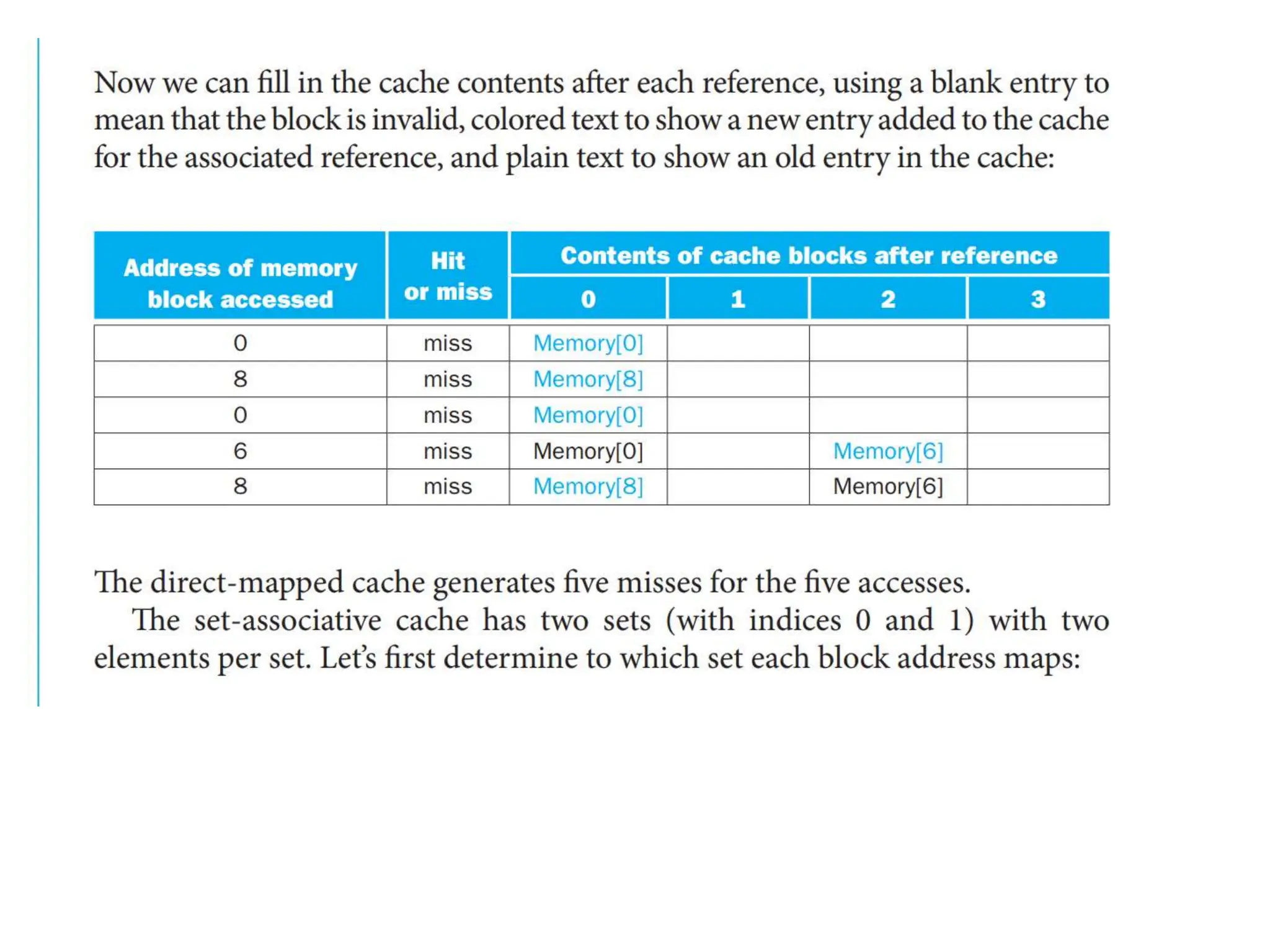

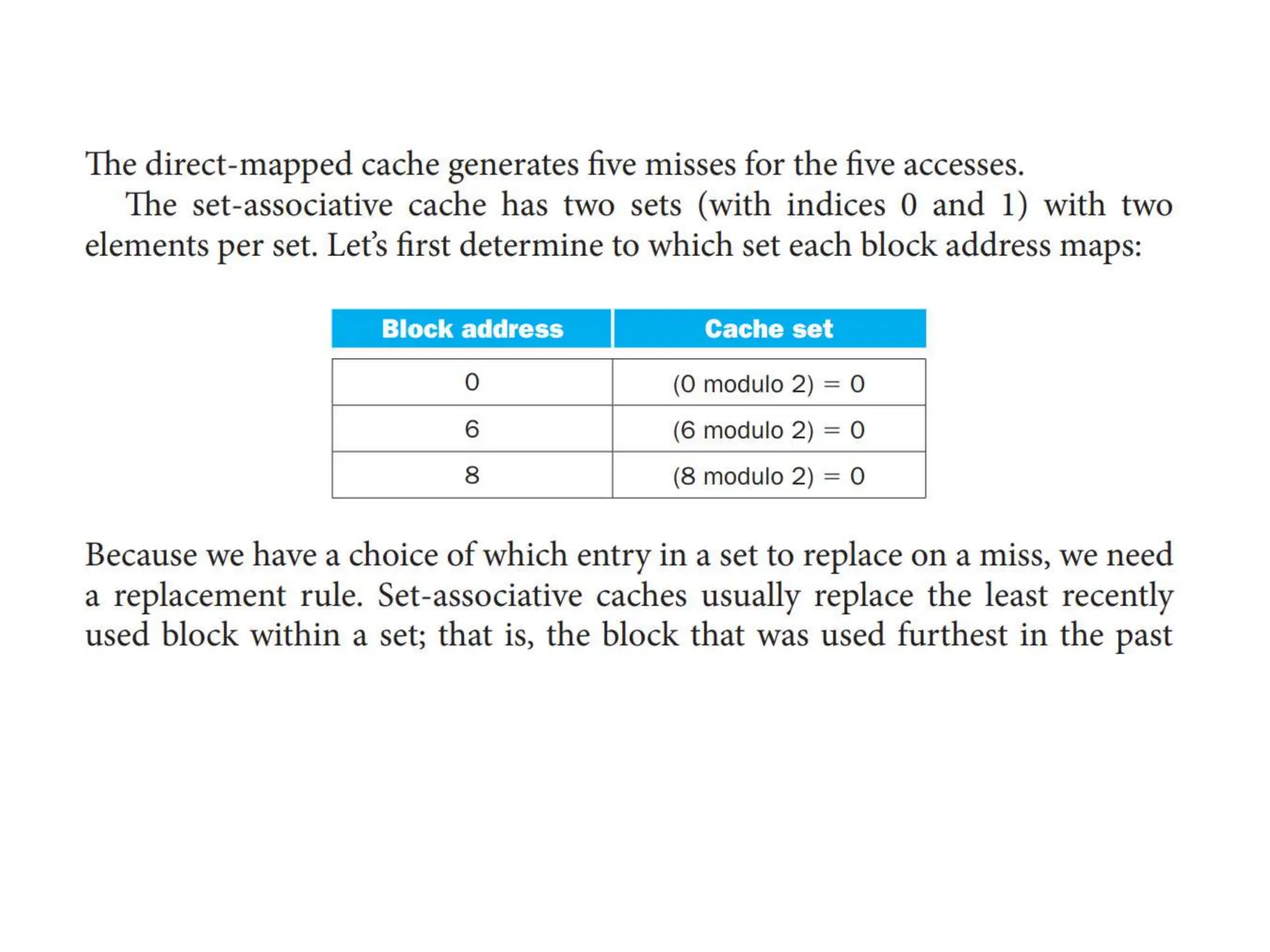

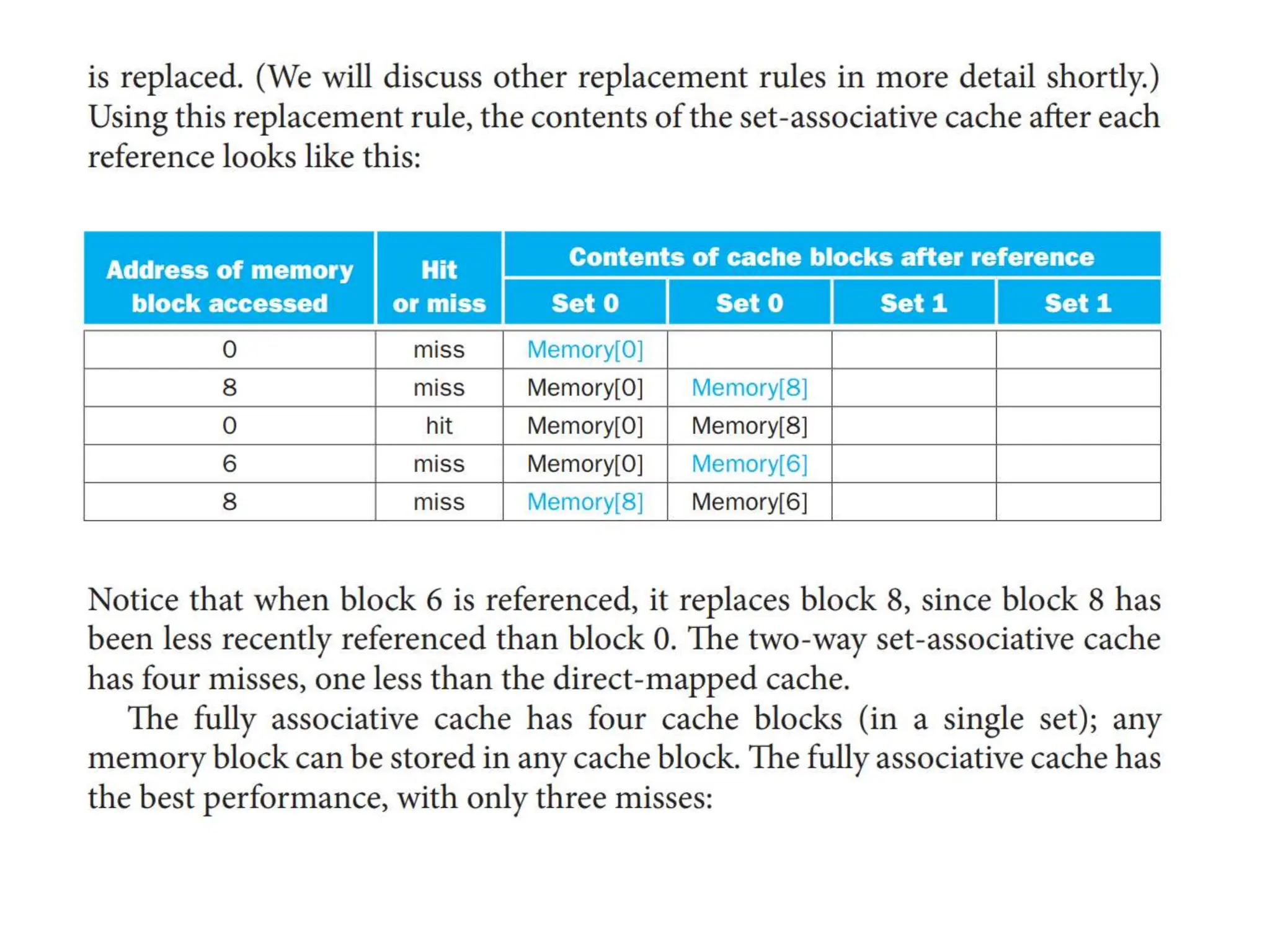

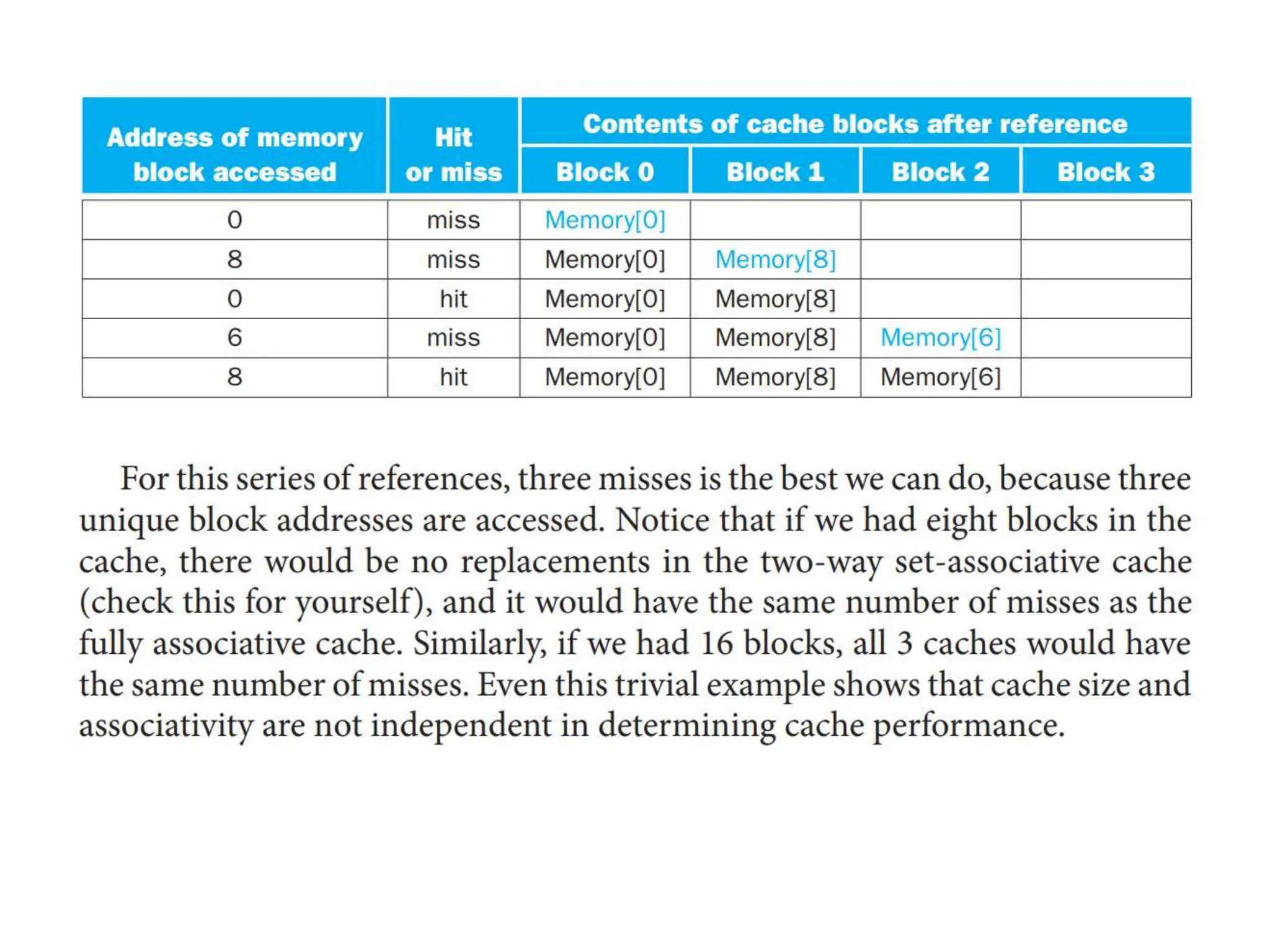

The document provides an overview of memory system organization and architecture, focusing on the hierarchy of memory, types of main memory, and characteristics of cache and virtual memory. It elaborates on main memory types, cache performance metrics including hit/miss ratios, and mapping techniques such as direct, fully associative, and set associative mappings. The text also includes numeric examples related to cache mapping and calculations, illustrating the complexities of memory management in computing systems.