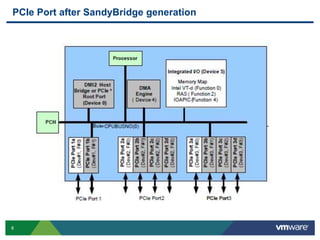

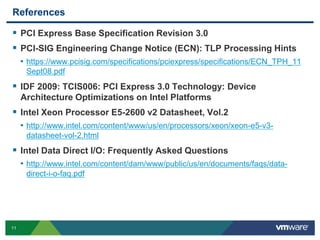

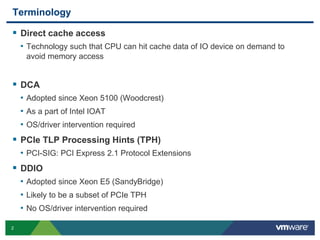

This document discusses techniques for improving CPU access to data from IO devices, including Direct Cache Access (DCA), PCIe Transaction Layer Processing Hints (TPH), and Data Direct I/O (DDIO). DCA allows the CPU to access cache data from IO devices to avoid memory access, but requires driver intervention. PCIe TPH and DDIO aim to prefetch or retain IO write data in the cache without driver involvement. DDIO is specific to Intel platforms and accelerates local socket performance, while DCA does not differentiate sockets. The document provides details on how each technique functions and references further reading.

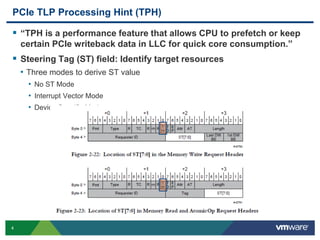

![DCA

Hardware Prefetch on DMA Write

3

• Memory access cannot be avoided

• Need to avoid cache eviction before CPU uses

DCA flag := CPUID(EAX:1):ECX[18]

• Require driver’s intervention

TLP format for DCA

82599 datasheet: Fig.7.29

82599 datasheet: Fig.7.30 Available for multiple sockets](https://image.slidesharecdn.com/directcacheaccess-141206083044-conversion-gate01/85/Revisit-DCA-PCIe-TPH-and-DDIO-3-320.jpg)