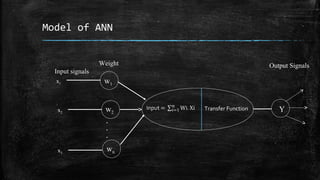

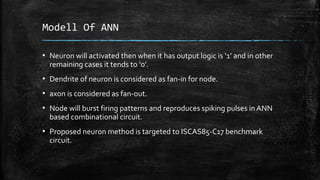

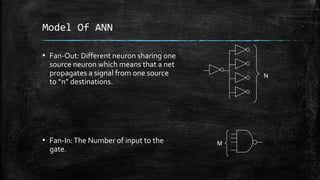

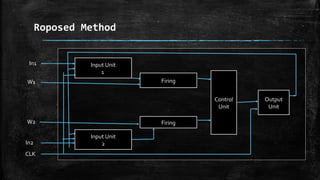

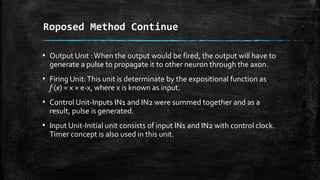

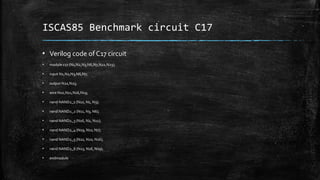

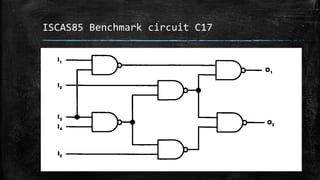

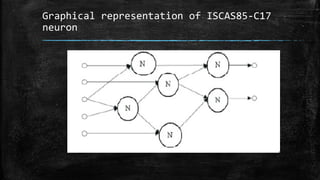

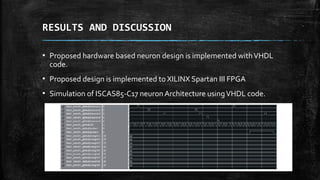

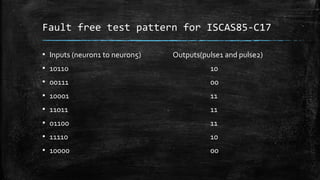

This document describes a proposed method for implementing neural network-based circuits for VLSI testing using an artificial neural network (ANN) model. The method uses a neuron design with input, firing control, and output units to test the ISCAS85 C17 benchmark combinational circuit. Simulation results showed the ANN-based neuron architecture could correctly detect faults and generate the expected output pulses for different input patterns applied to the C17 circuit. The proposed approach aims to allow interconnecting more artificial neurons to create a complete neural network for VLSI design testing.