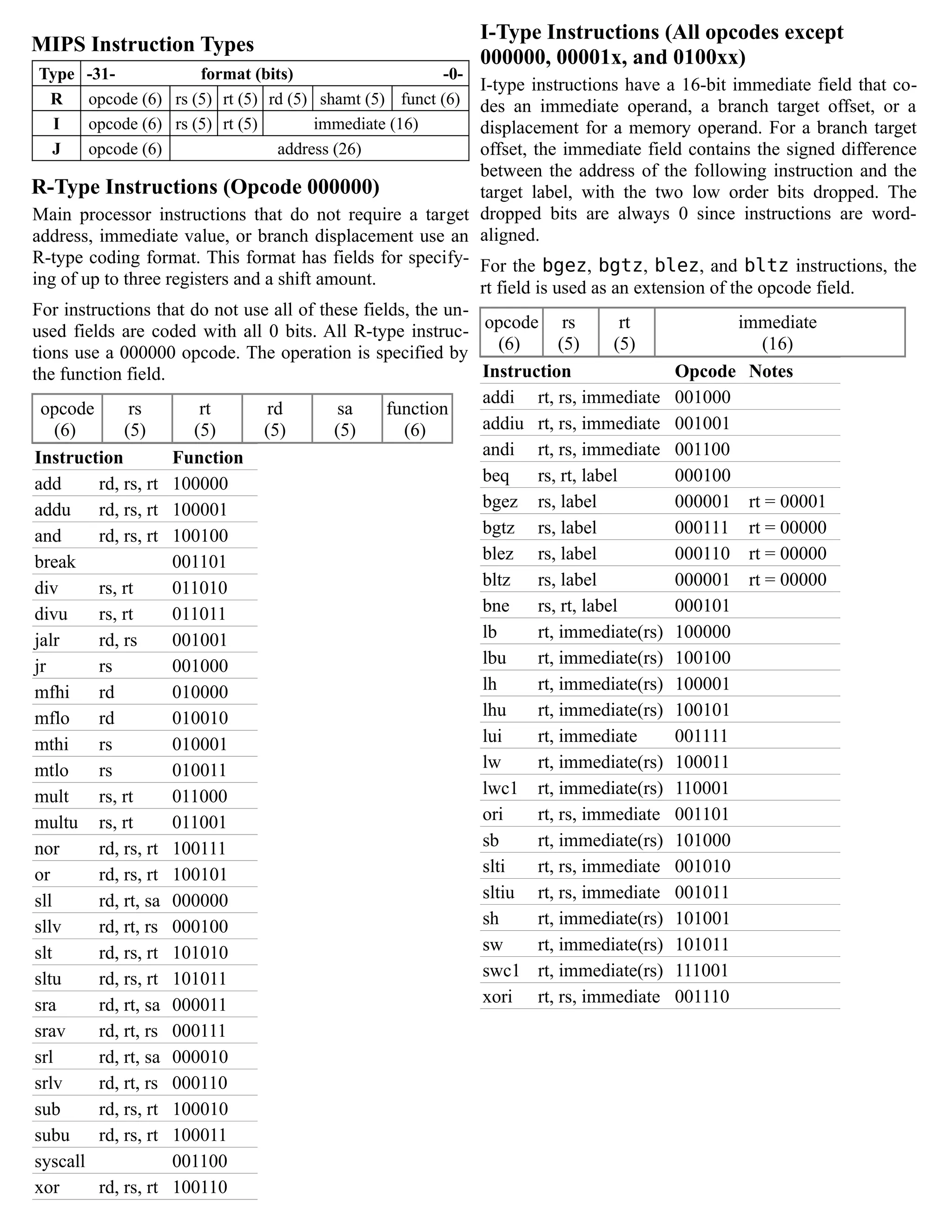

R-type instructions use an opcode of 000000 and specify registers and operations in various fields. I-type instructions use other opcodes and specify an immediate value or address offset. J-type instructions are jumps that provide a 26-bit target address. Coprocessor instructions use an 0100xx opcode and specify floating point operations and registers.