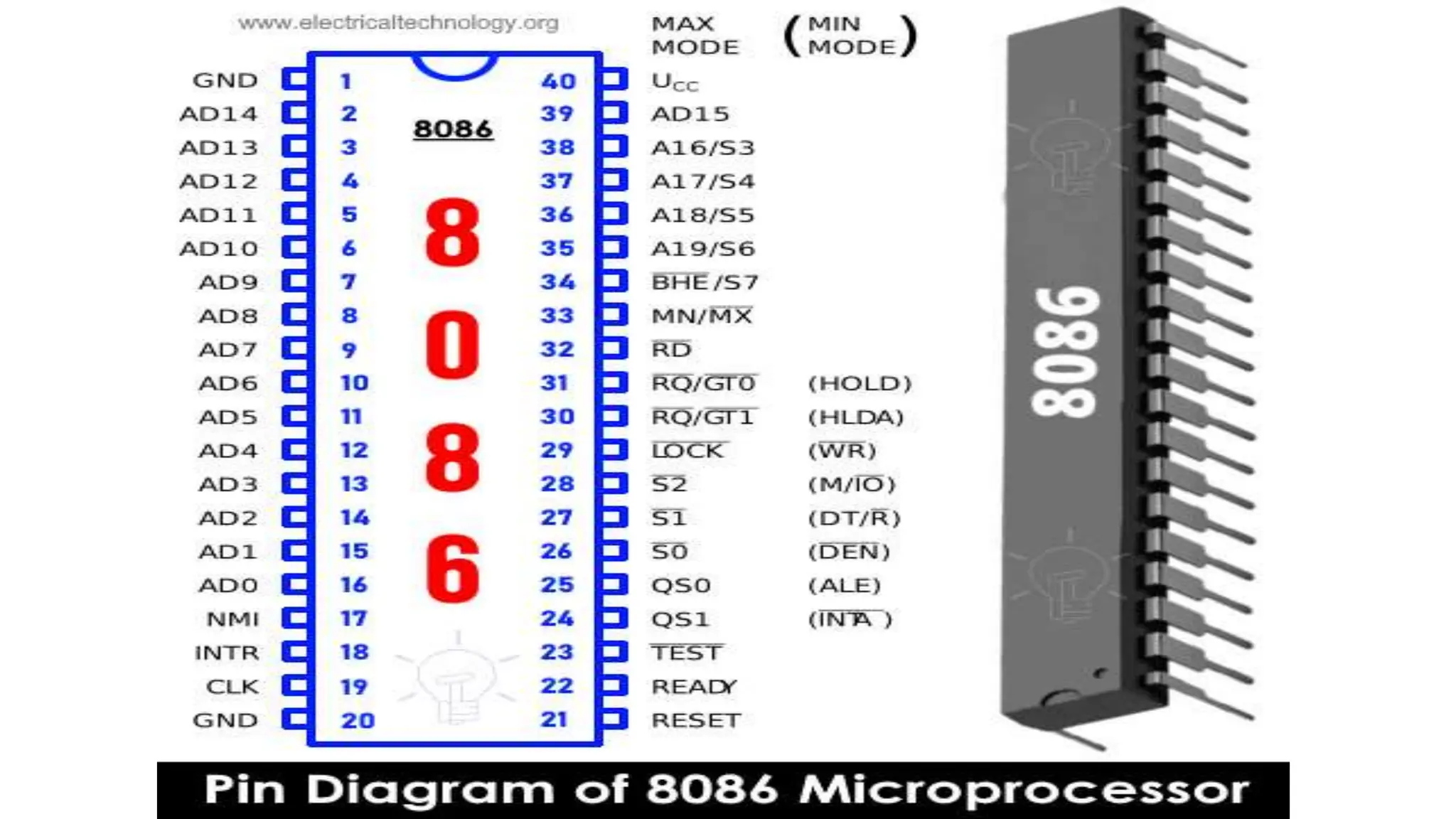

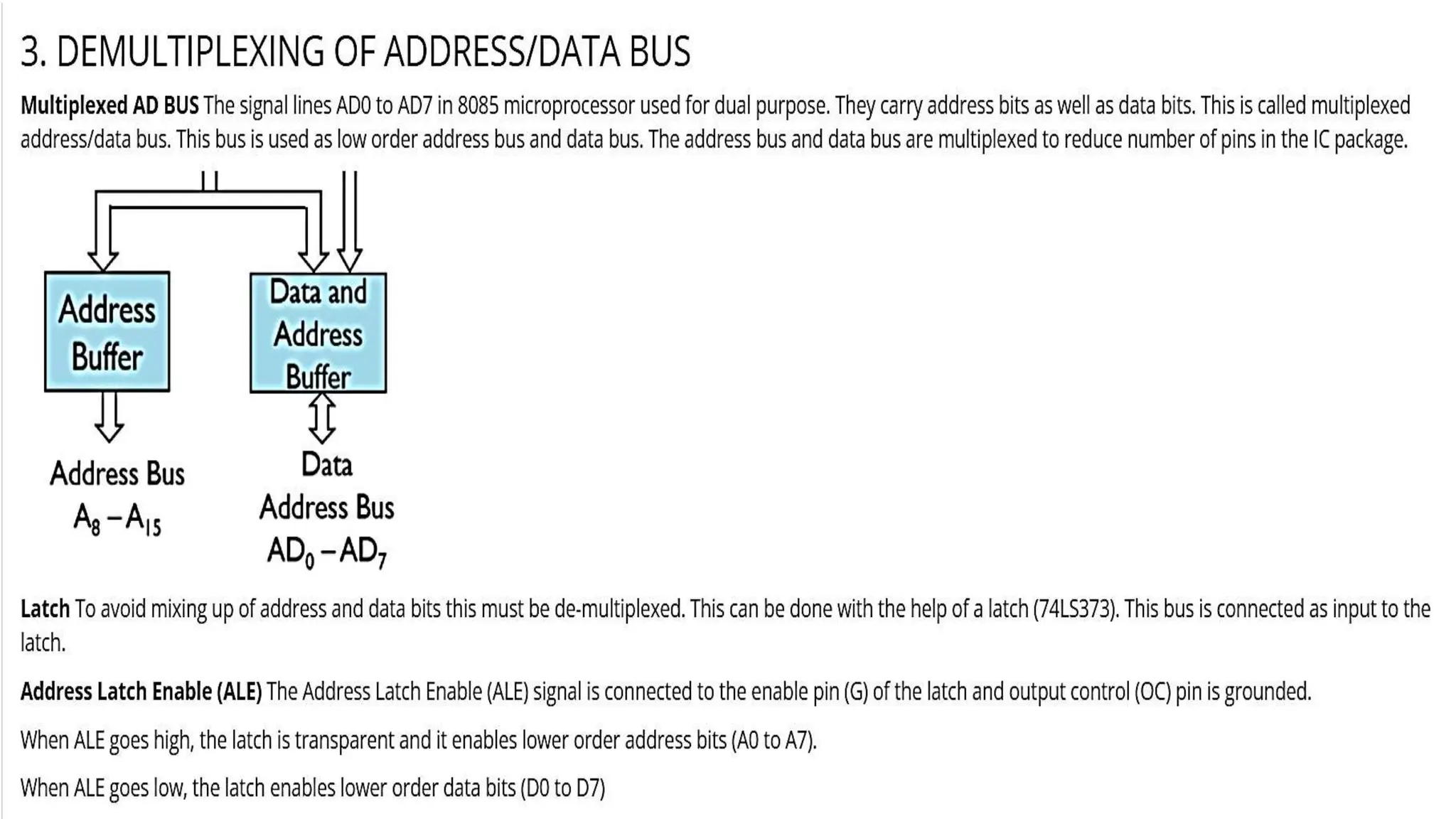

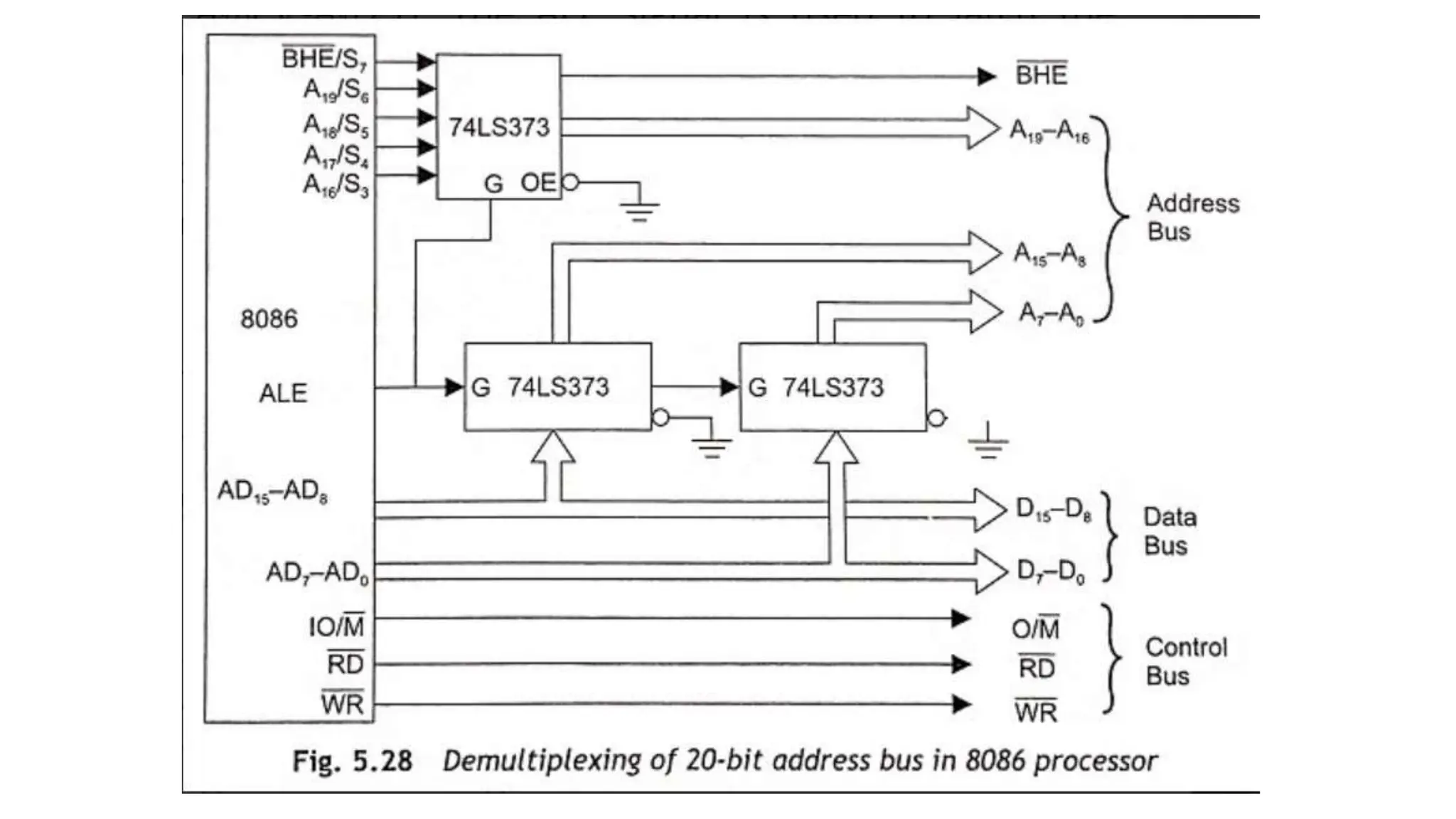

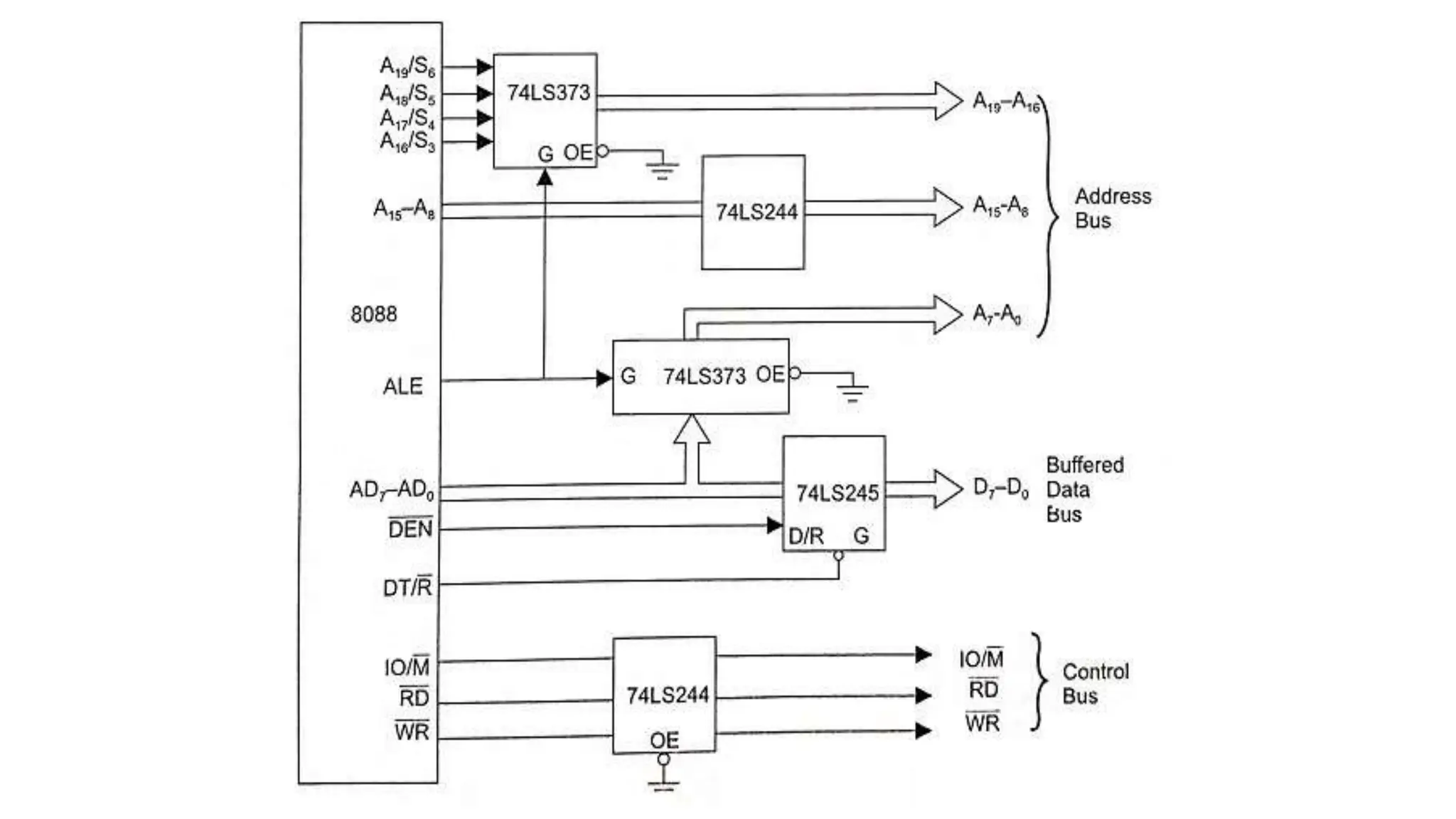

The document discusses the demultiplexing of the address and data buses in the 8086 microprocessor, which operates in a time-multiplexed mode for efficient data transfer. It explains the function of the address, data, and control buses, and the use of latch ICs for demultiplexing the 20-bit address lines. Additionally, it outlines the bi-directional nature of the data bus and the control signals that manage data flow.