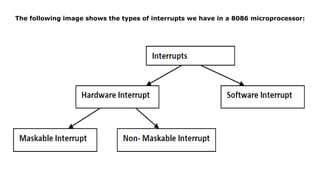

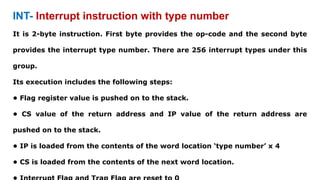

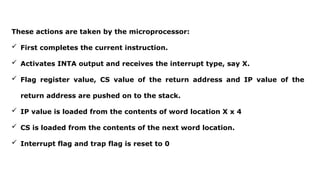

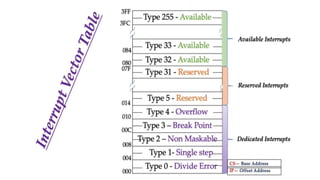

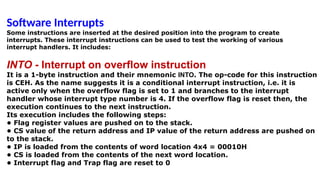

The document explains interrupts in the 8086 microprocessor, covering how they create temporary halts for peripheral devices to access the CPU. It details various interrupt types, including hardware and software interrupts, and their associated instructions like 'int', 'into', and 'iret'. Additionally, it outlines the processing steps and priority levels for these interrupts, emphasizing the role of the interrupt flag and different types of interrupt requests.