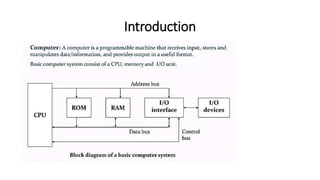

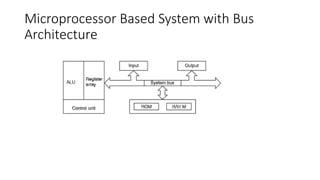

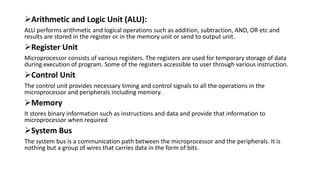

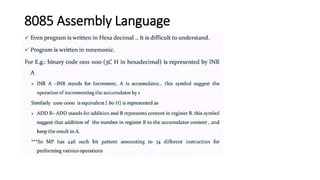

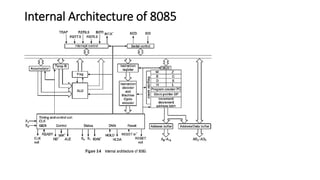

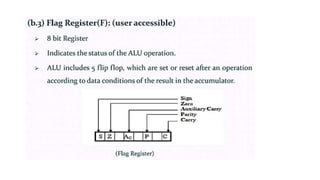

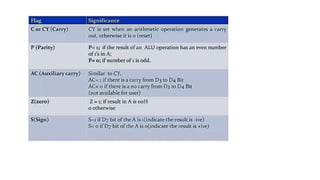

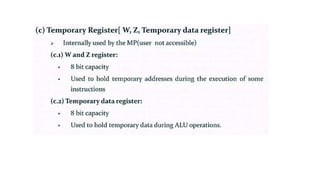

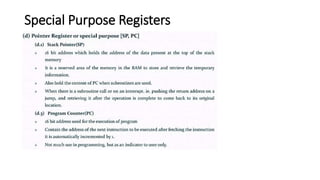

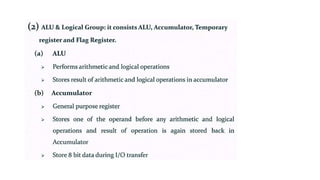

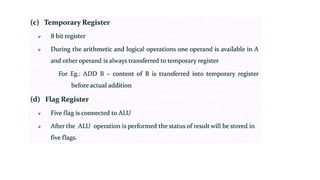

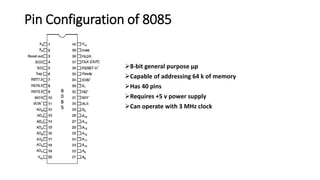

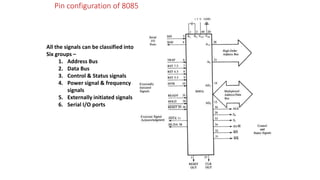

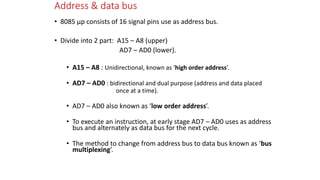

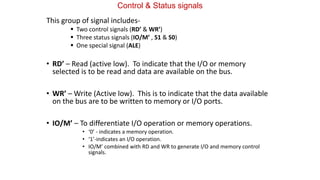

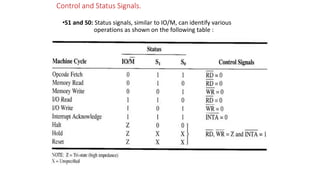

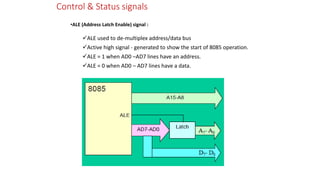

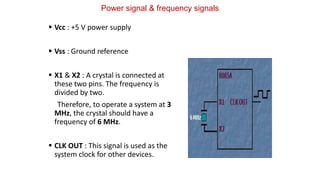

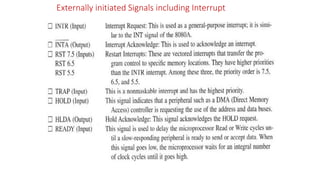

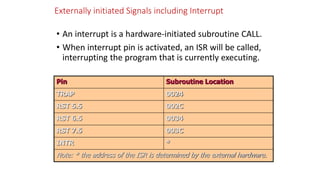

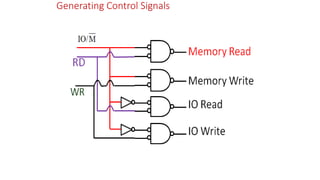

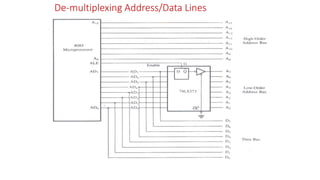

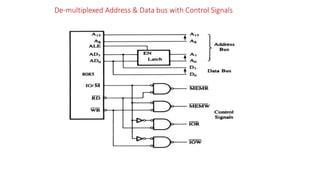

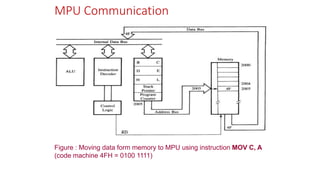

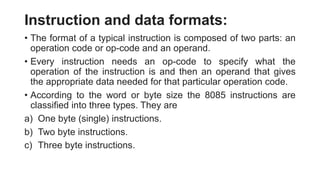

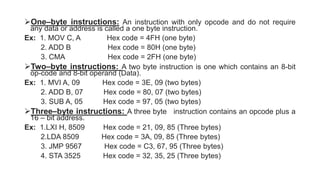

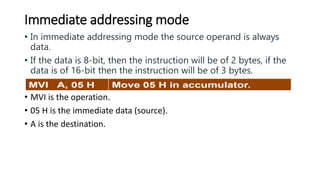

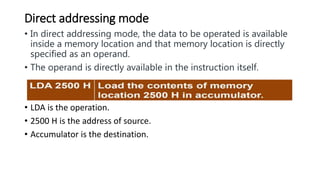

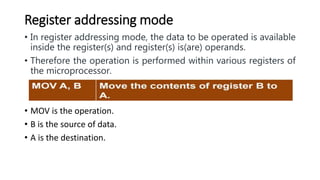

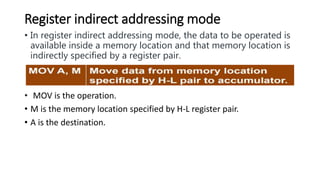

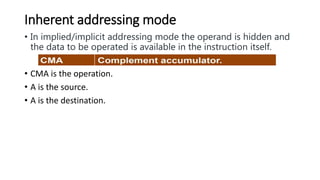

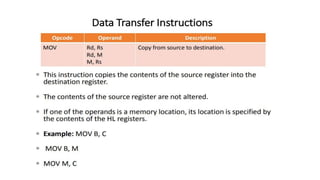

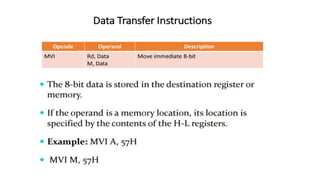

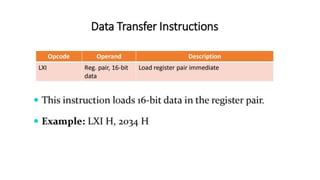

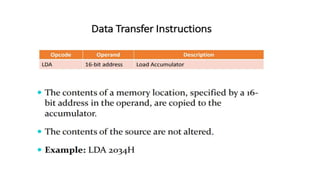

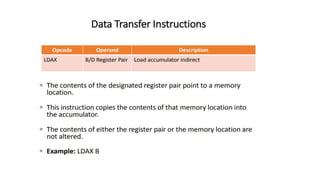

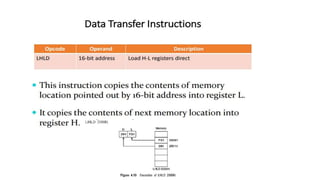

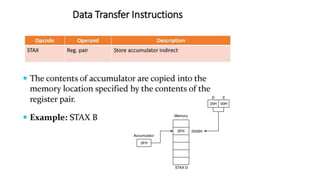

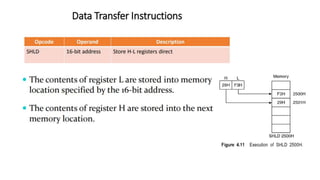

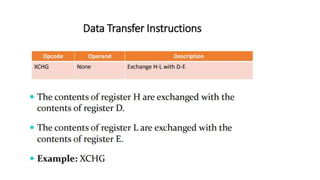

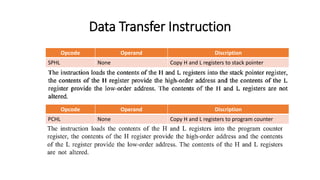

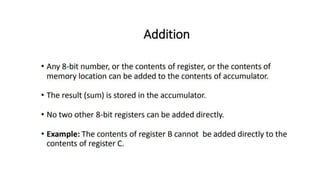

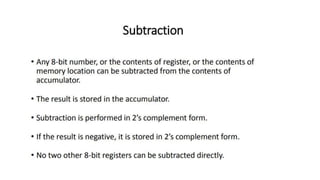

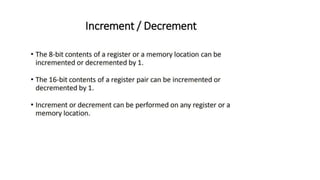

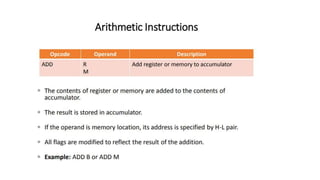

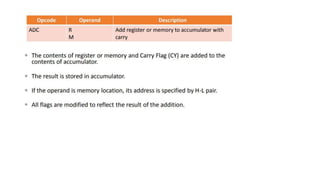

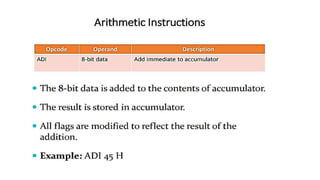

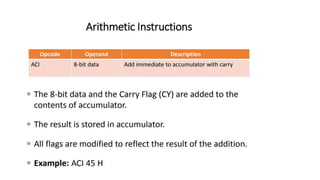

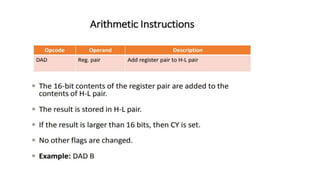

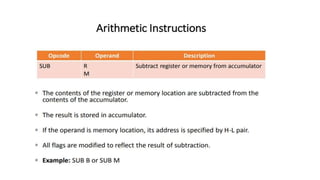

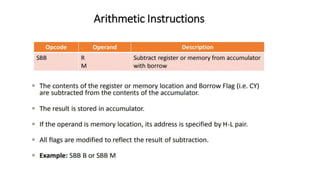

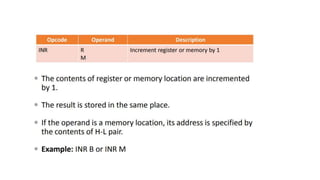

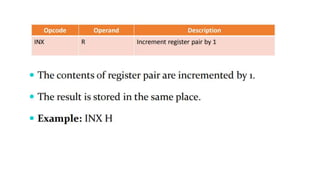

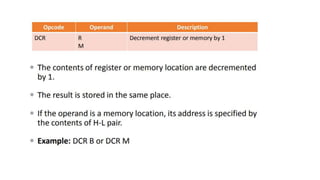

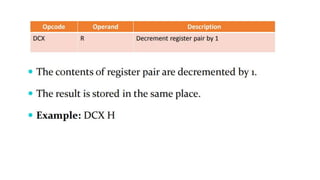

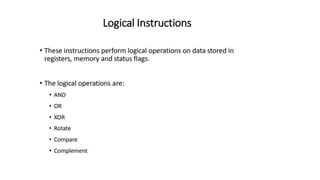

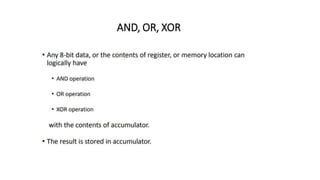

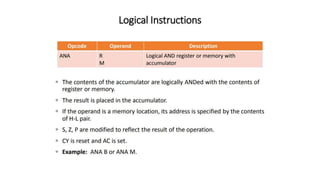

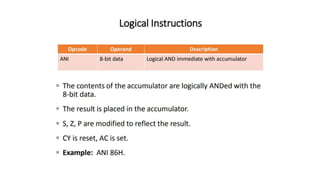

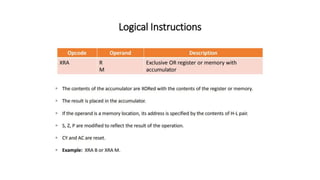

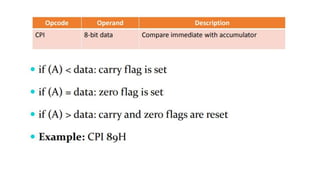

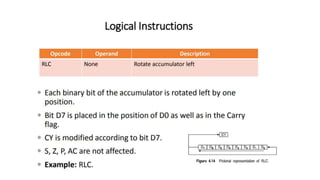

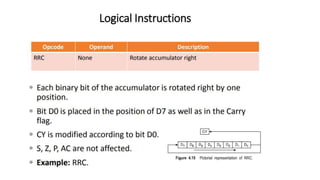

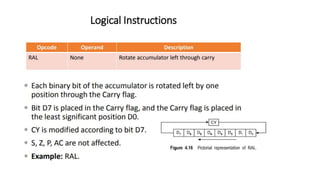

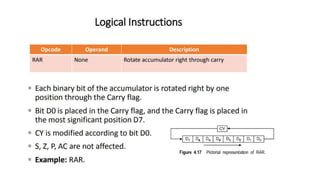

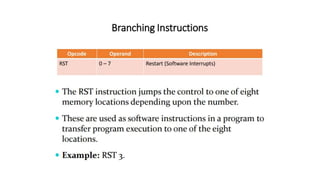

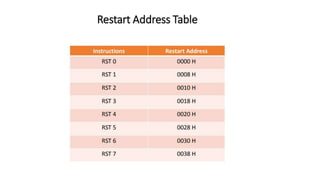

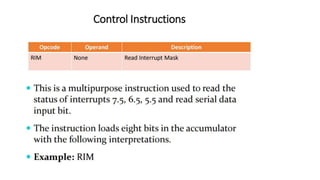

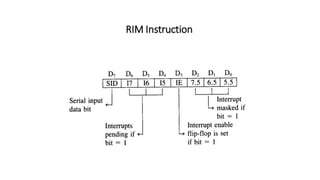

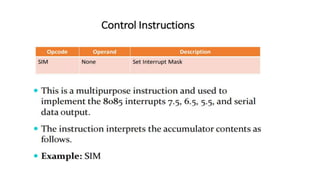

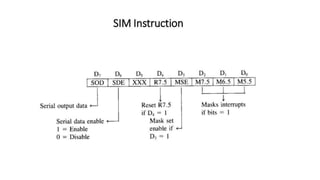

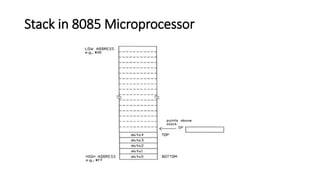

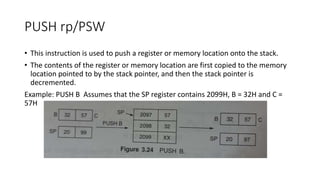

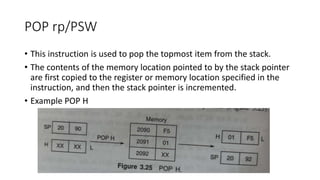

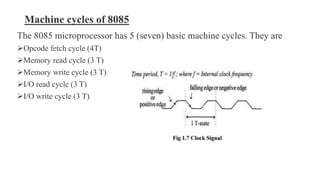

The document provides an overview of microprocessors and microcontrollers. It discusses the basic concepts of microprocessors including the definition, components like the ALU, registers, control unit, memory and system bus. It describes how a microprocessor works and introduces machine language and 8085 assembly language. The later lectures discuss the internal architecture, registers, pin configuration and instruction set of the 8085 microprocessor. It also covers addressing modes, classification of instructions and use of the stack in 8085.