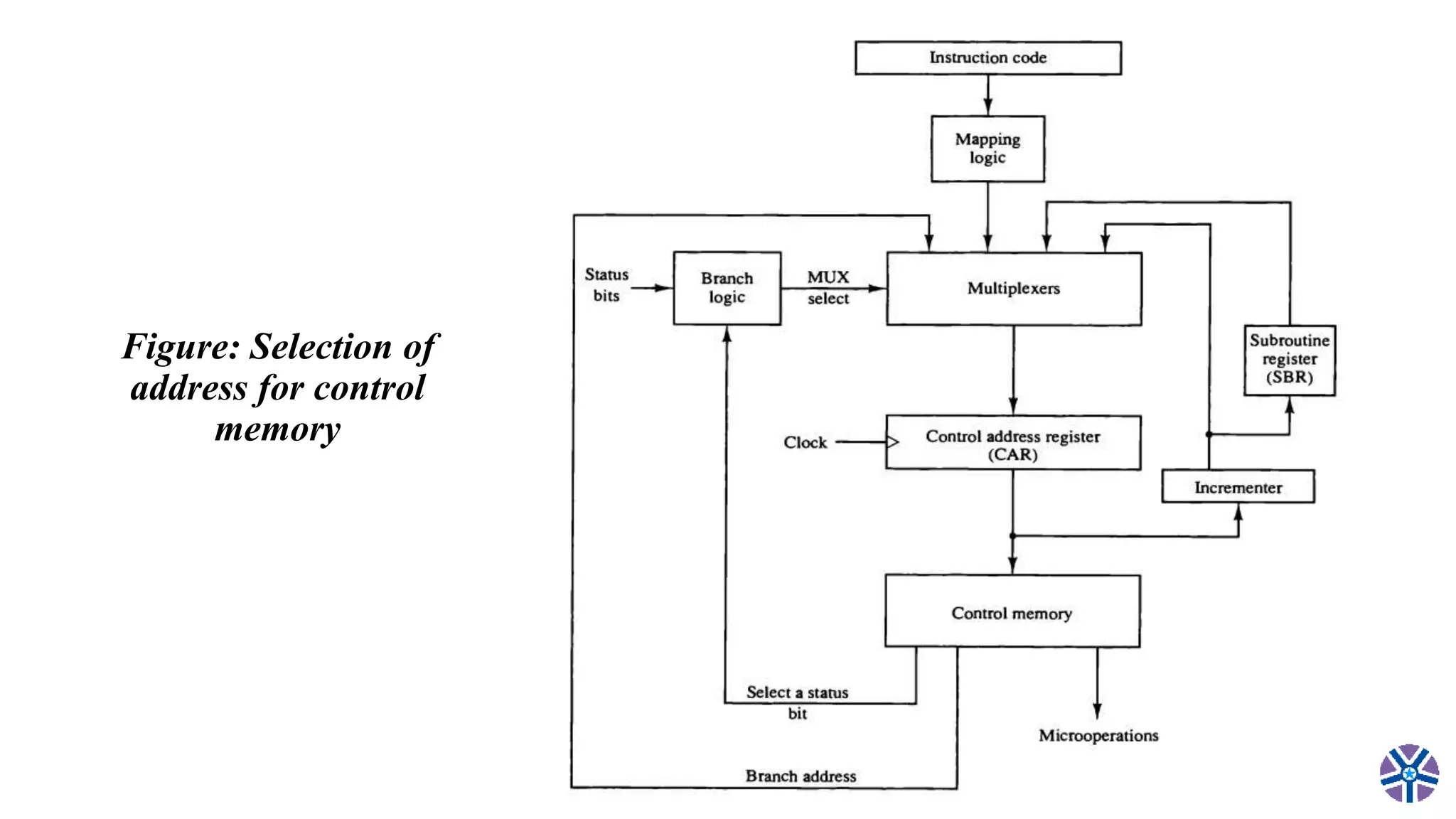

This document discusses the topics to be covered in a session on computer organization and architecture. It provides an overview of microprogrammed control, including control memory, address sequencing, microprogram examples, and the design of the control unit. Specific topics that were covered in the previous session are outlined, such as microprogrammed control, control memory, address sequencing, microprogram examples, and the design of the control unit. The next session is planned to cover microprogramming examples. Relevant textbooks and references are also listed.