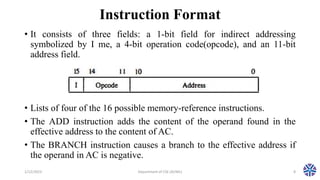

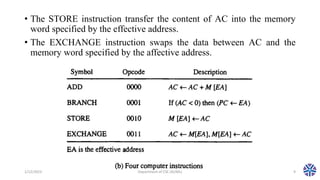

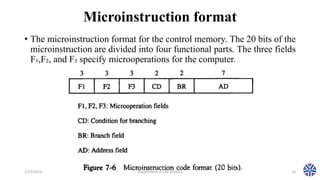

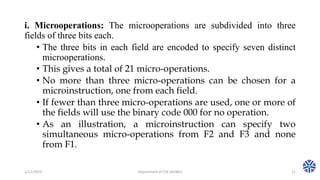

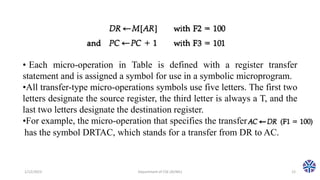

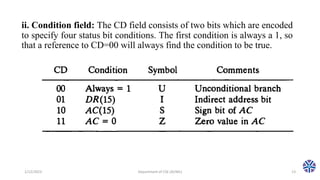

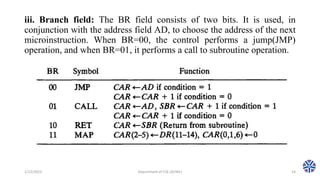

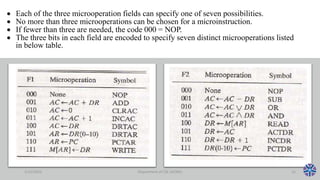

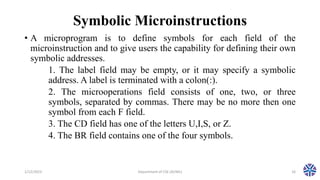

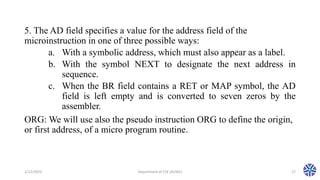

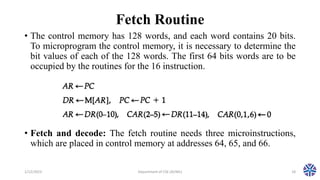

This document provides an overview of the topics covered in a session on computer organization and architecture. It discusses microprogrammed control, including control memory, address sequencing, and the design of the control unit. It provides an example of a microprogram, including the instruction format, microinstruction format, and a symbolic and binary representation of a fetch routine microprogram. The session covered microprogrammed control, control memory, address sequencing, an example microprogram, and the design of the control unit.