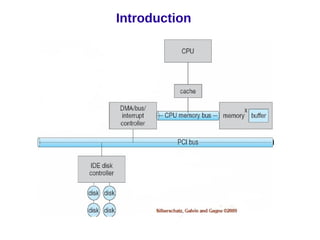

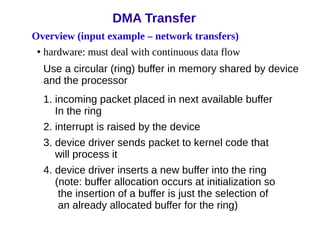

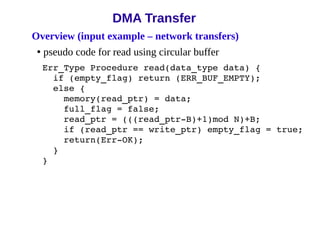

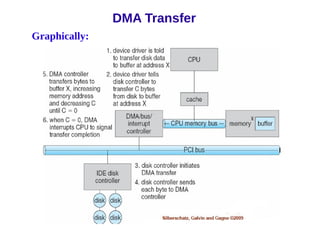

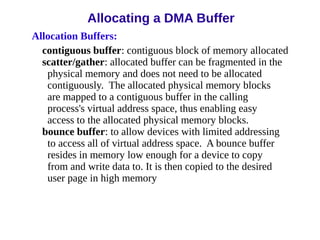

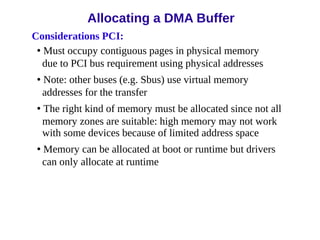

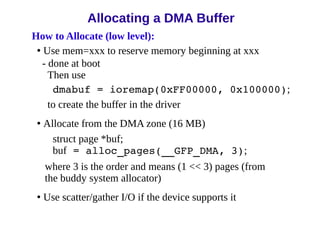

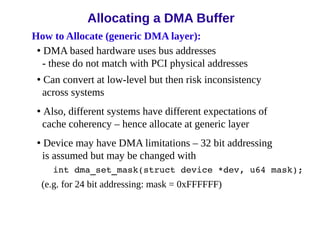

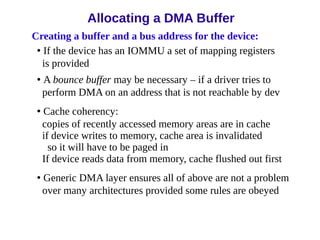

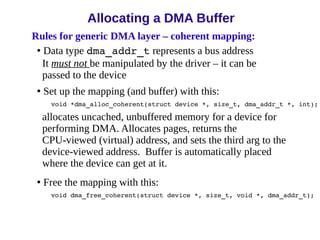

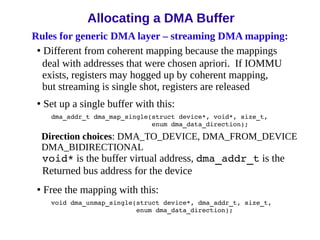

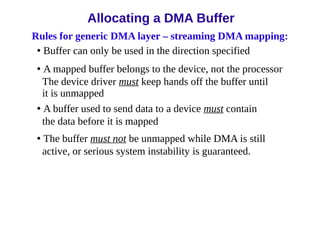

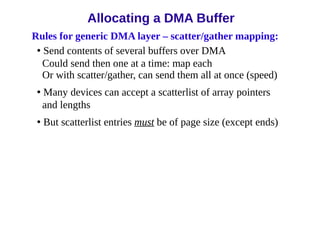

Direct memory access (DMA) allows peripheral devices to access main memory directly without intervention from the CPU. This improves data transfer speeds by eliminating CPU overhead. Hardware support is required in the form of DMA controllers. DMA can cause cache coherency issues if the CPU cache is not properly invalidated or flushed. The document discusses DMA programming, buffer allocation, and ensuring cache coherency between DMA transfers and the CPU cache.