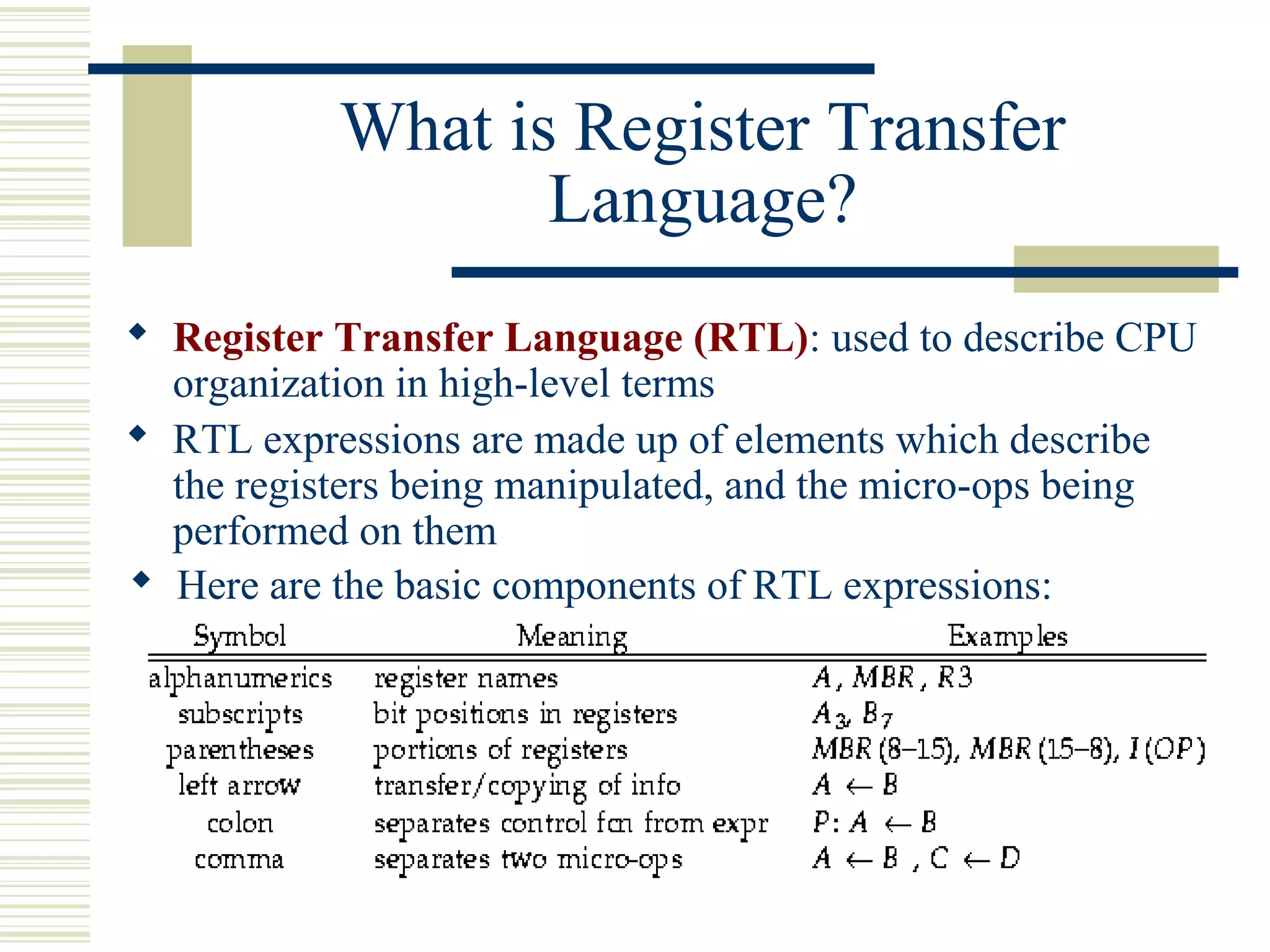

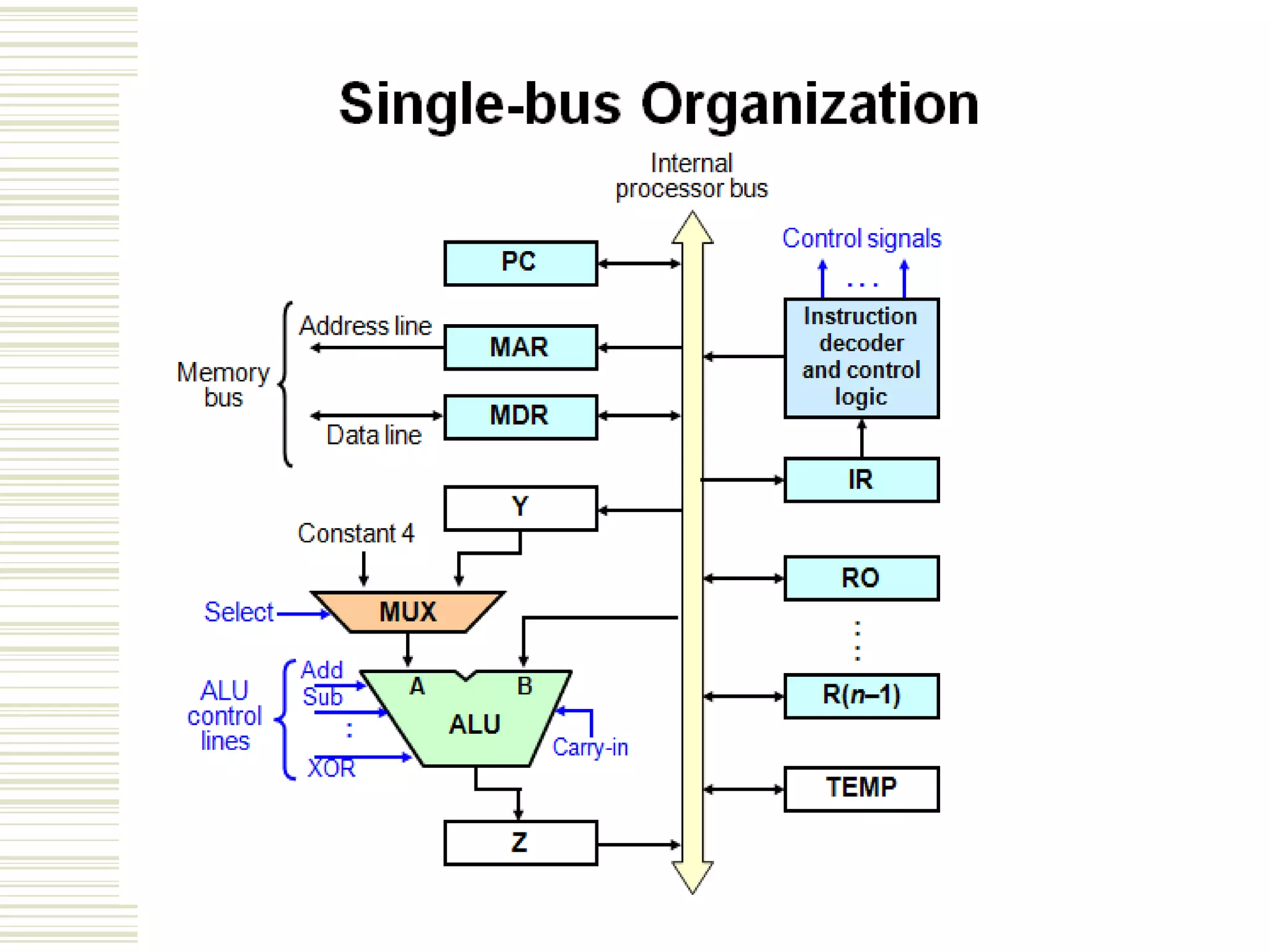

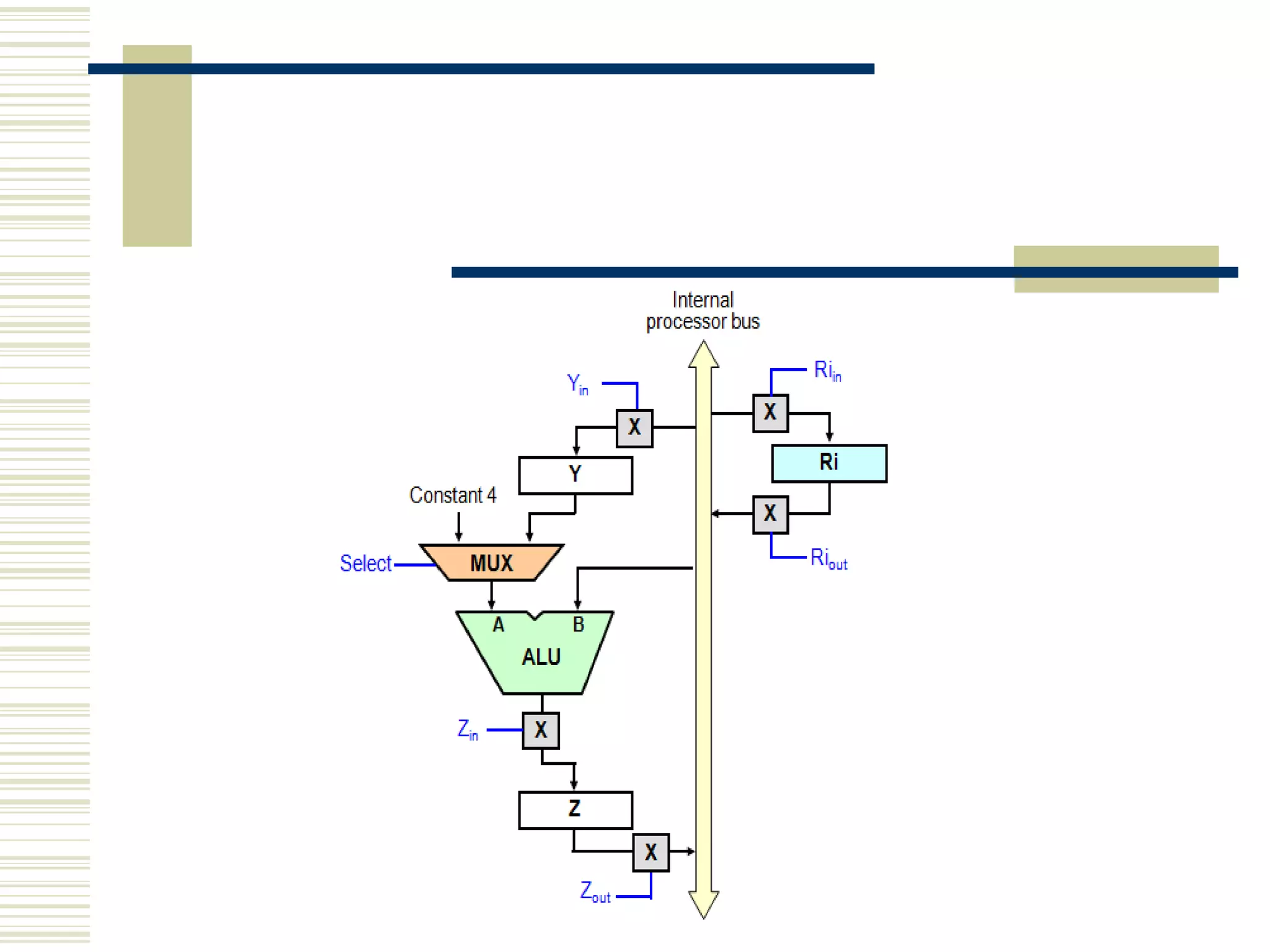

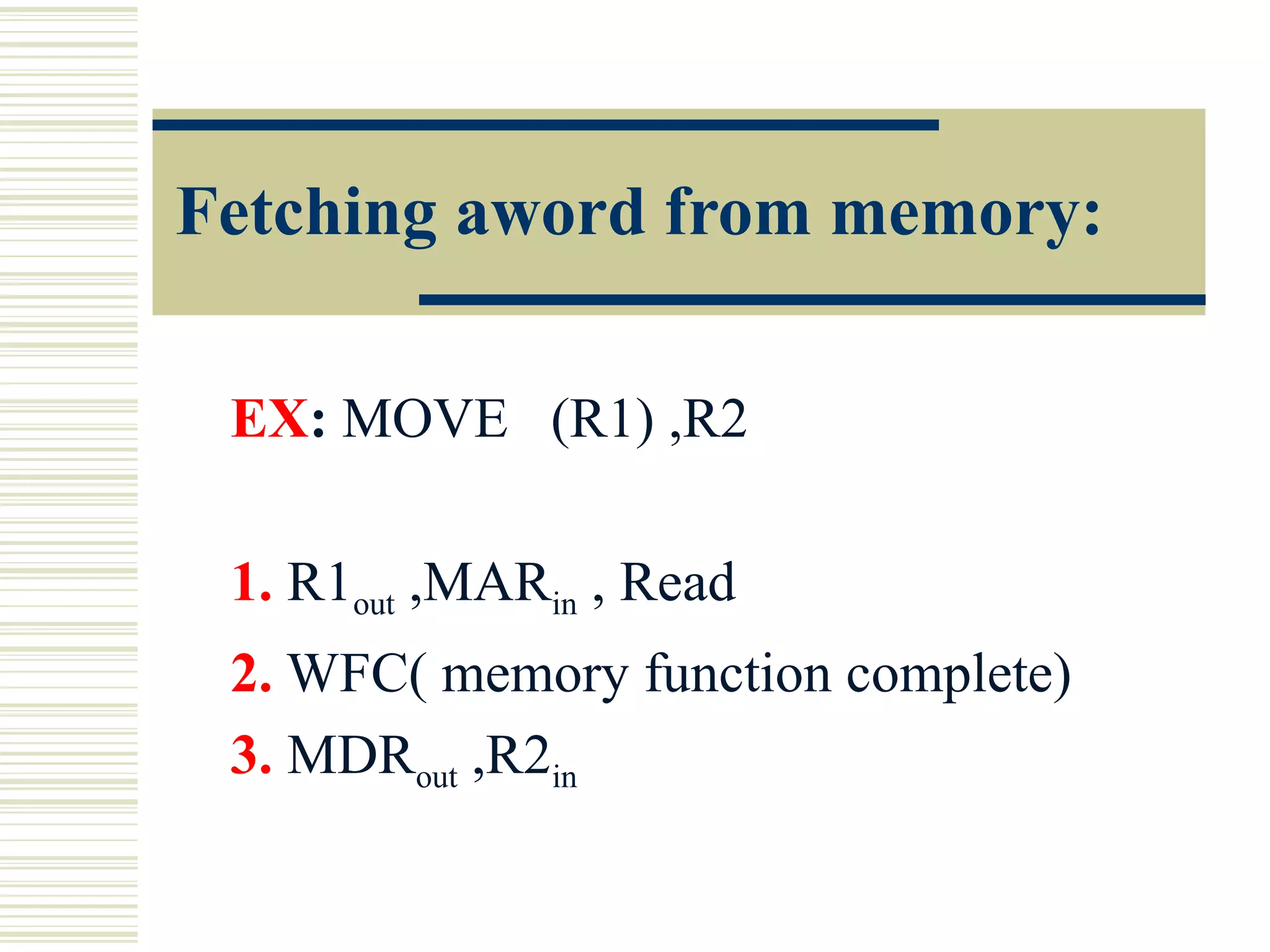

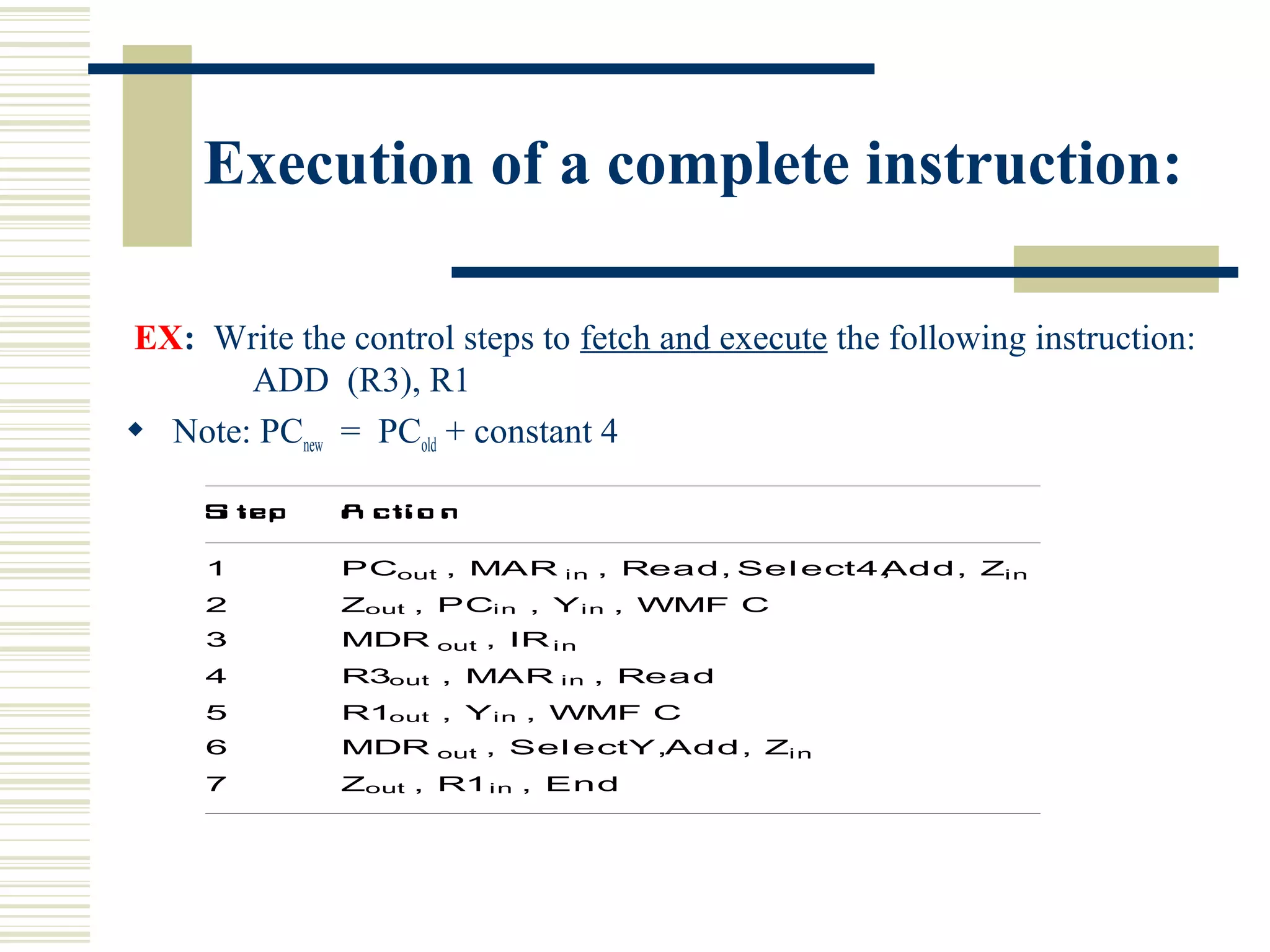

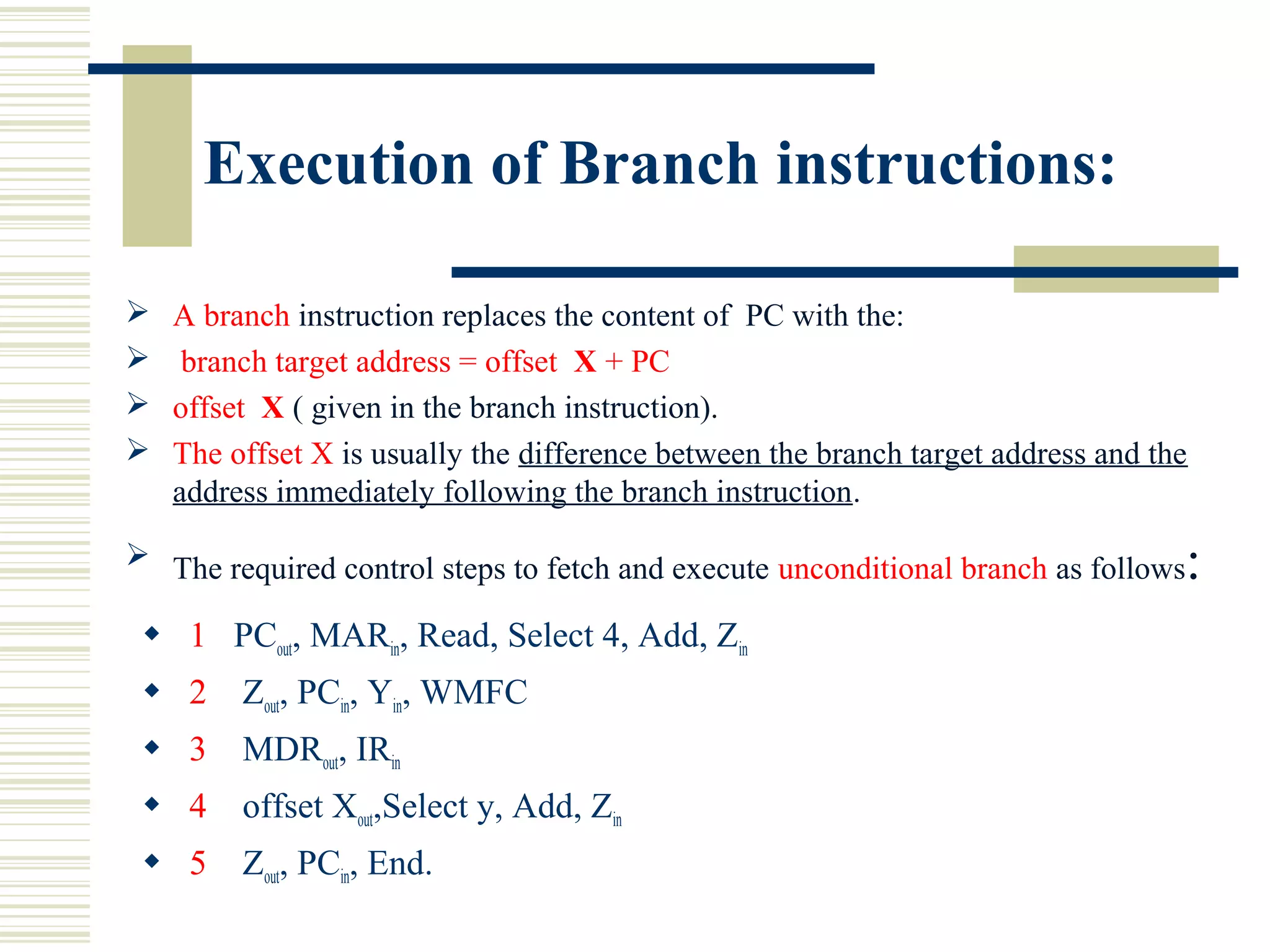

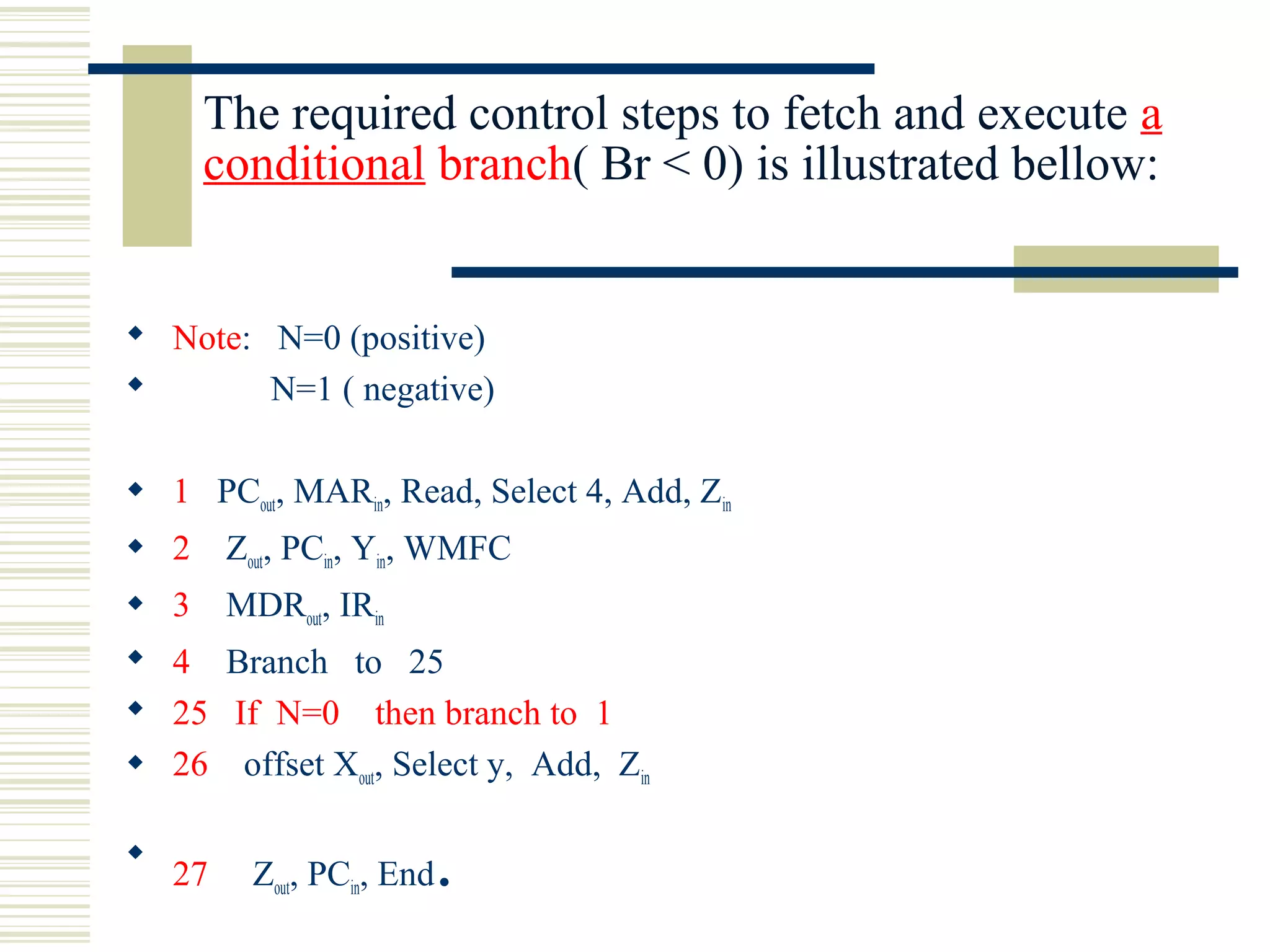

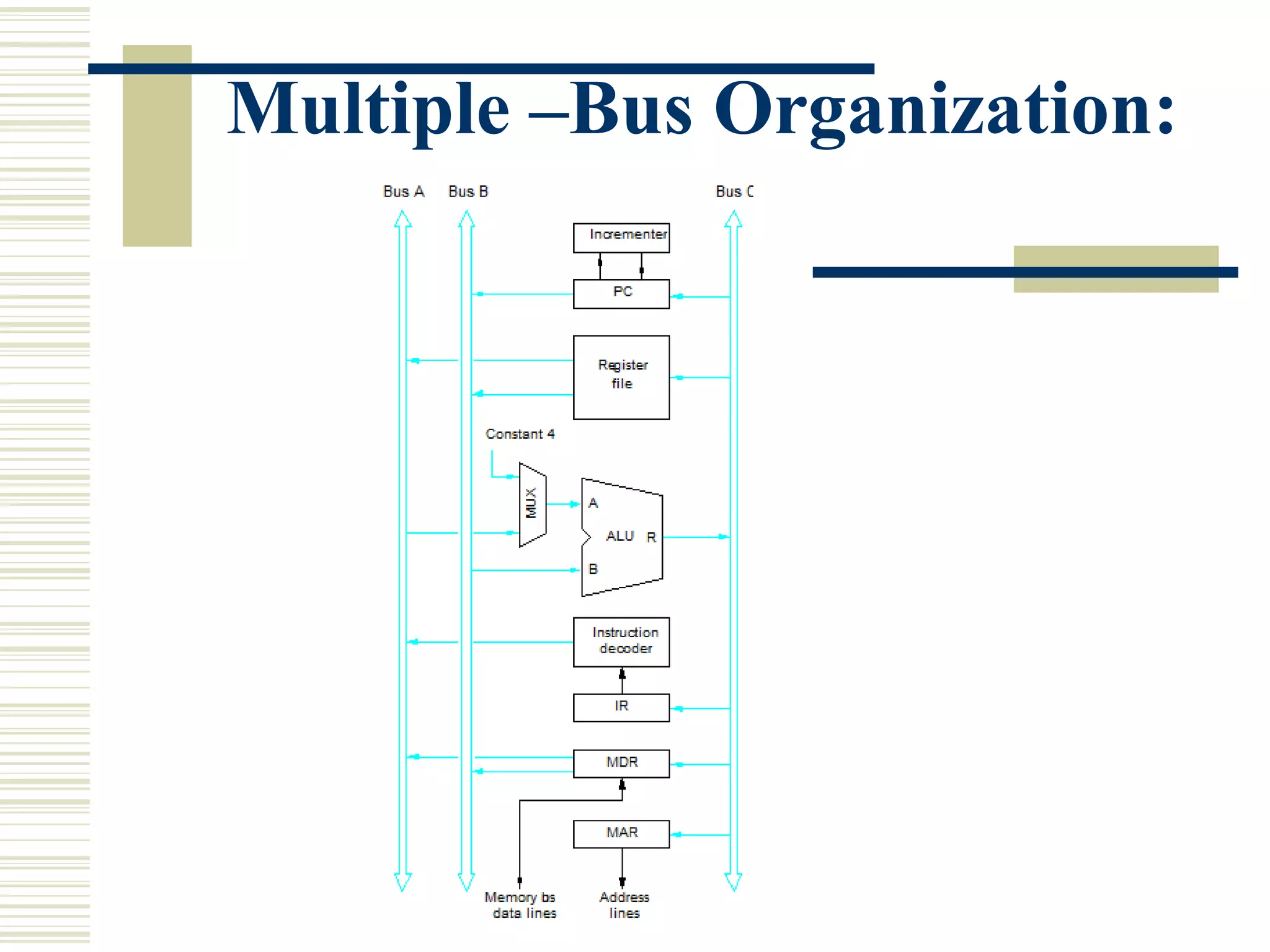

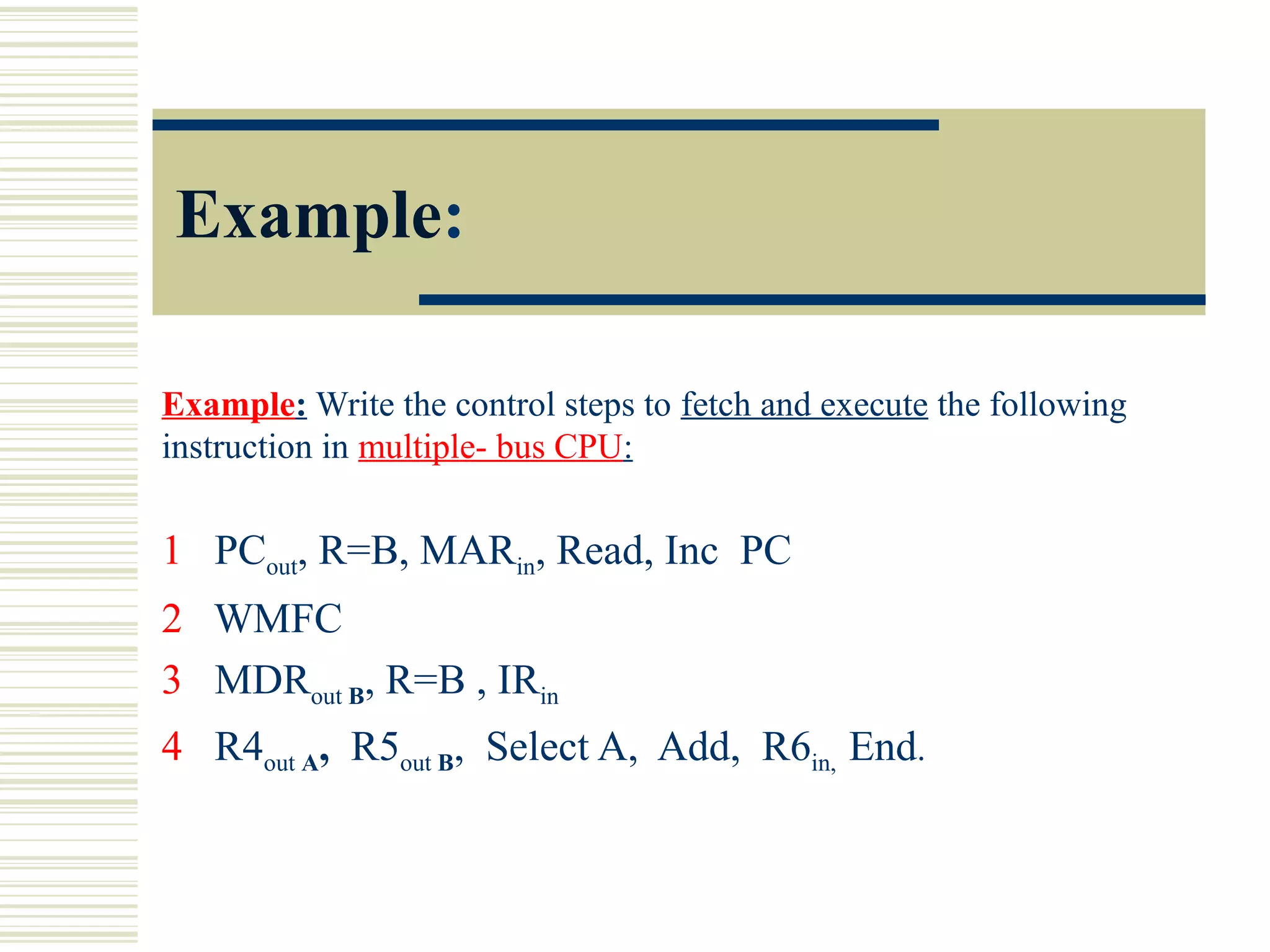

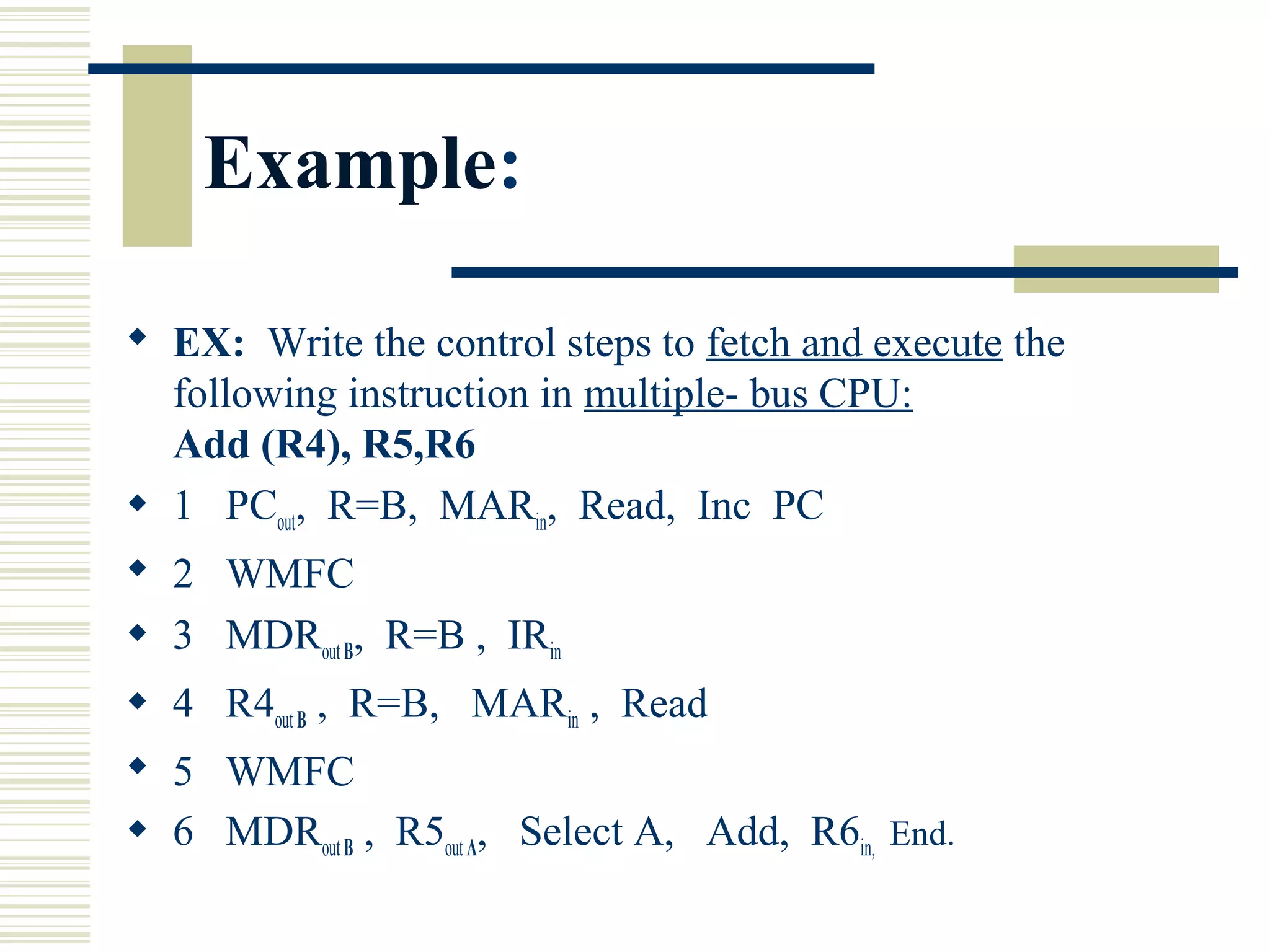

Register Transfer Language (RTL) is an intermediate representation used to describe data flow at the register-transfer level in computer architecture. It outlines the organization of a CPU using high-level expressions and includes instructions for fetching and executing commands, managing memory operations, and handling control signals for registers. The document also details how to execute branch instructions and demonstrates control steps in multiple-bus CPU organizations.