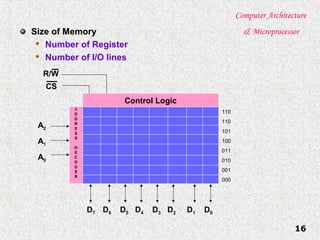

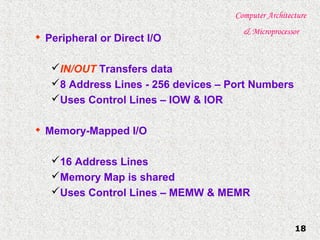

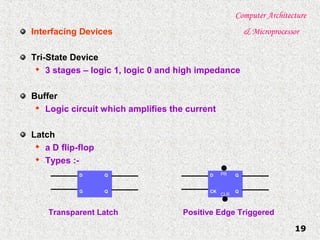

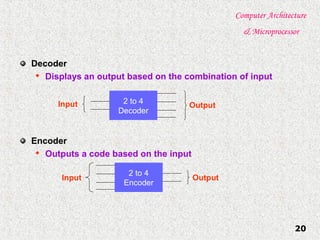

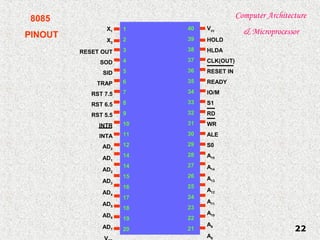

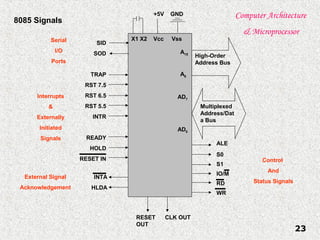

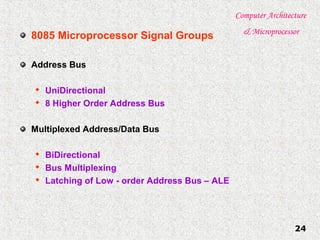

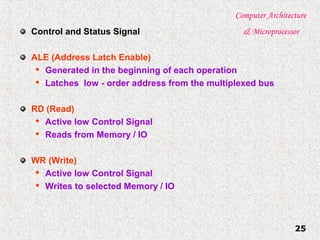

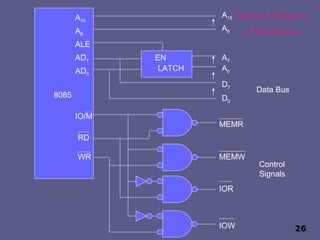

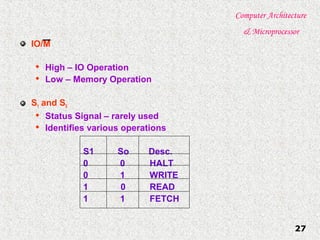

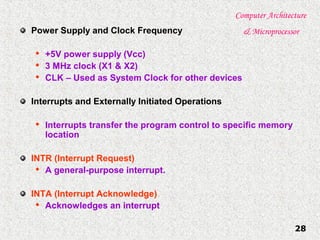

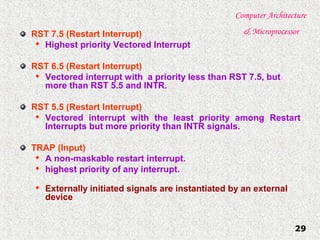

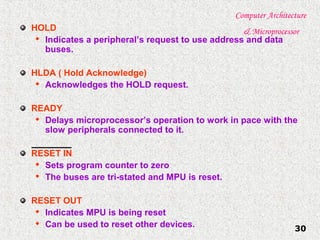

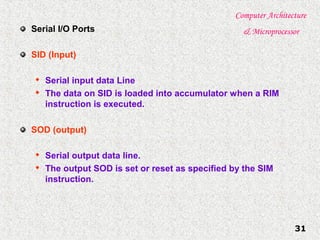

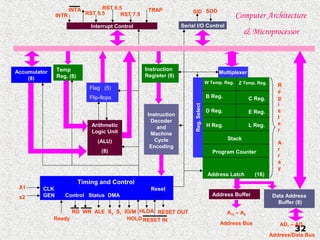

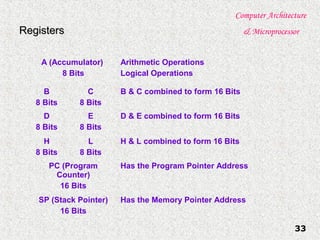

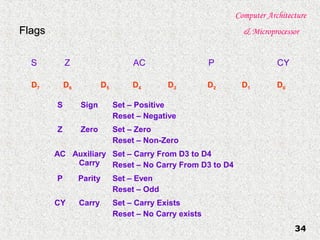

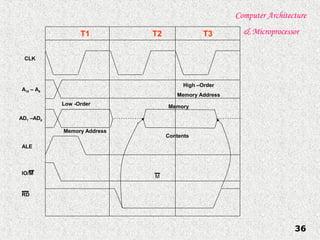

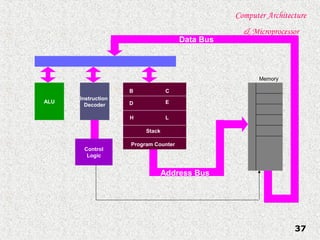

The document provides an overview of computer architecture and microprocessors. It discusses microprocessor components like the accumulator, registers, flags, and control bus. It describes microprocessor operations like memory reads, writes and I/O. It also covers the 8085 microprocessor architecture in detail, including its pin configuration, buses, registers, interrupts and timing.