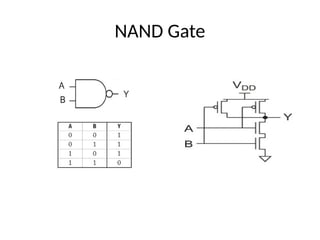

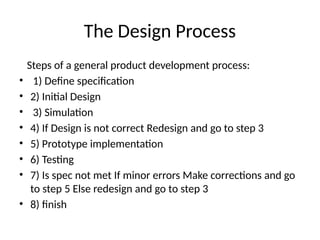

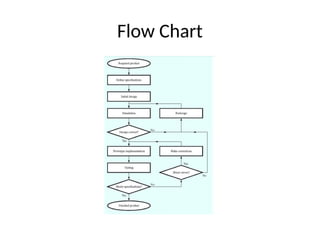

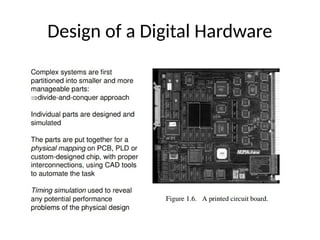

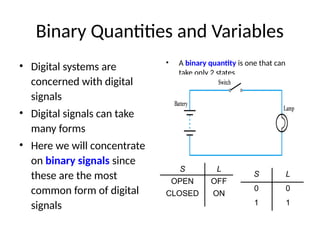

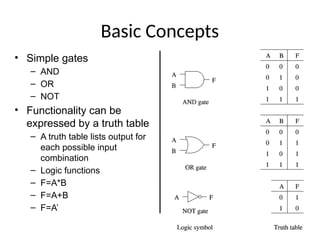

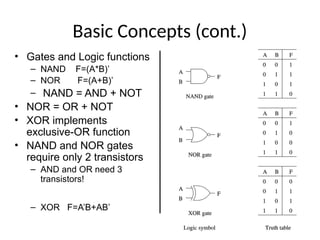

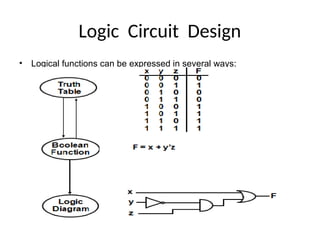

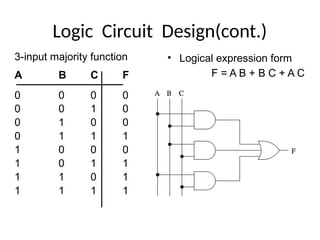

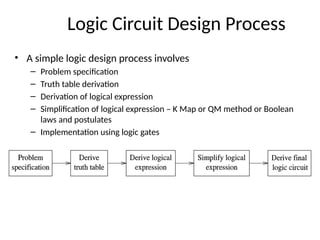

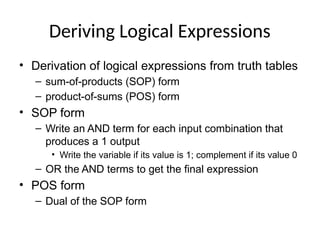

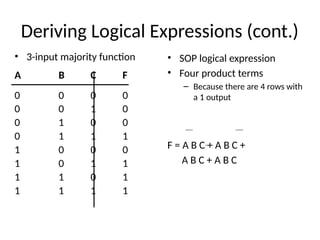

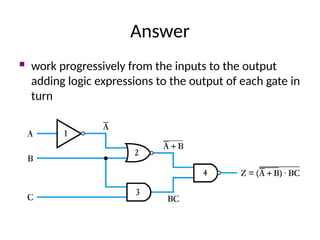

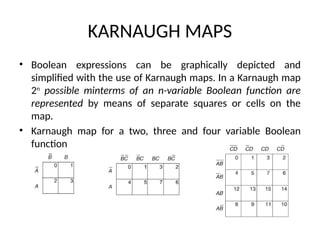

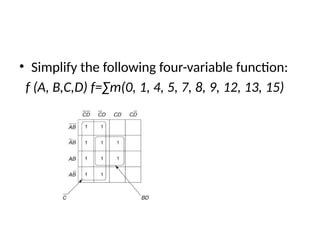

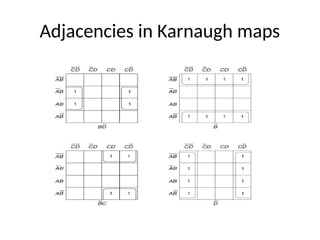

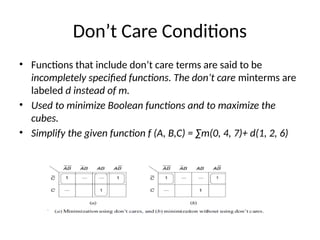

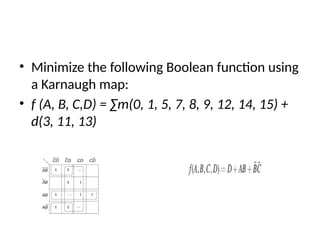

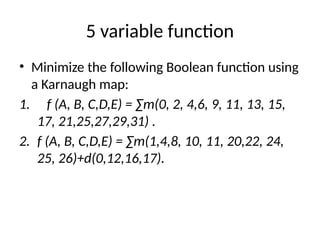

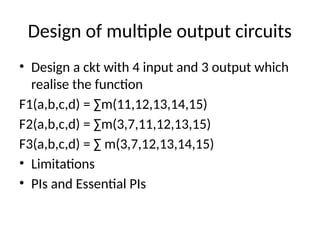

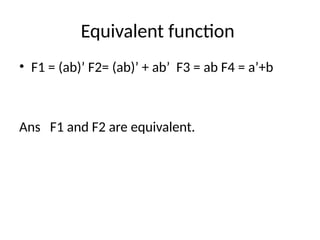

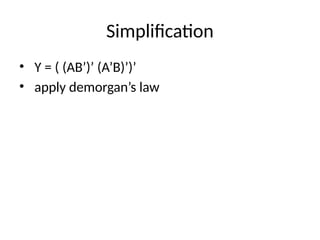

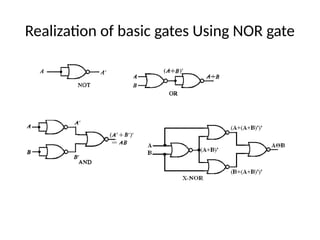

This document outlines the syllabus for a digital electronics course, covering design concepts, logic circuits, boolean algebra, and digital hardware components. It details course outcomes, including the ability to design combinational and sequential circuits, as well as write VHDL code. Additional sections discuss the design process, basic logic gates, and the application of Karnaugh maps for circuit simplification.