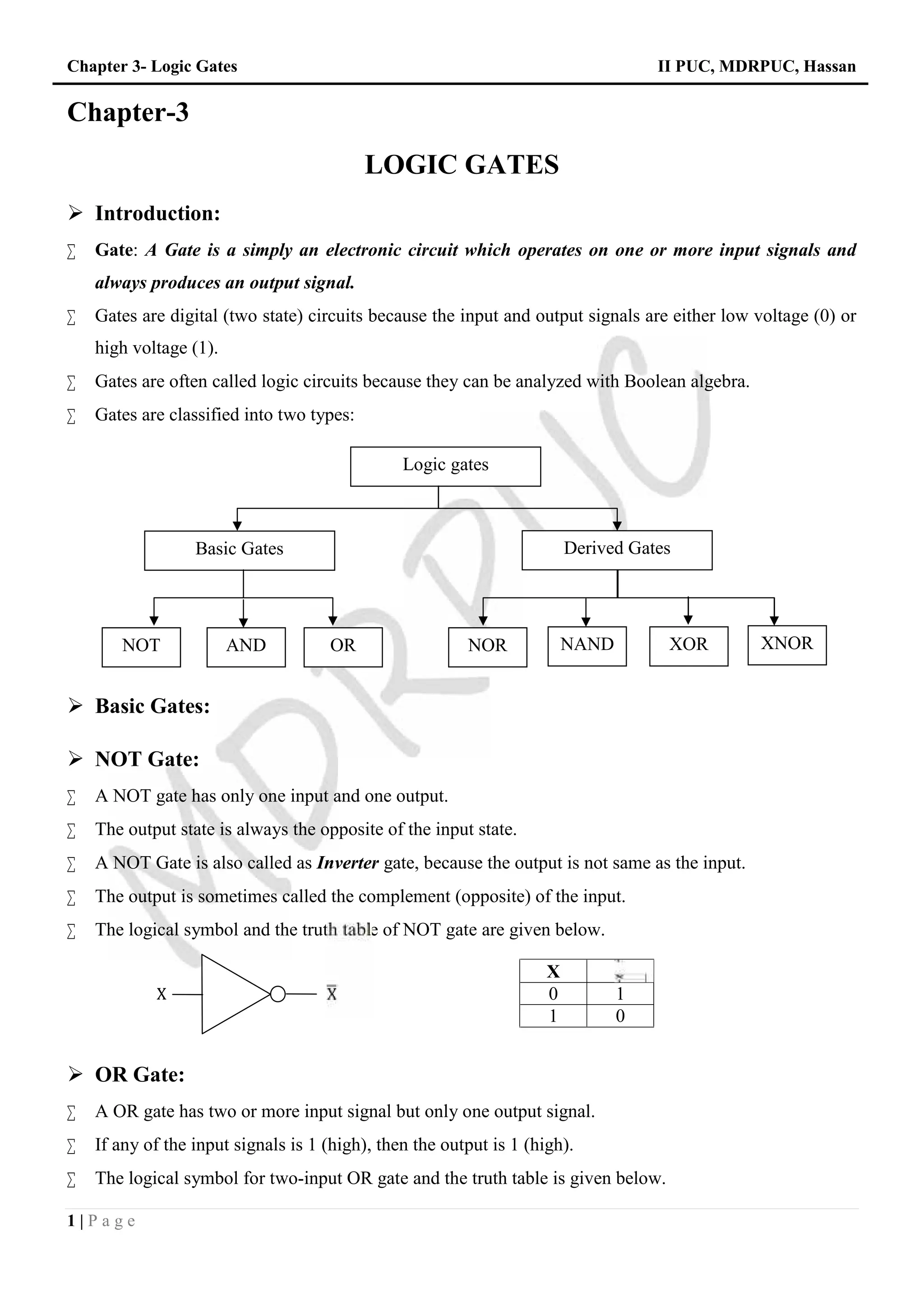

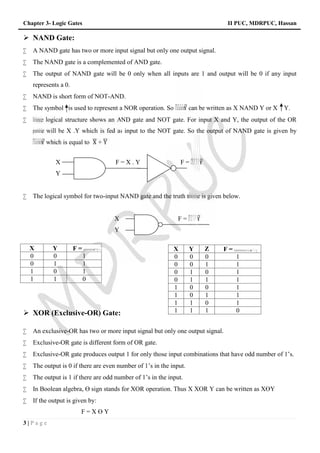

This document discusses logic gates and their types. It begins by defining a gate and explaining that gates are digital circuits with two state (0 or 1) inputs and outputs. It then covers the basic gates - NOT, OR, AND, NOR and NAND - providing their symbols, truth tables and descriptions. The document also discusses derived gates like XOR and XNOR. It explains that NAND and NOR gates are universal gates since all other gates can be realized using only these two gate types. Finally, it provides examples of realizing NOT, AND and OR gates using only NAND gates or only NOR gates.