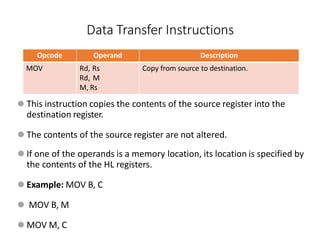

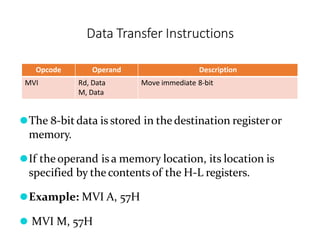

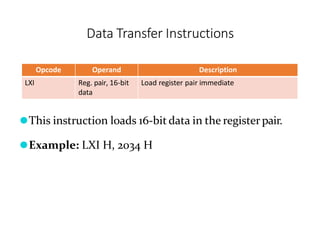

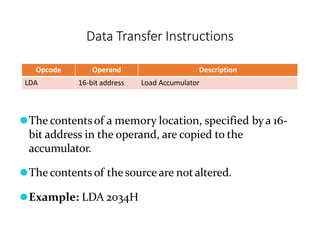

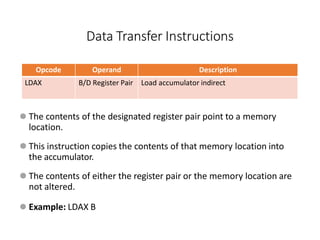

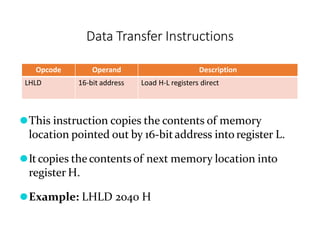

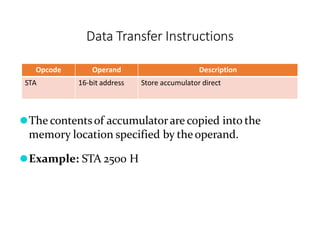

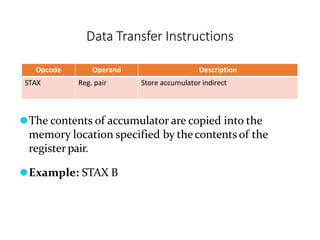

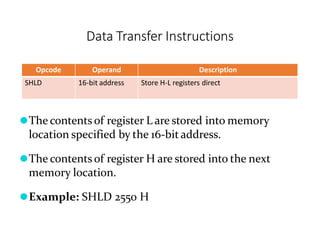

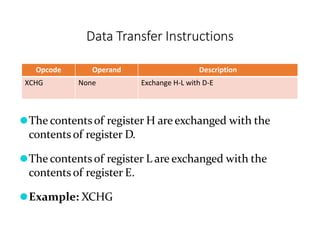

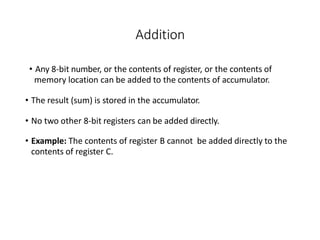

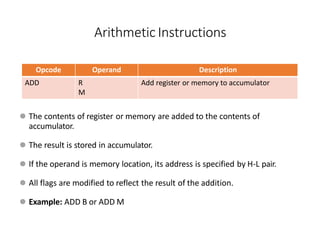

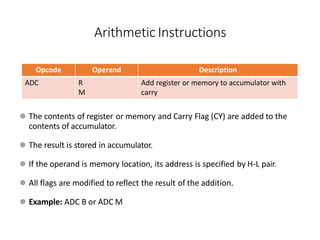

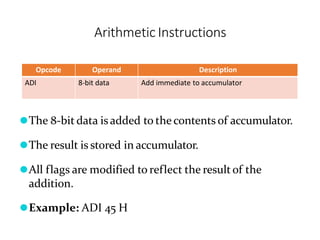

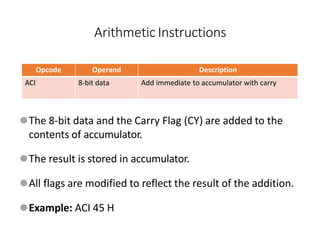

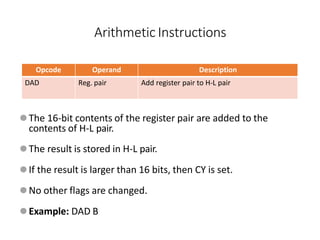

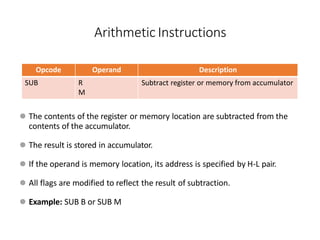

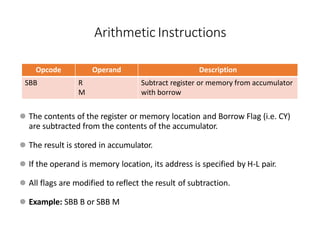

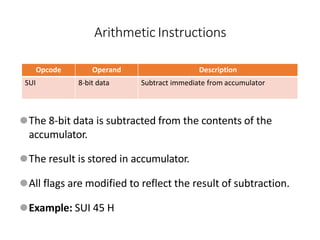

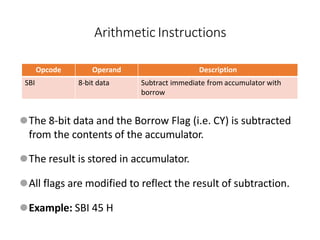

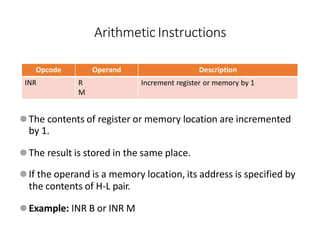

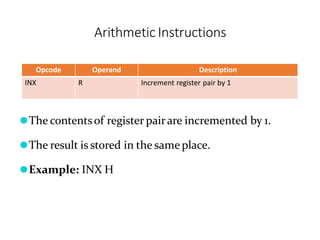

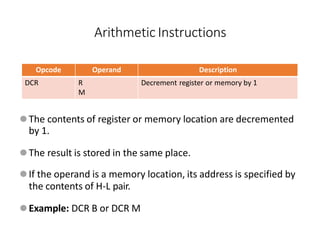

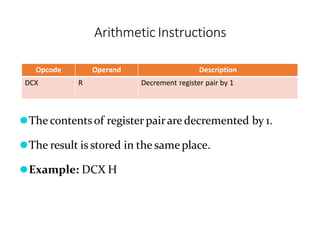

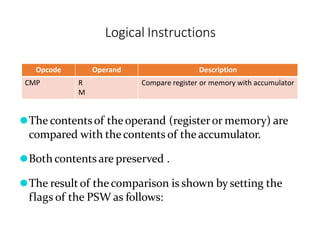

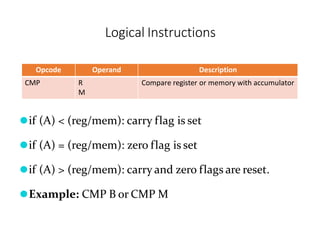

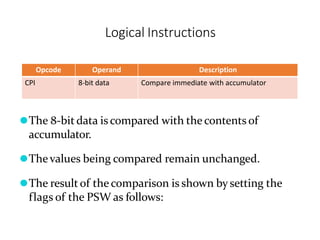

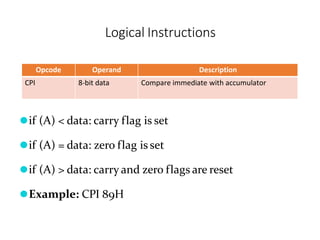

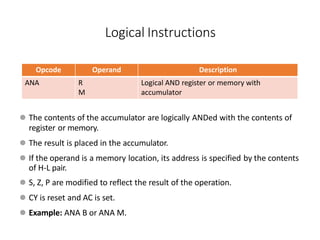

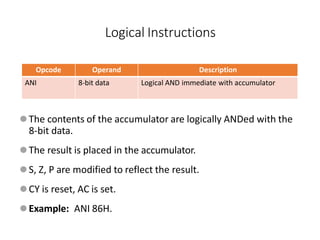

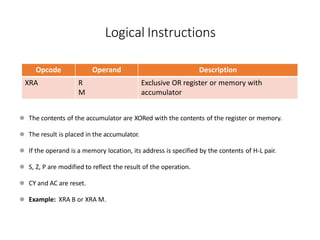

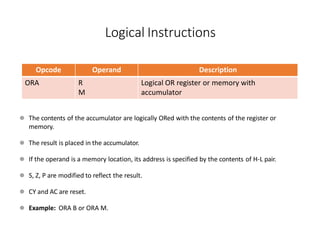

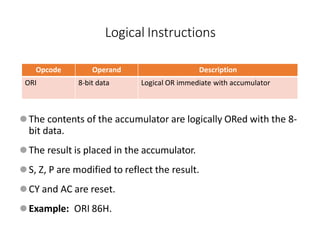

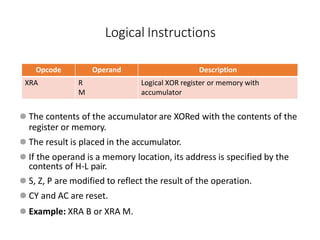

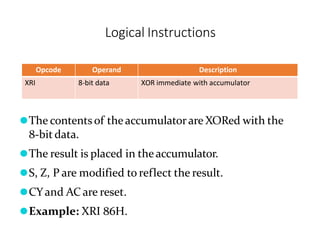

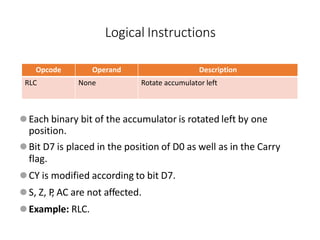

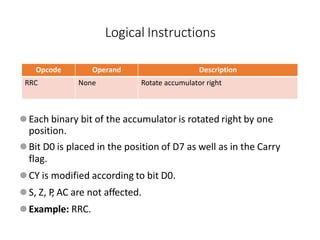

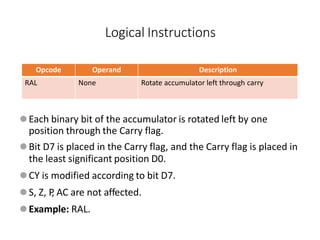

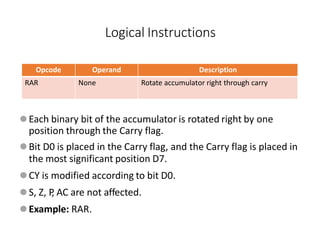

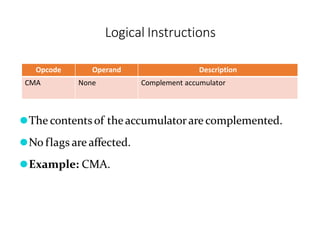

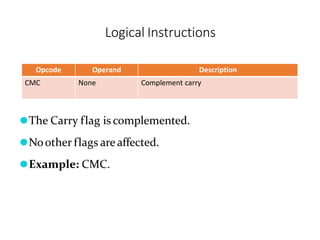

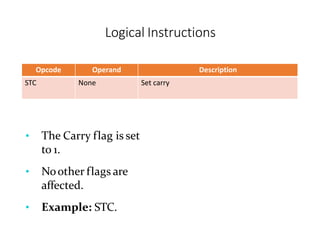

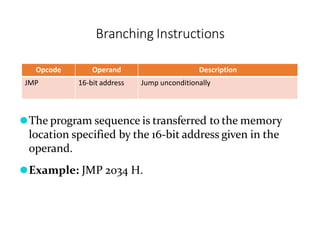

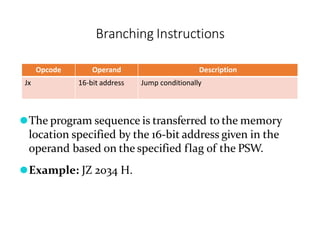

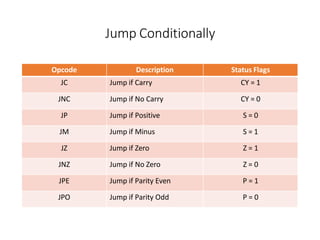

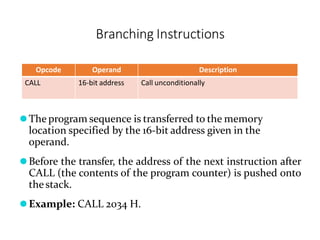

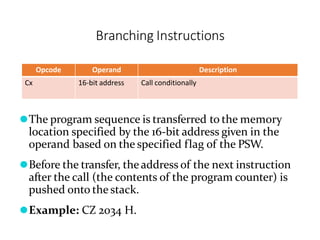

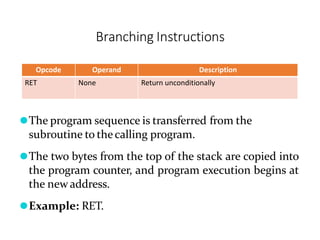

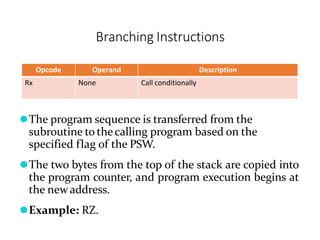

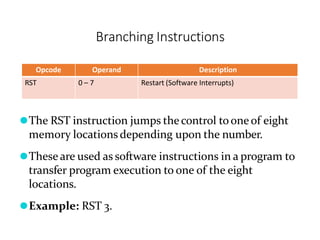

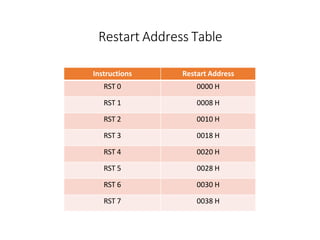

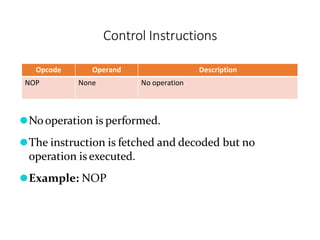

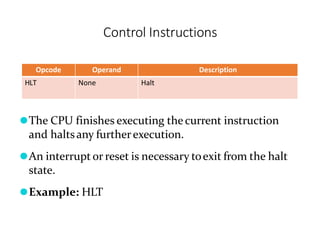

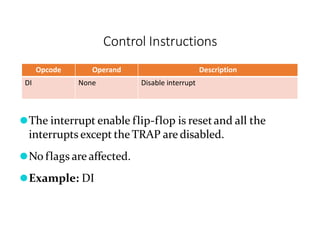

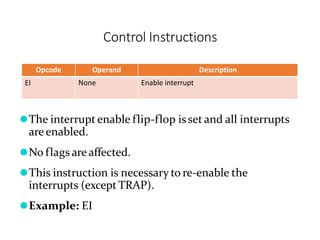

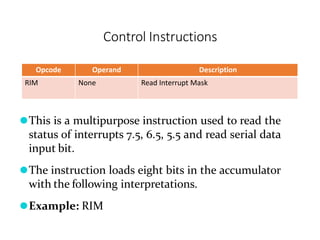

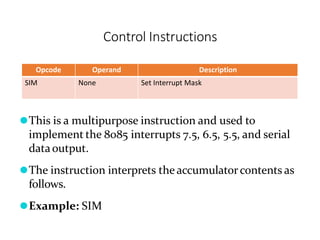

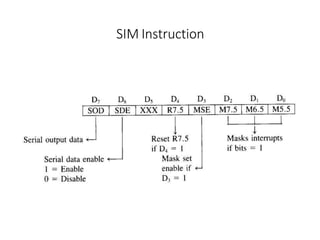

The document discusses the types of instructions in the 8085 microprocessor instruction set. It describes that the 8085 has 246 instructions that are classified into different types including data transfer instructions, arithmetic instructions, logical instructions, branching instructions, and control instructions. It provides details about common data transfer instructions like MOV, MVI, LXI, LDA, etc. and explains arithmetic instructions for addition, subtraction, increment, decrement. Logical instructions for AND, OR, XOR, rotate and compare are also covered.