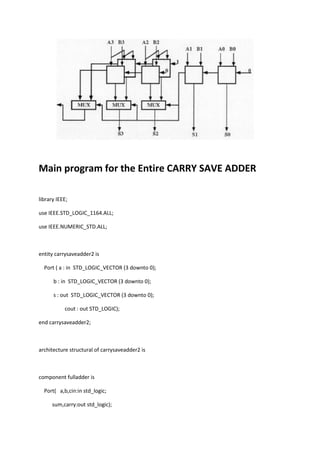

This document describes a carry save adder circuit implemented using VHDL. It contains the main program that instantiates full adder and multiplexer components. The full adder component performs addition and outputs the sum and carry. The multiplexer component selects between two inputs based on a selection signal. The carry save adder uses multiple full adders in parallel and multiplexers to select the carry outputs and generate the final sum.