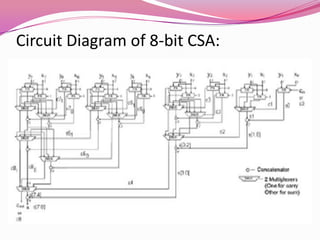

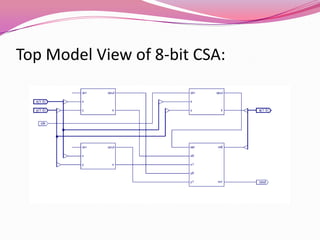

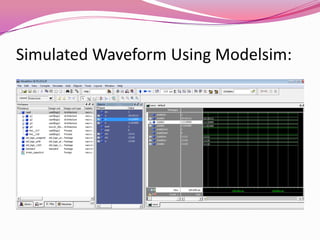

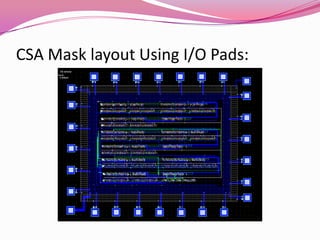

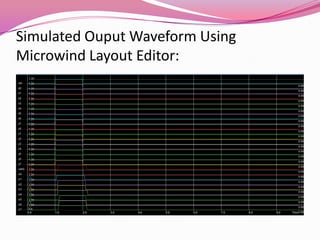

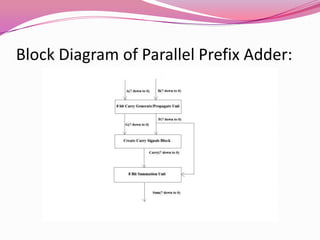

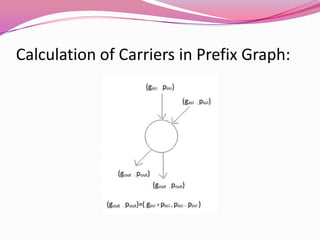

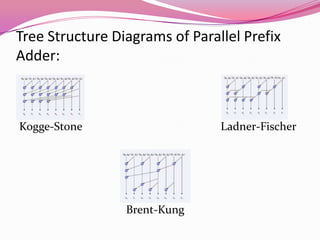

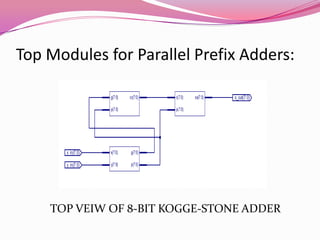

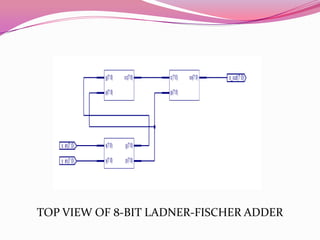

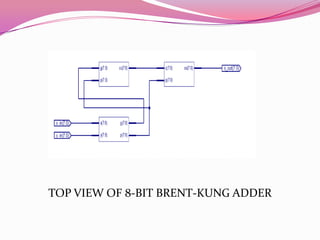

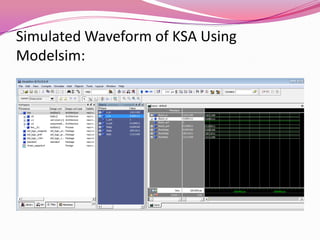

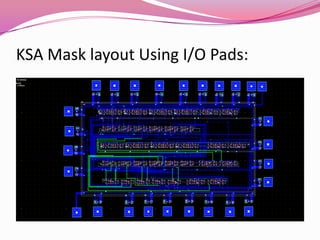

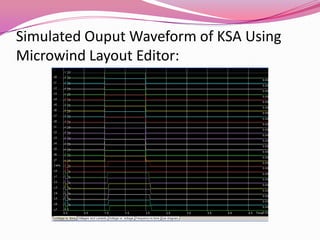

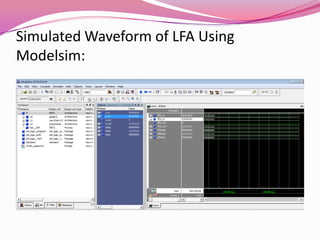

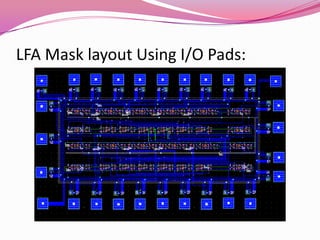

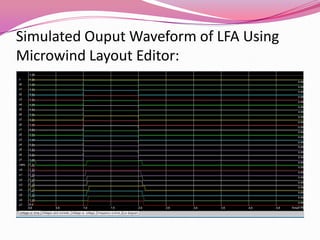

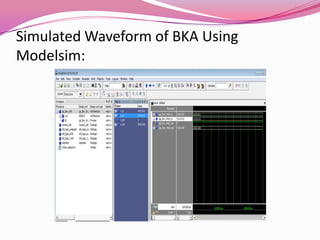

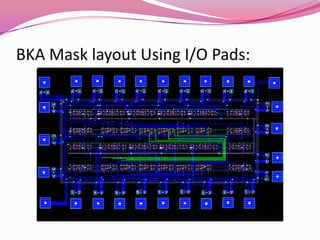

The document discusses the implementation of 8-bit conditional sum adders and parallel prefix adders for fast addition. It introduces conditional sum adders that generate output sums and carries assuming an input carry of 0 or 1. Parallel prefix adders perform addition in parallel using different tree structures, including Brent-Kung, Kogge-Stone, and Ladner-Fischer adders. Circuit diagrams, layouts, and simulated waveforms are presented for 8-bit implementations of conditional sum adders and each type of parallel prefix adder. Potential areas for expansion include higher radix adders.