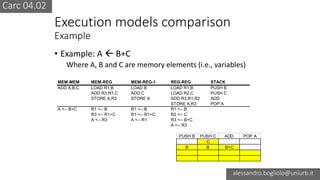

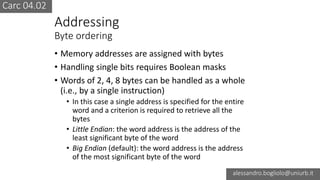

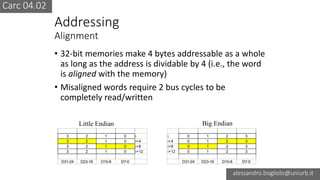

The document discusses various aspects of computer instruction-set architecture, including classification criteria, execution models, and addressing methods. It details RISC and CISC instruction sets, execution modes such as stack, memory-memory, memory-register, and register-register, as well as byte ordering and alignment in addressing. The document also explains different addressing techniques, such as direct, relative, and indirect addressing, in the context of instruction execution.

![Carc 04.02

alessandro.bogliolo@uniurb.it

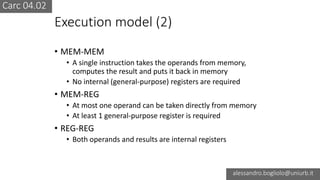

Addressing

Address computation

Direct

LD R1,var R1 M[var]

Relative to registers

LD R1,var(R2) R1 M[R2+var]

Indirect

LD R1,(R2) R1 M[R2]

Relative to registers, indexed and scaled

LD R1,var(R2)(RX)

R1 M[R2+var+RX*d]

var

(R2)

(R2)

var

var(R2)

(RX)*d

d](https://image.slidesharecdn.com/carc-04-02-170224100324/85/CArcMOOC-04-02-Instruction-Set-Architecture-9-320.jpg)