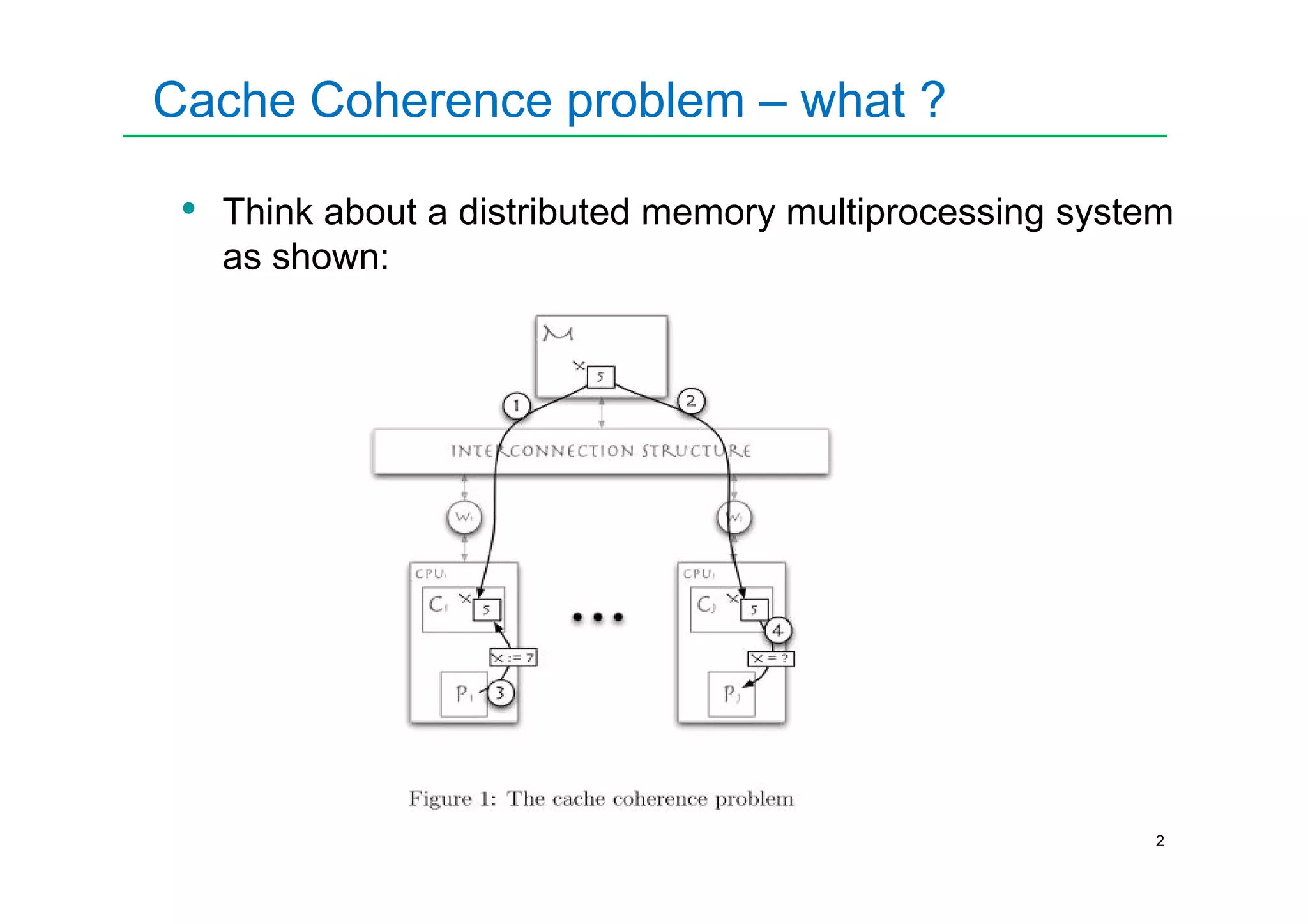

Cache coherence is a technique used in multiprocessing systems to maintain consistency between caches and shared memory. When a processor modifies a variable in its cache that is also stored in another processor's cache, inconsistency arises. There are three main techniques to maintain cache coherence: snoopy-based protocols invalidate or update other caches when a write is observed; directory-based protocols use a directory to control access to shared data and update or invalidate caches; and snarfing-based protocols allow caches to watch addresses and data to update copies when writes are seen. Cache coherence aims to ensure data consistency across caches for shared resources.