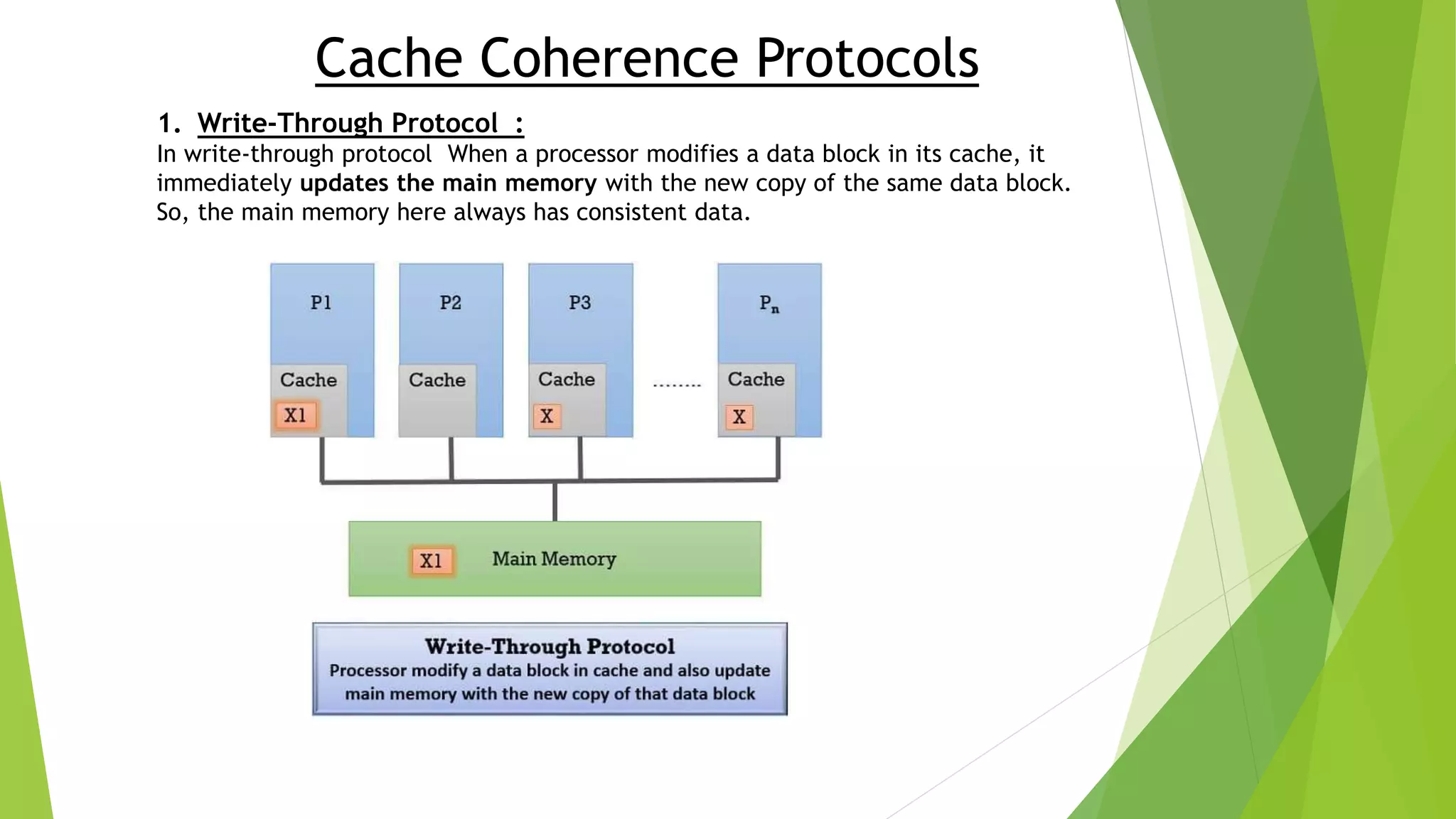

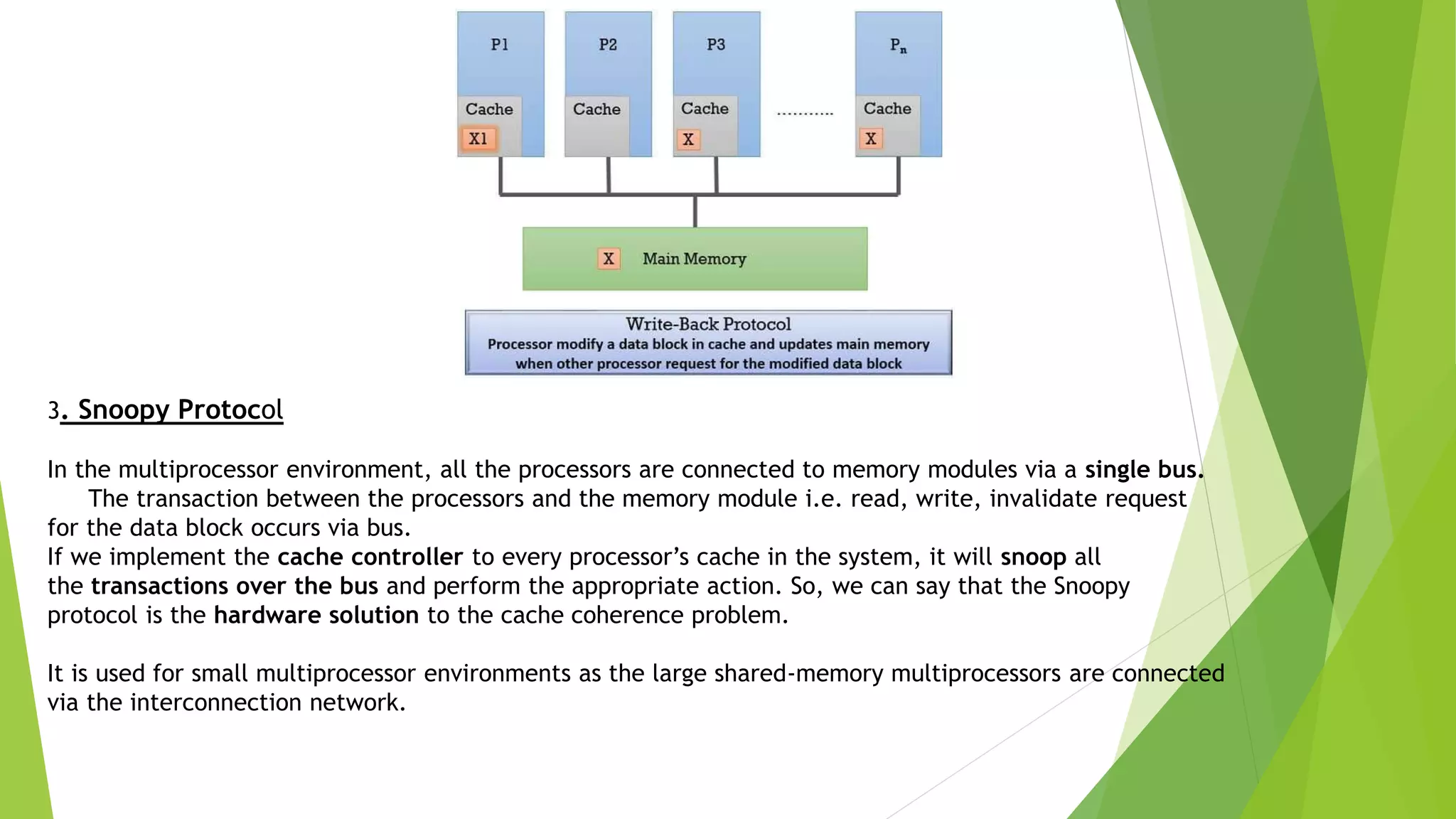

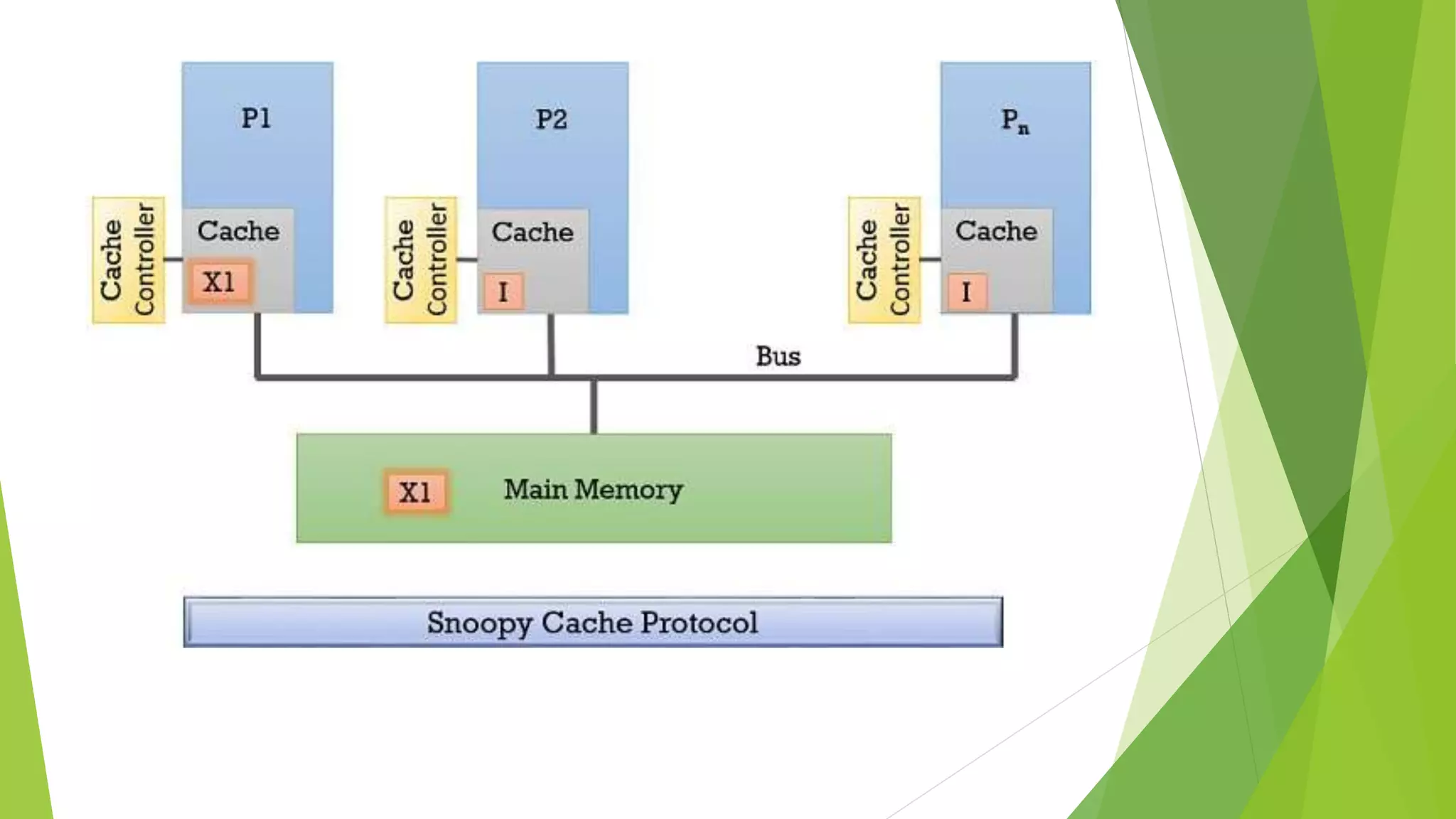

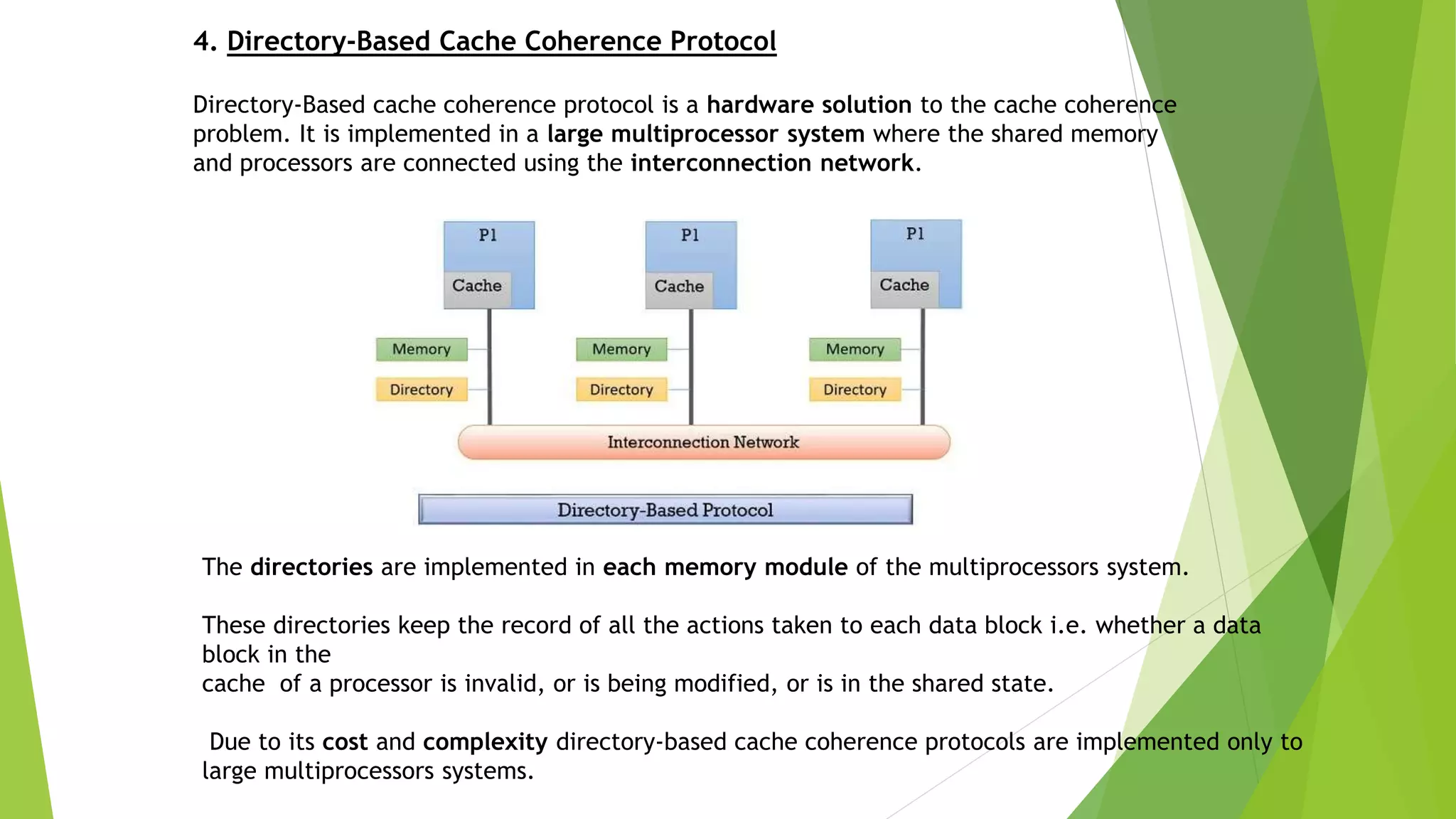

The document discusses cache coherence and different cache coherence protocols. Cache coherence is needed when multiple processor cores have their own caches to access shared memory. Incorrect execution could occur if the same data has different values in different caches. The document describes write-through, write-back, snoopy, and directory-based cache coherence protocols. Write-through updates memory on every write, while write-back only updates on cache eviction. Snoopy protocol uses a shared bus to monitor transactions. Directory-based protocol uses directories in memory to track the state of each block in large multiprocessor systems.