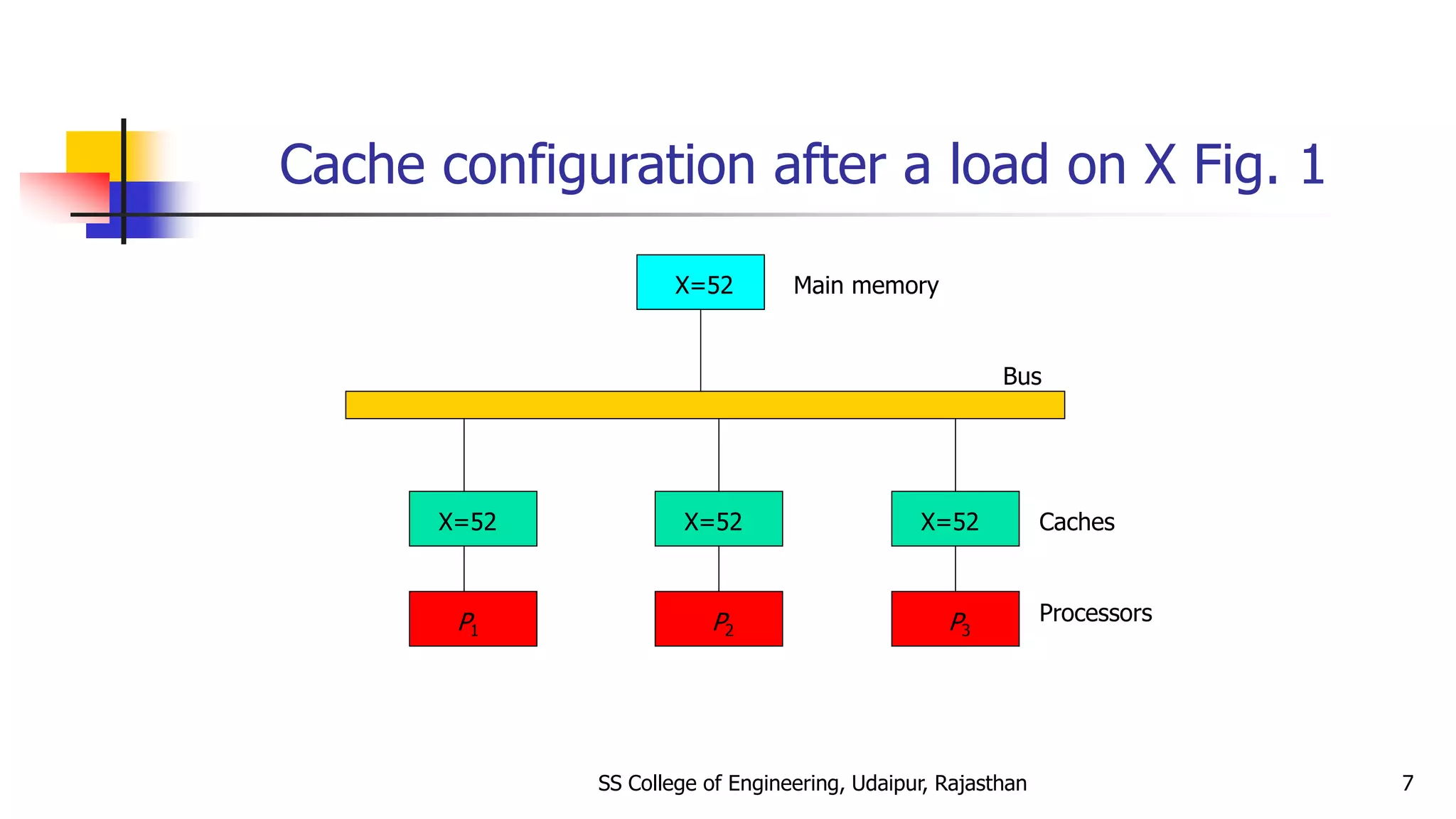

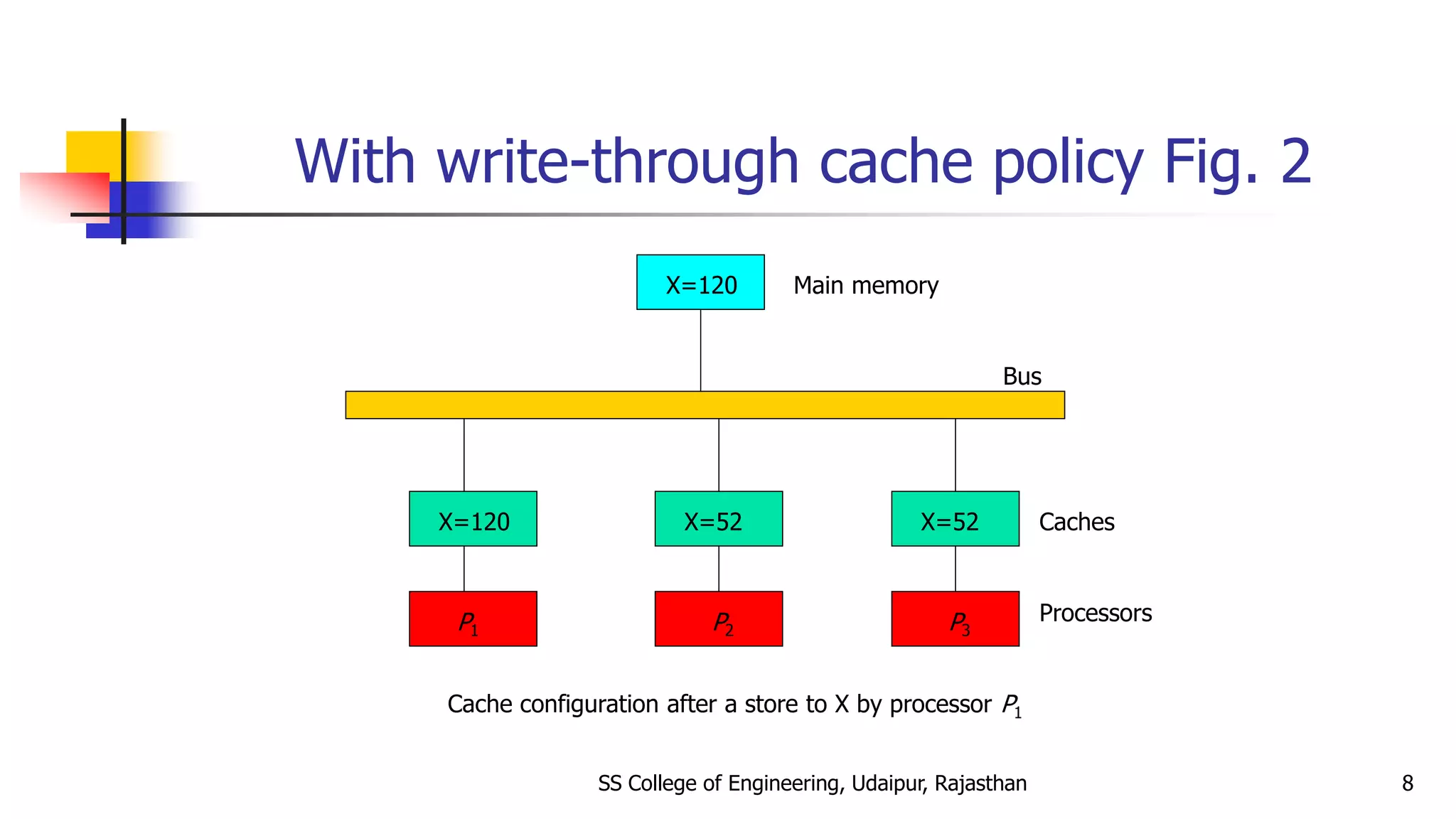

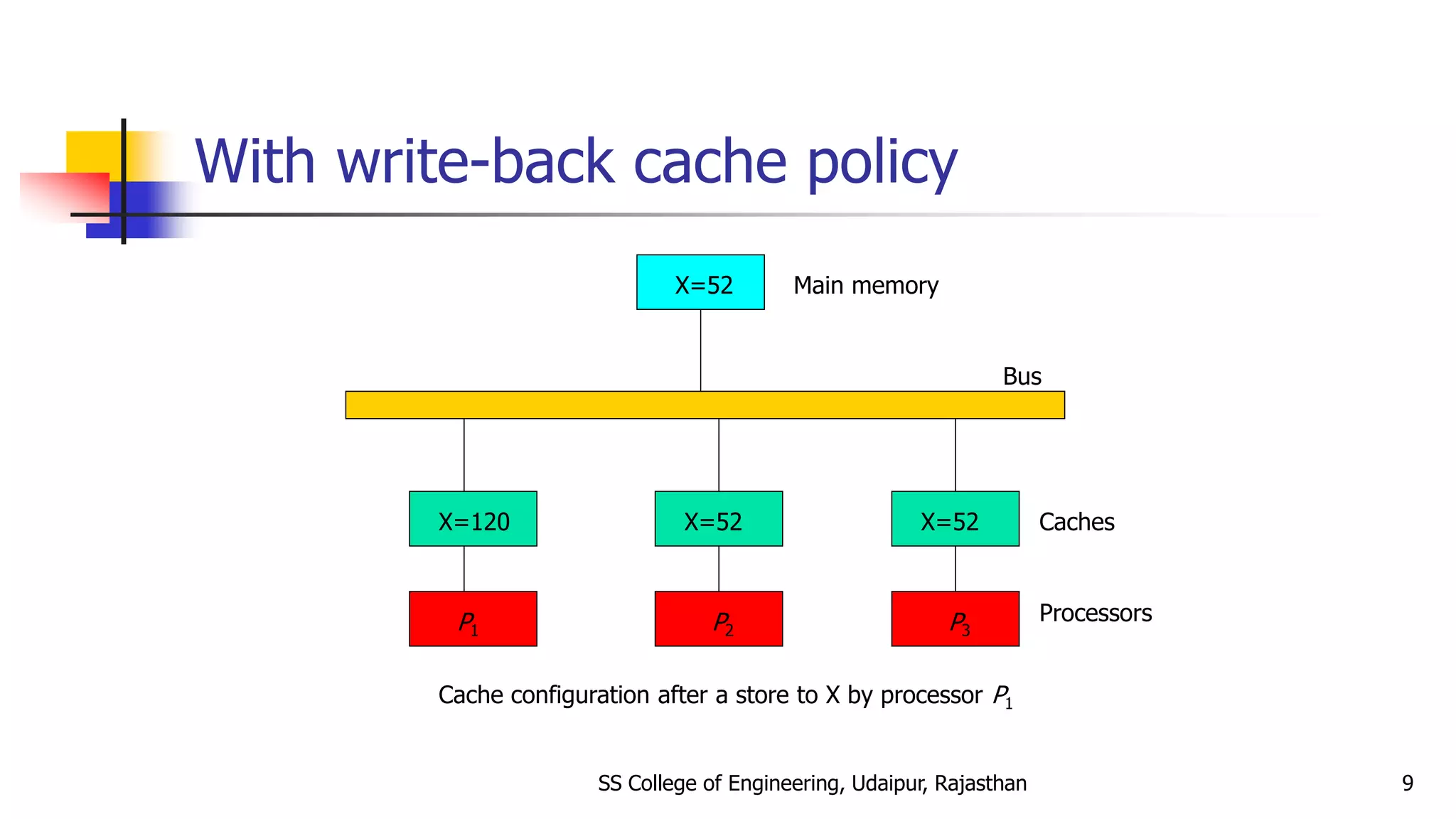

This document discusses cache coherence in multiprocessor systems. It describes how inconsistent copies of data in caches can occur and violate coherence. Two main solutions are described: 1) using a shared cache or disallowing private caches to avoid inconsistent copies, and 2) employing snoopy cache controllers and a directory-based coherence protocol to monitor memory accesses and invalidate stale cache lines to ensure consistent views of shared data across processors. The document provides examples of how coherence issues can arise and explains the basic mechanisms of snoopy and directory-based cache coherence.