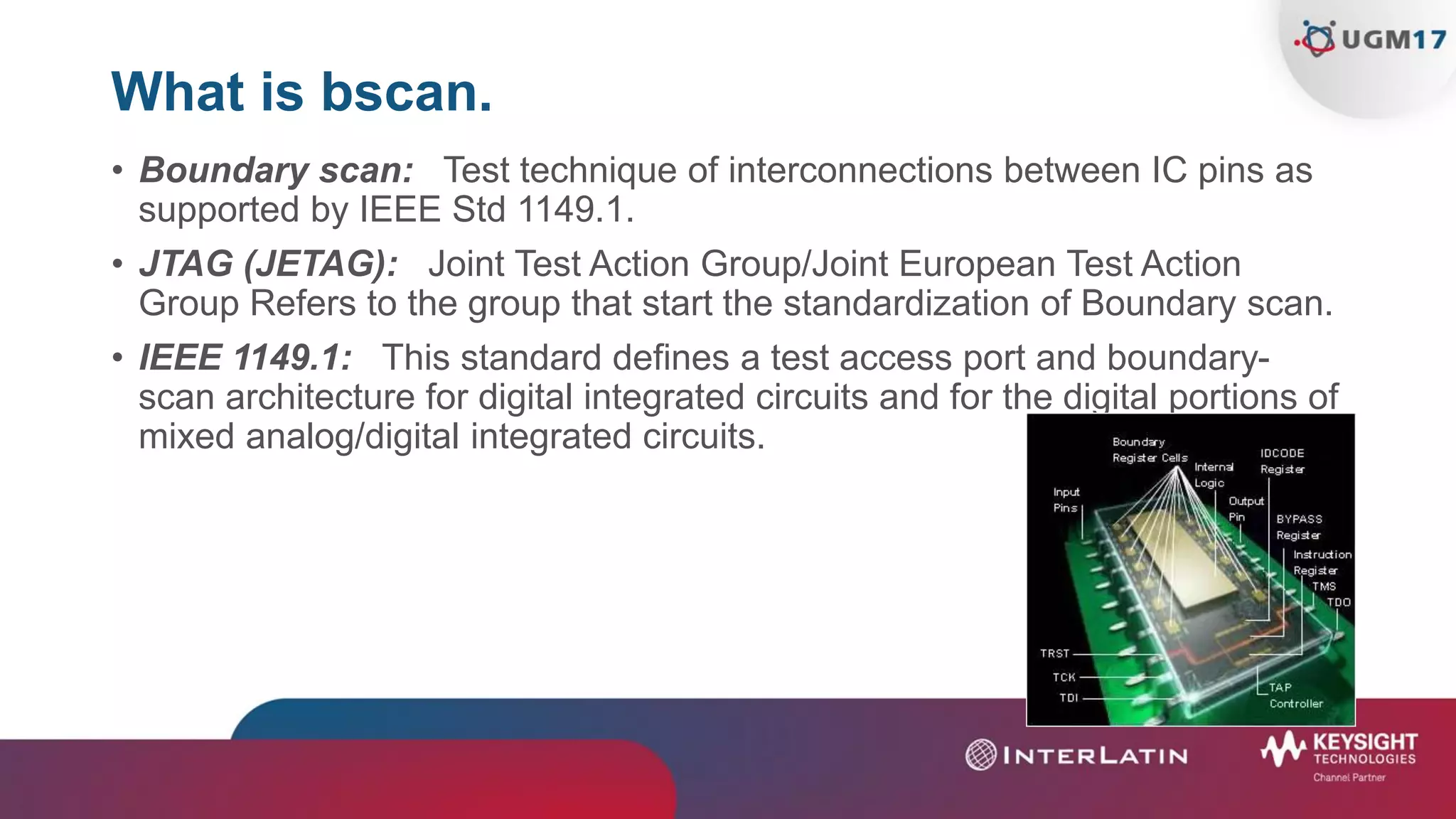

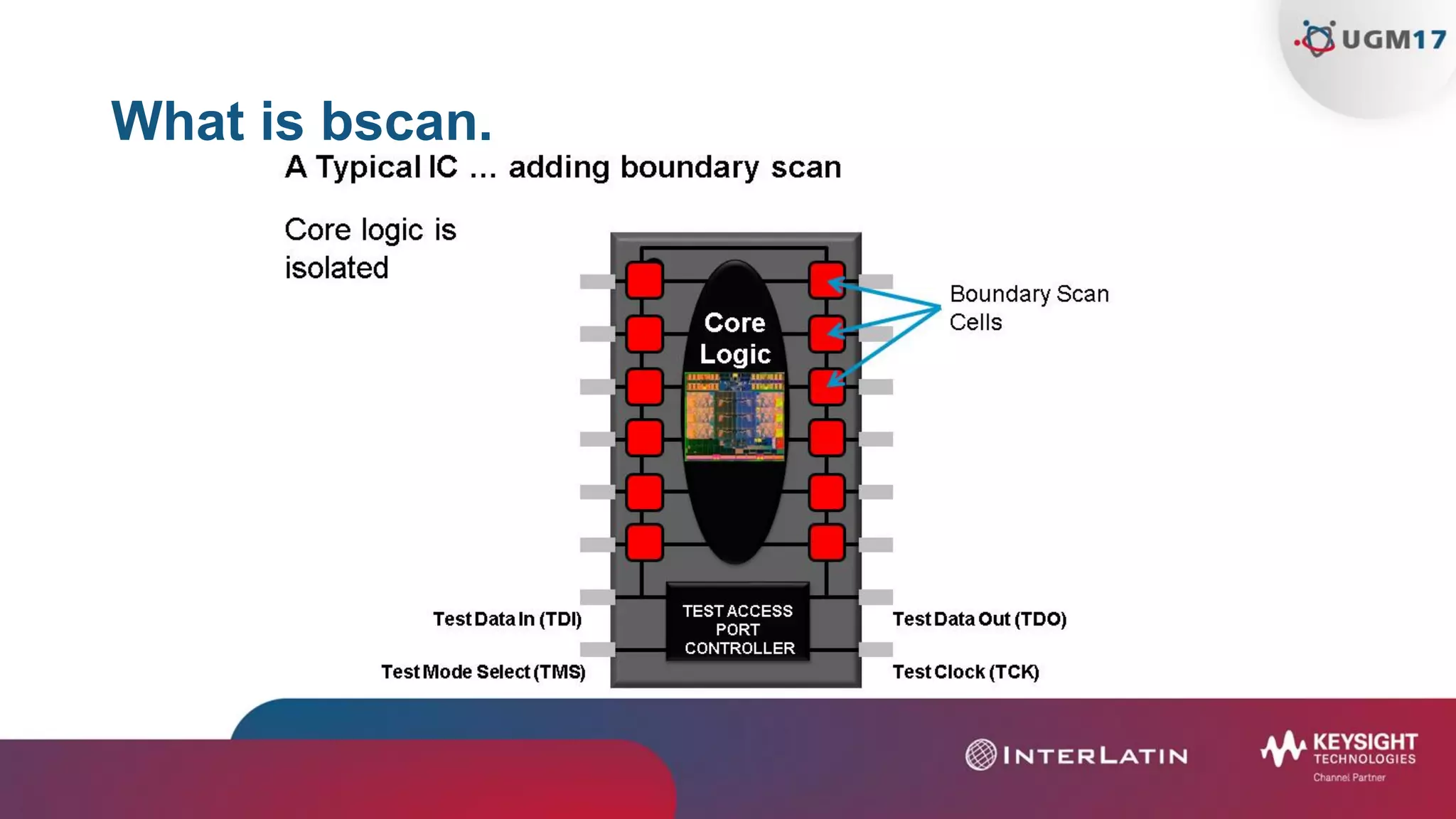

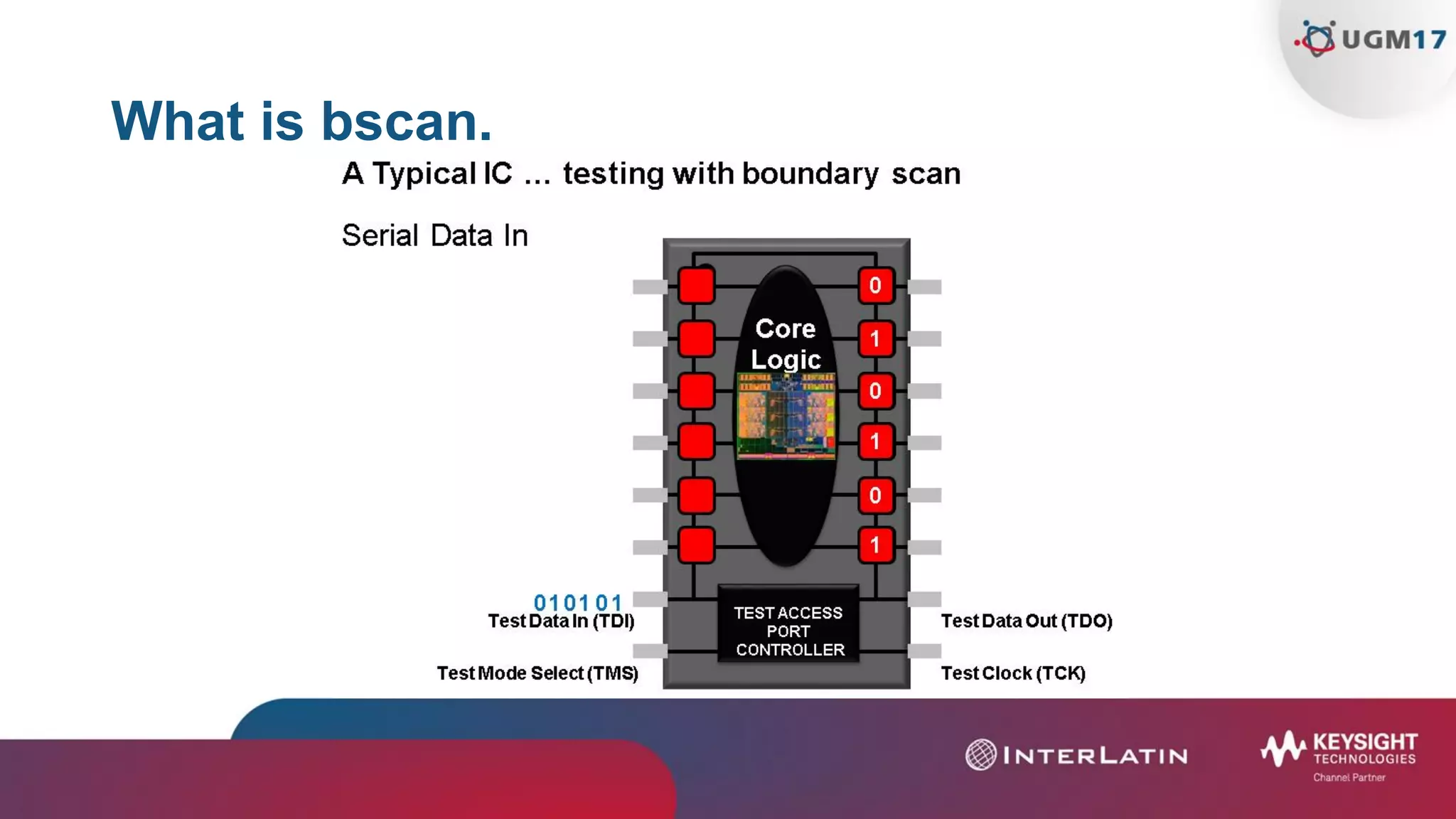

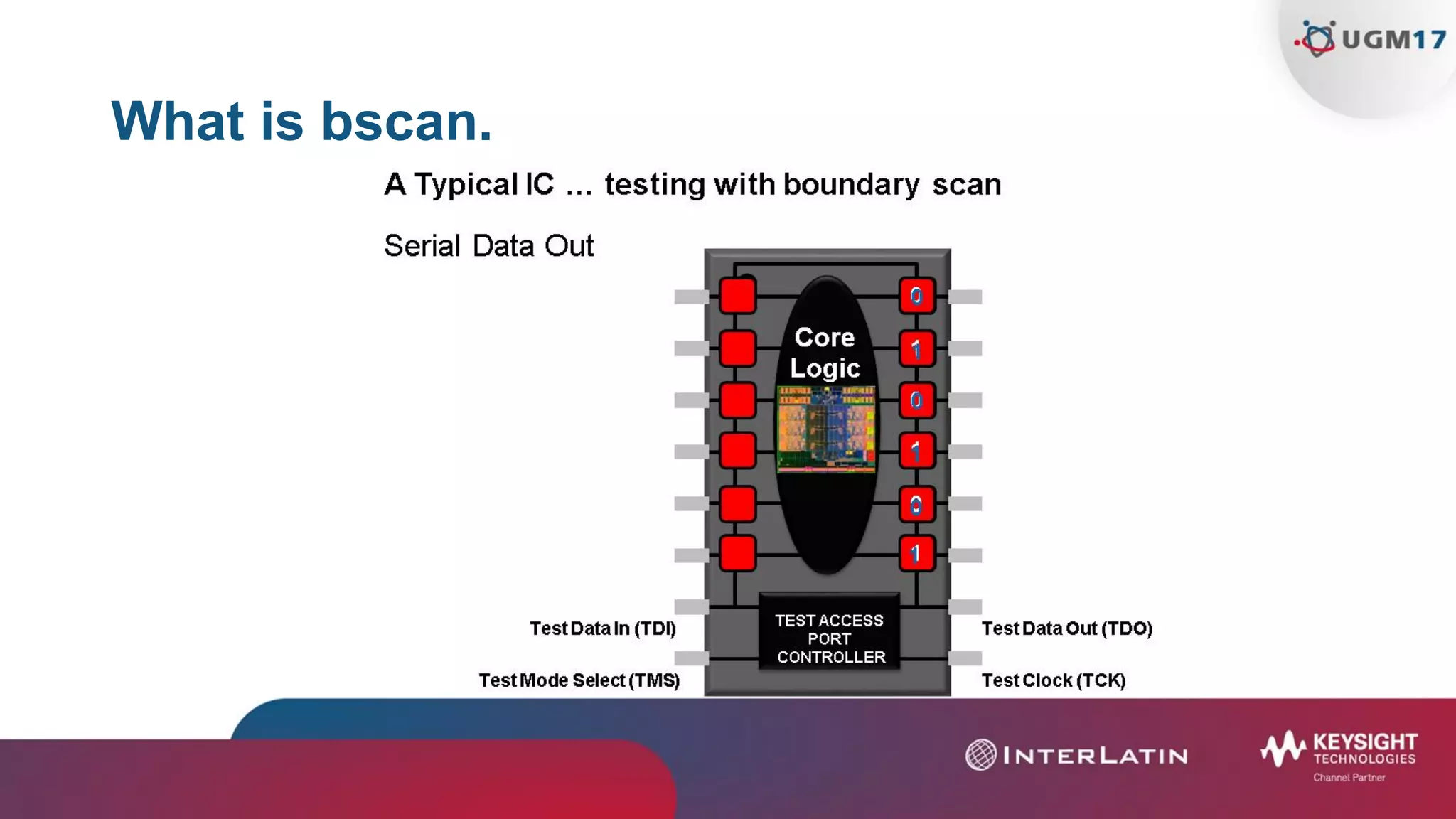

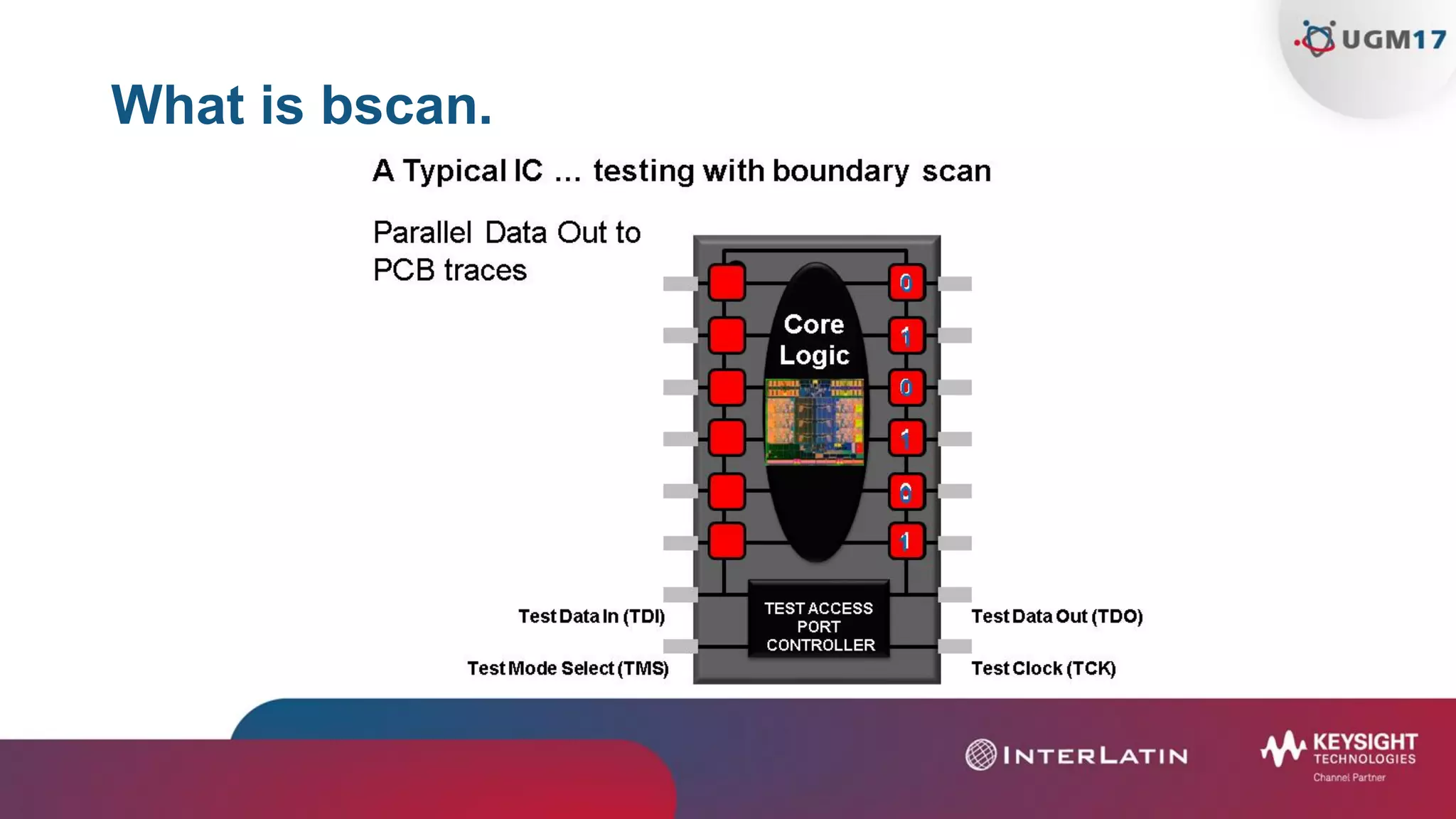

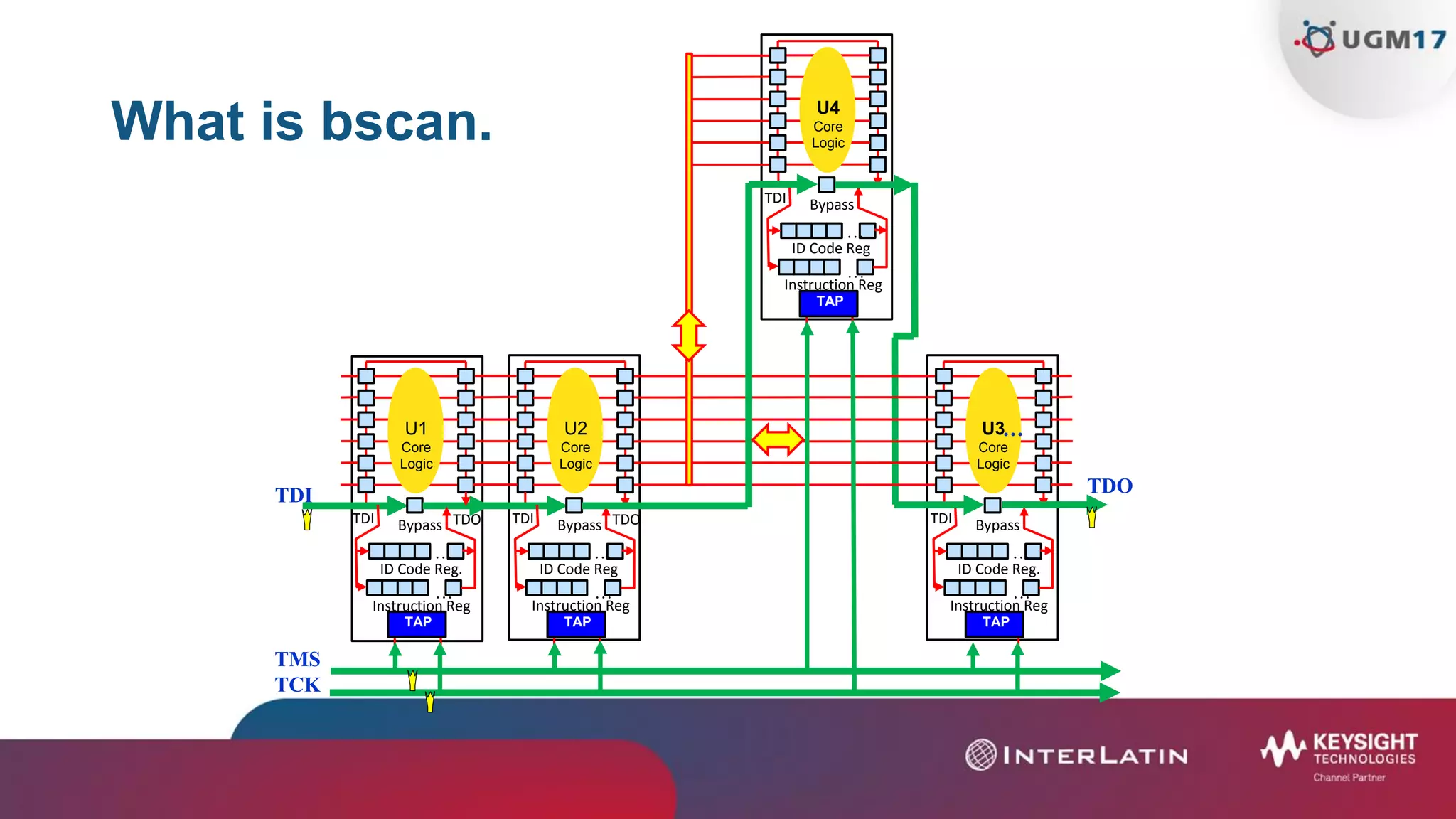

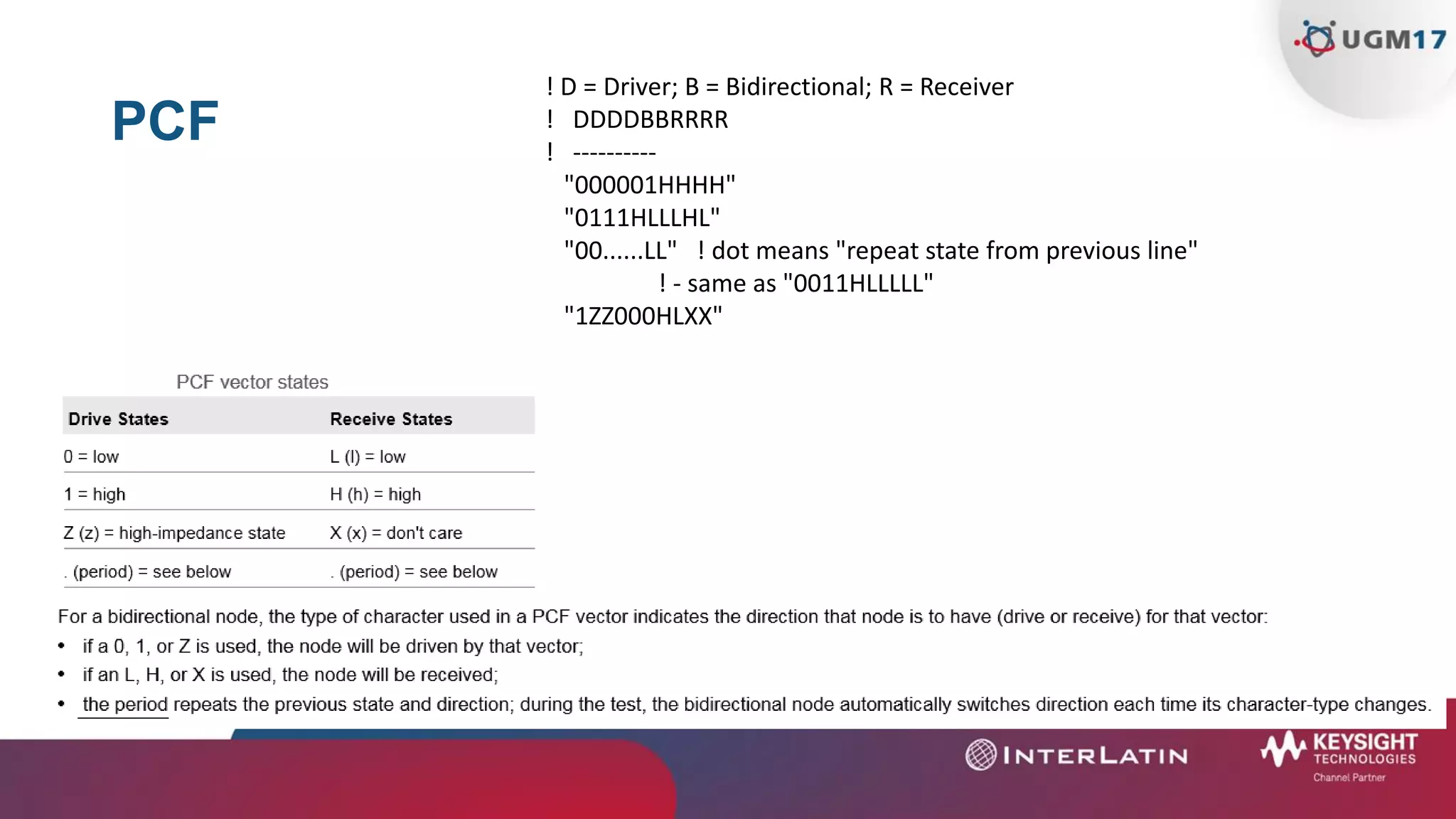

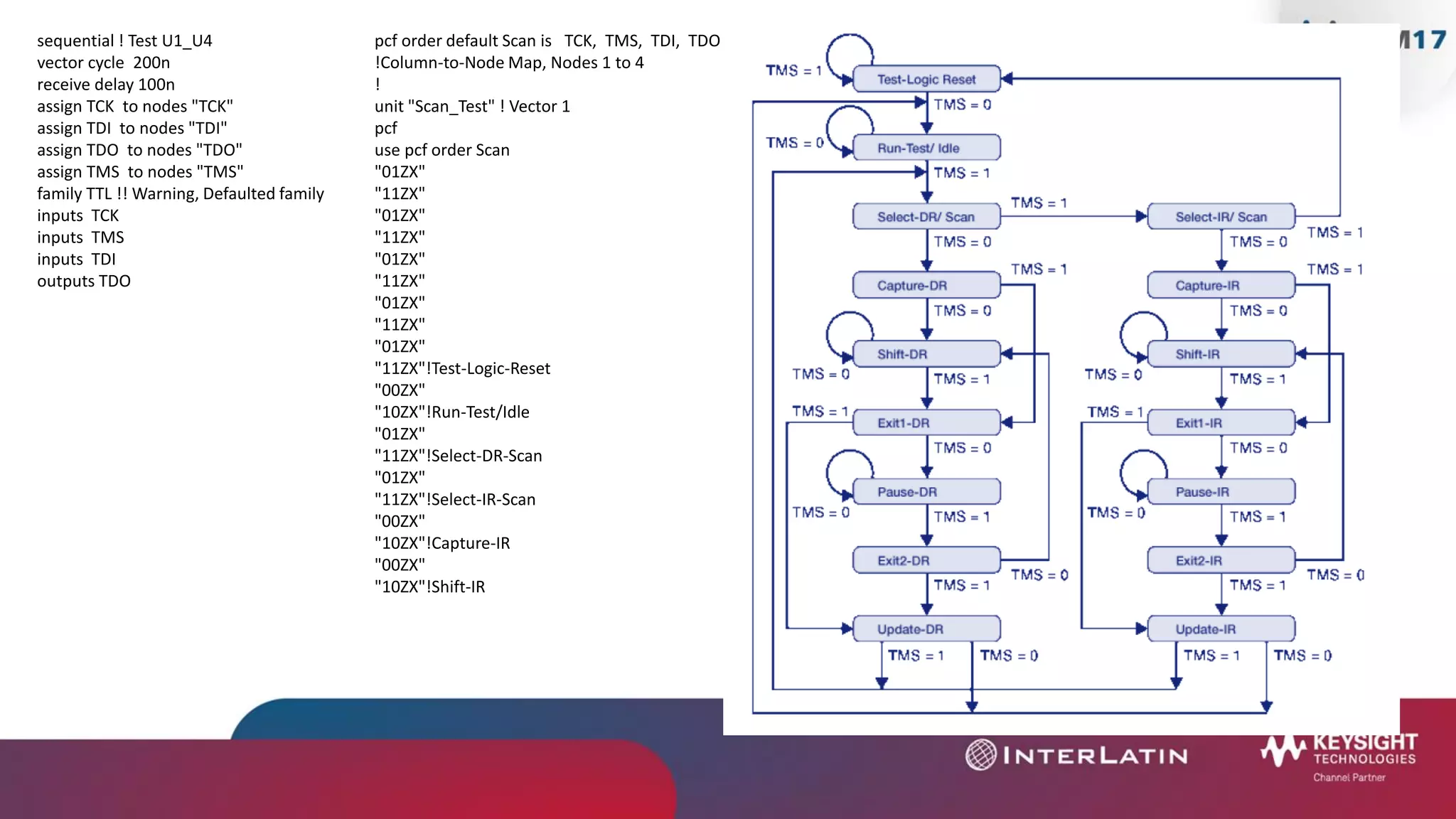

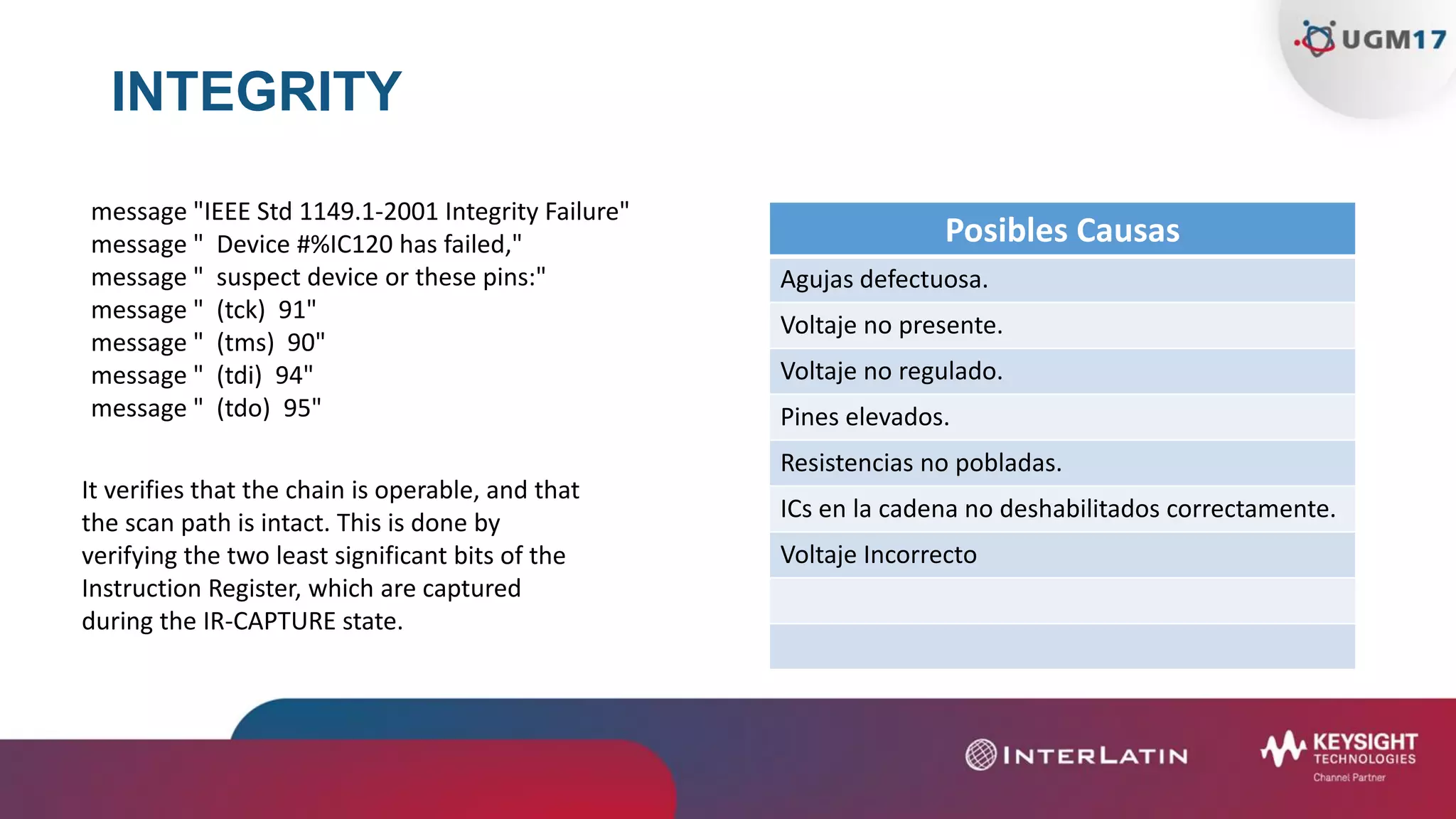

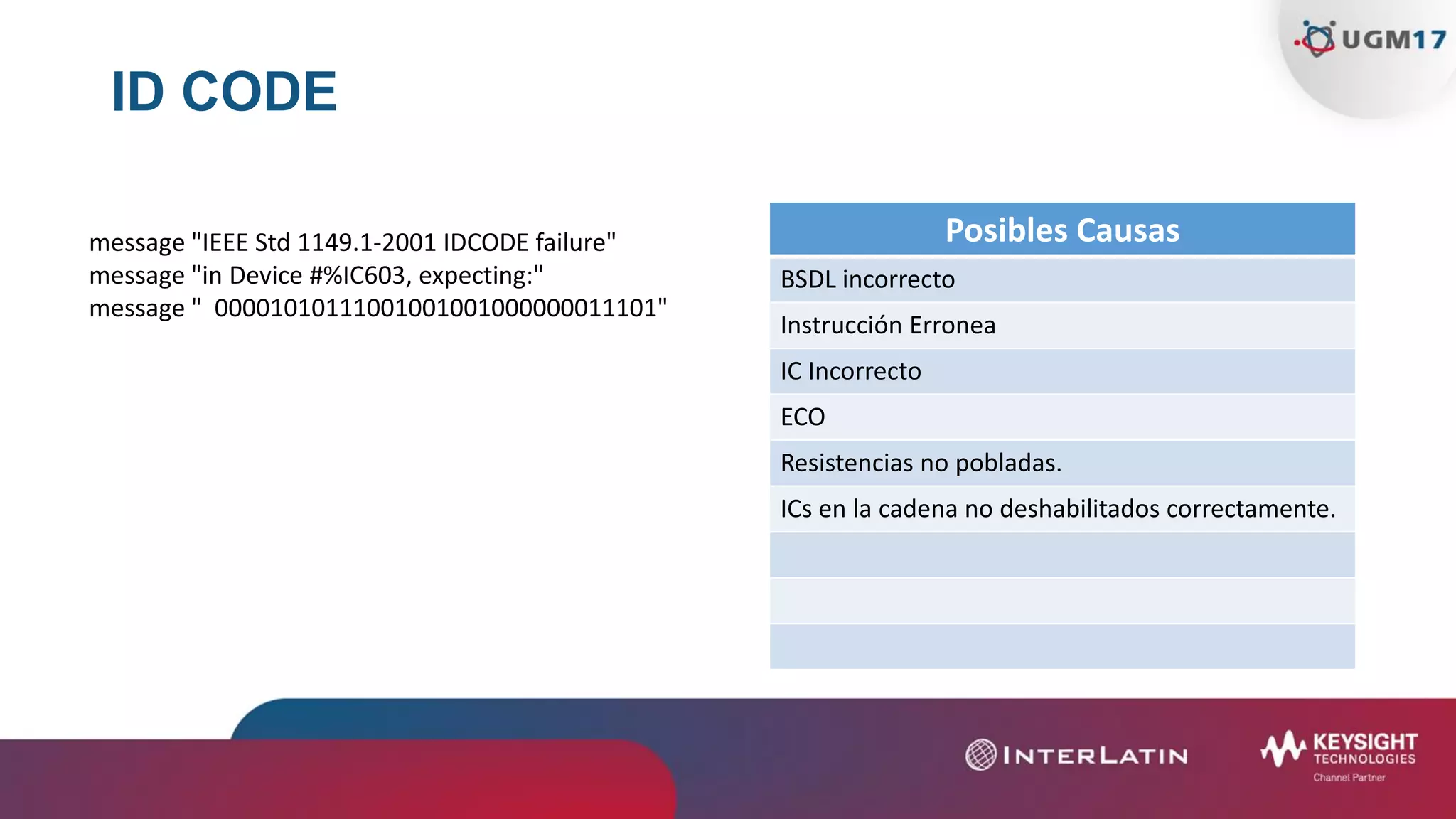

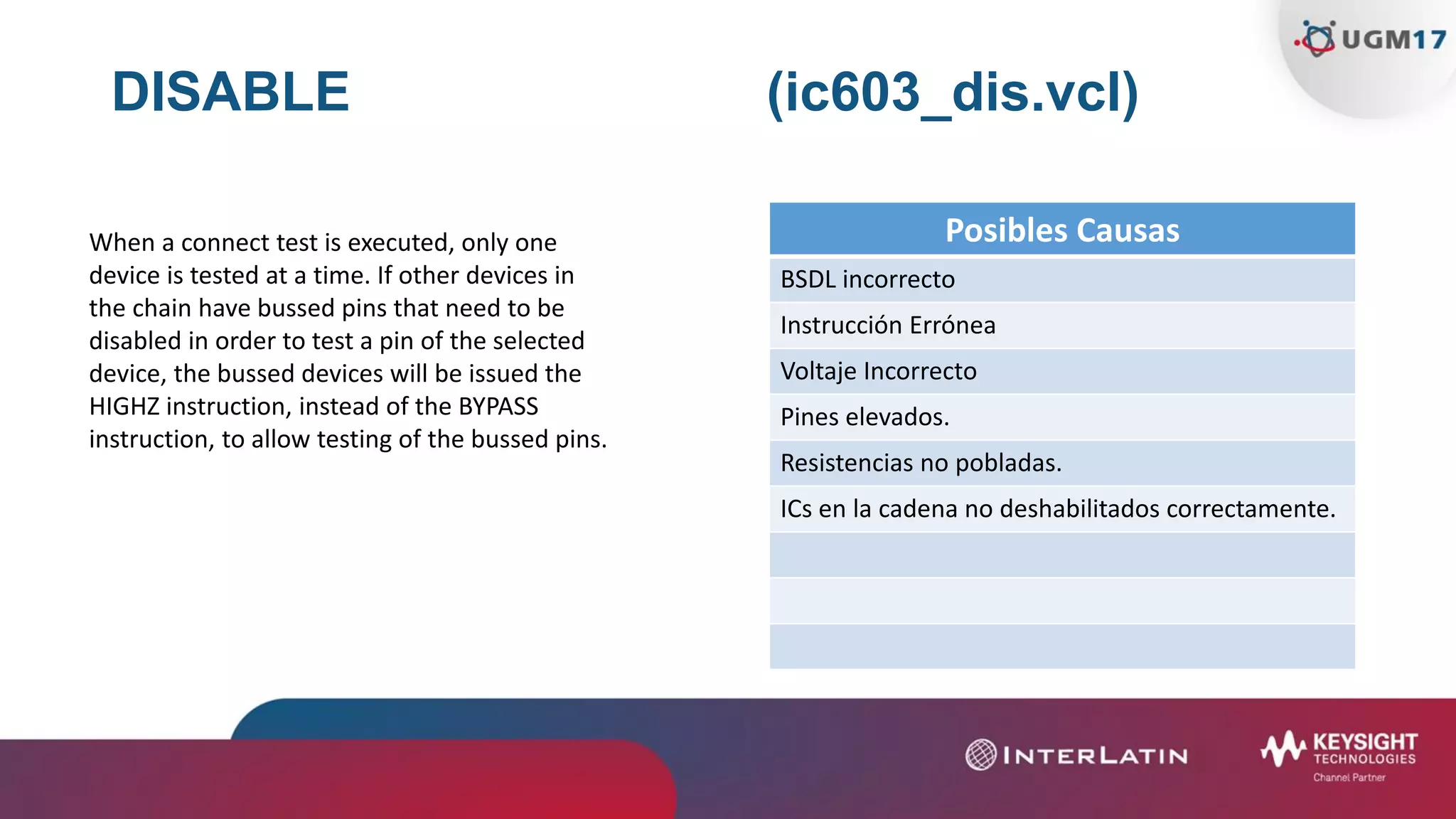

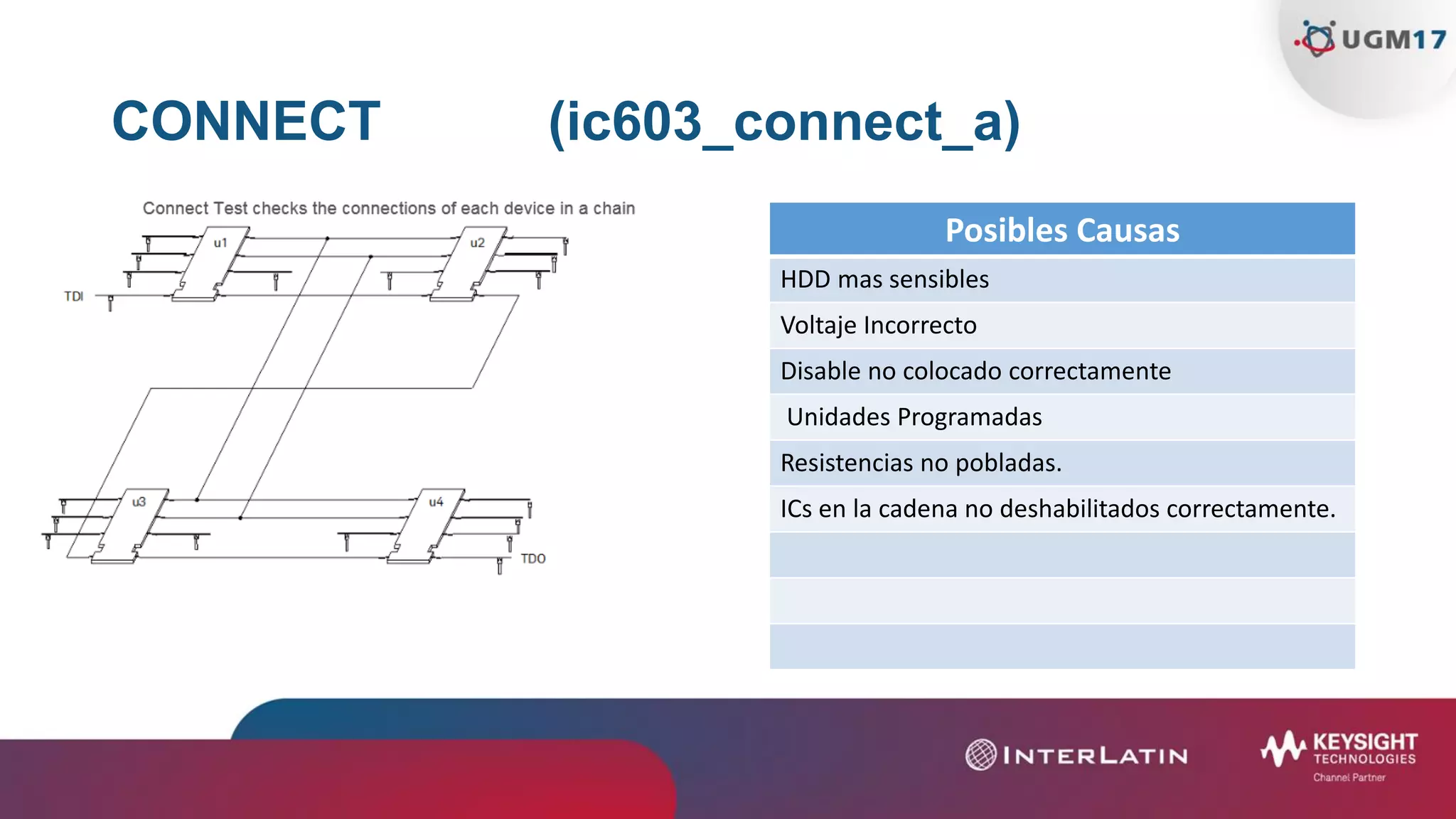

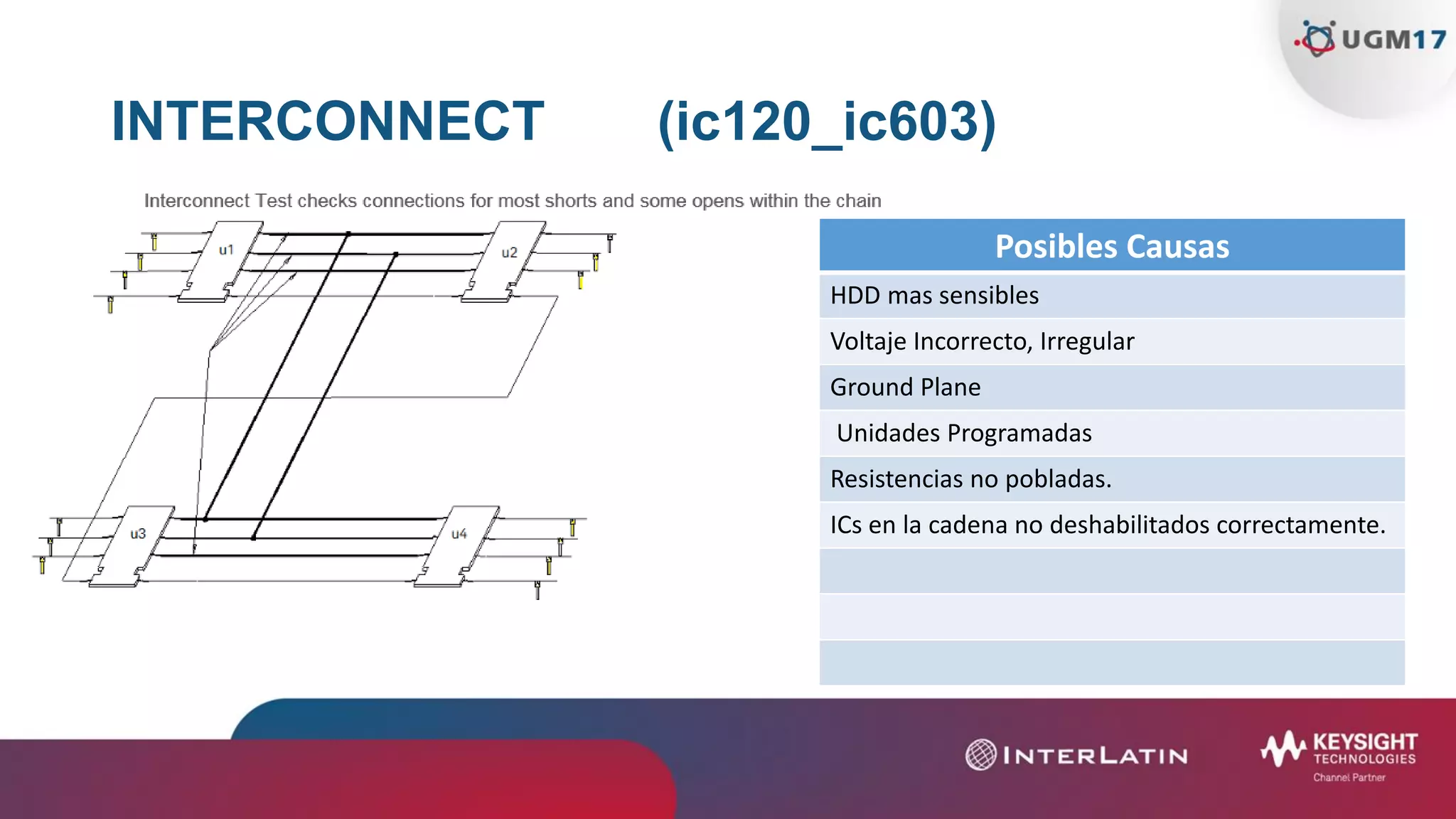

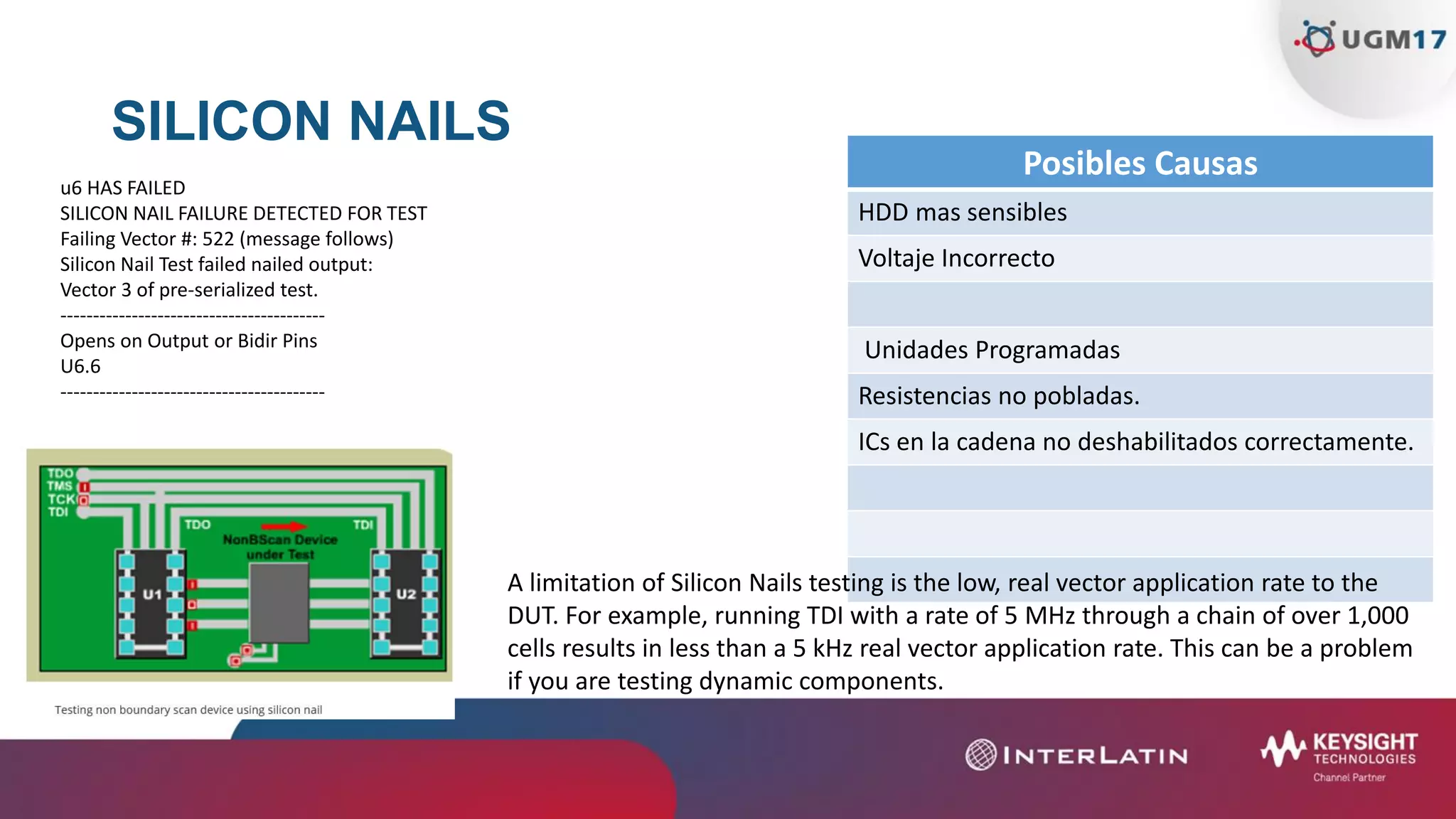

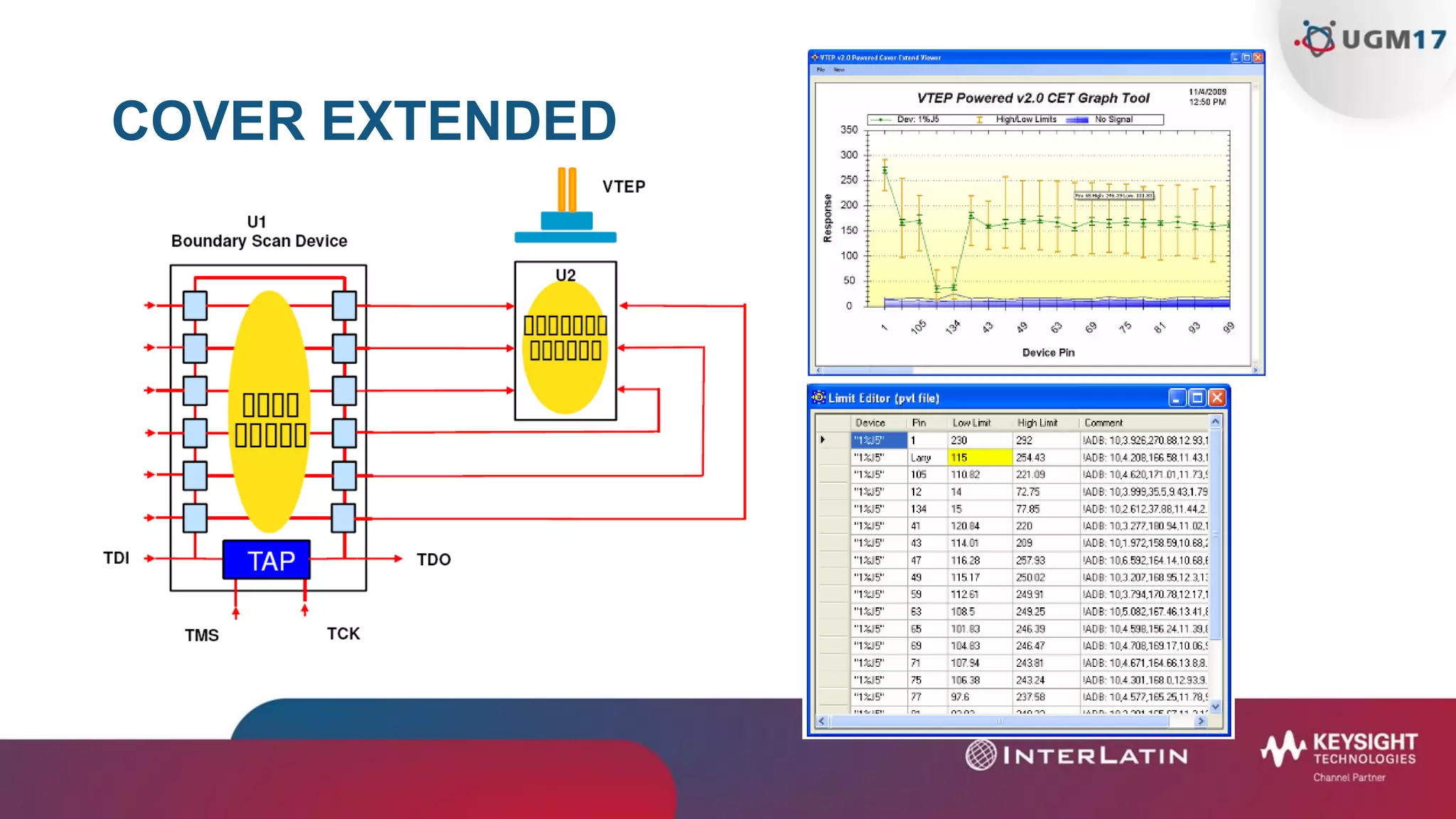

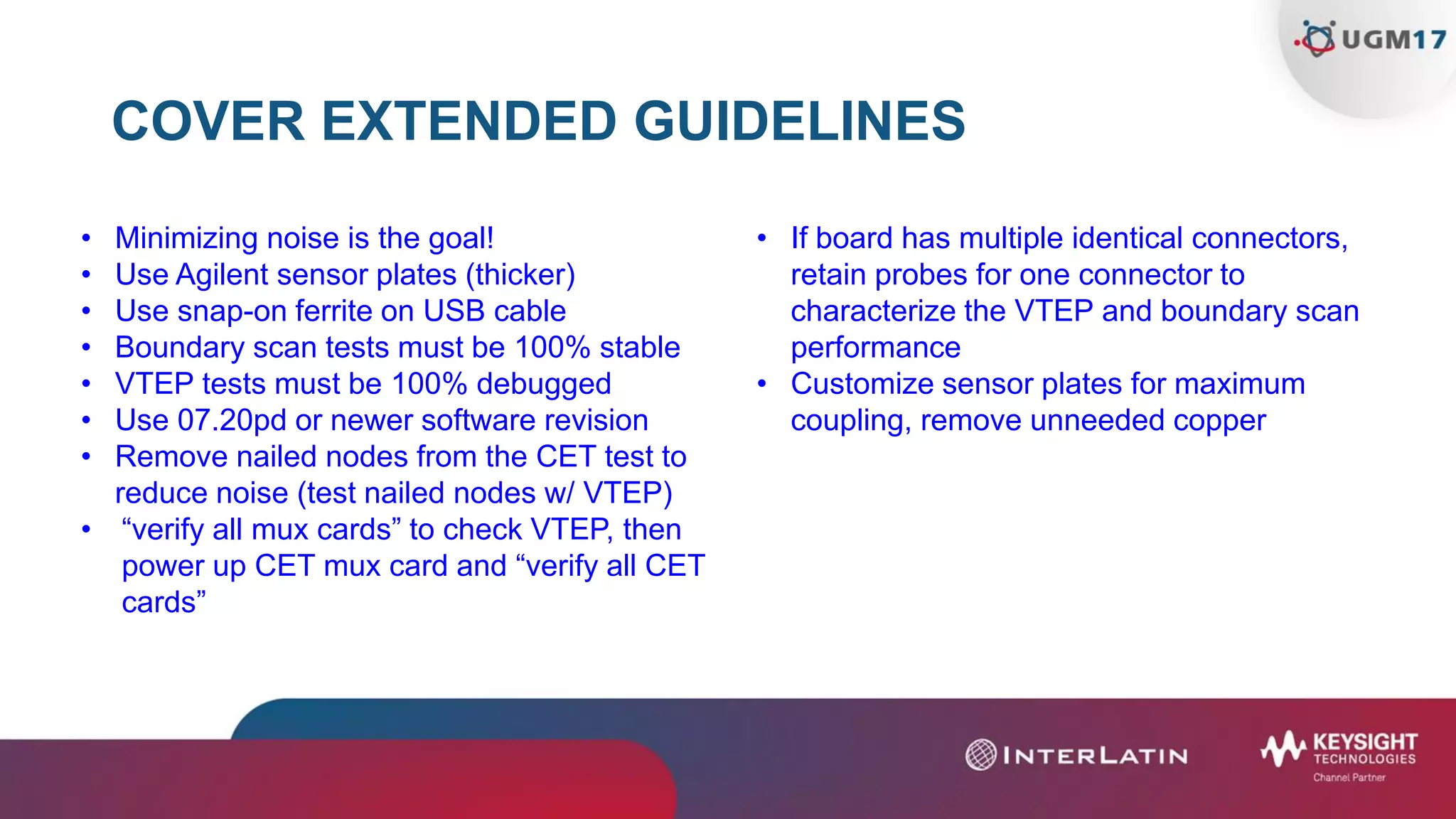

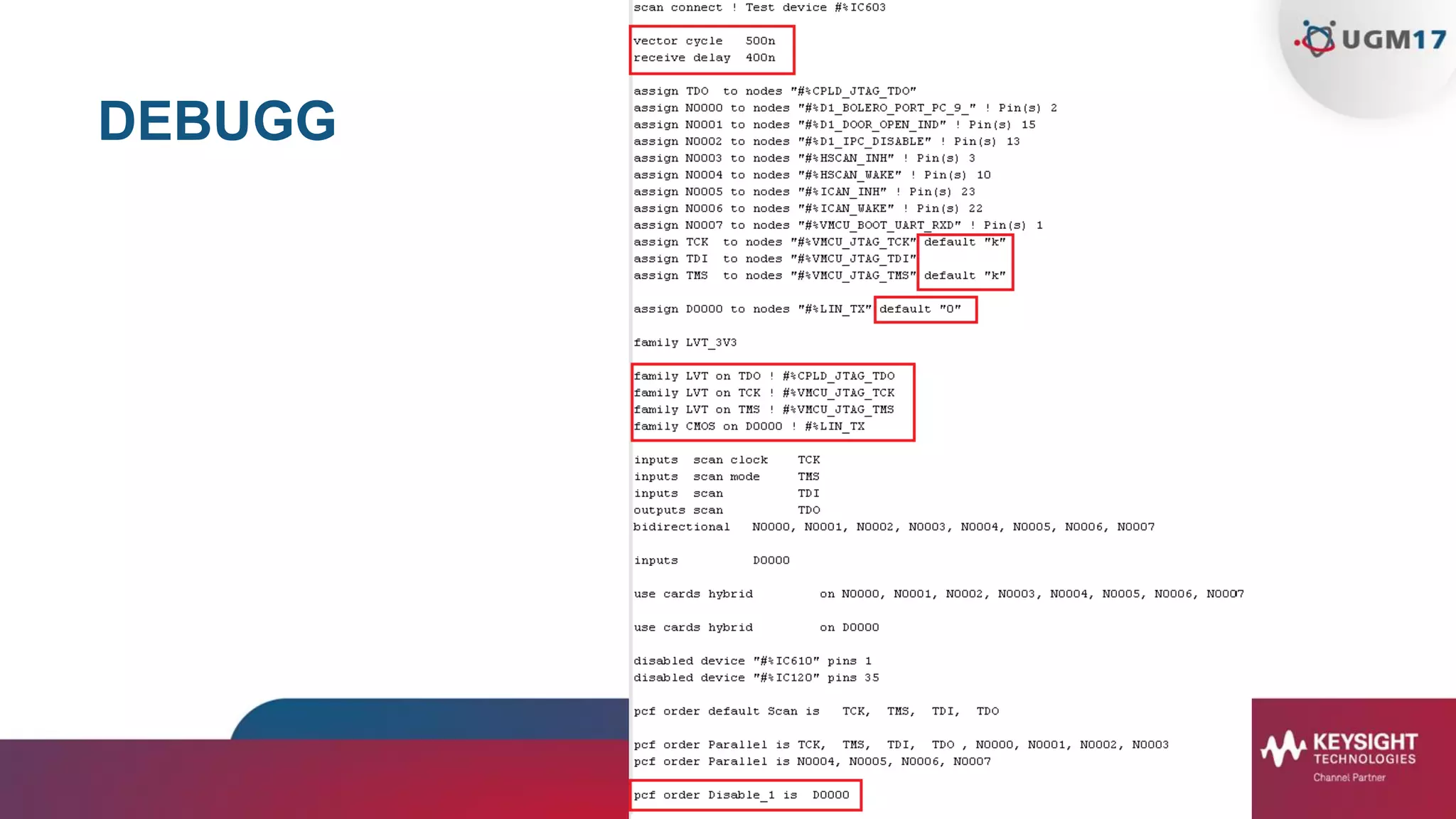

The document provides a comprehensive overview of boundary scan (BSCAN) testing, emphasizing its application in verifying digital integrated circuits per IEEE standard 1149.1. It outlines the types of BSCAN tests, common failures, and troubleshooting tips, including potential causes and error messages for various failure scenarios. Additionally, it includes guidelines for effective BSCAN test execution and considerations for minimizing noise during tests.