The document contains examples and solutions to problems involving boolean algebra, combinational logic circuits, binary number systems, and basic digital logic components like flip-flops. Some key points:

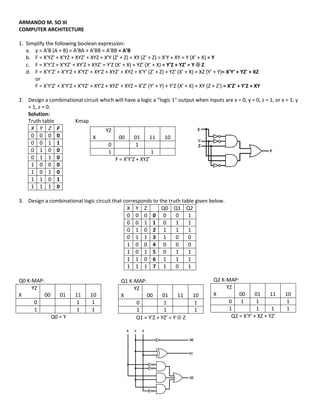

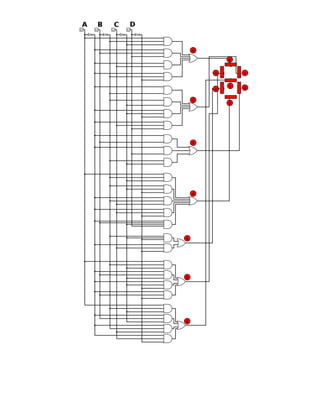

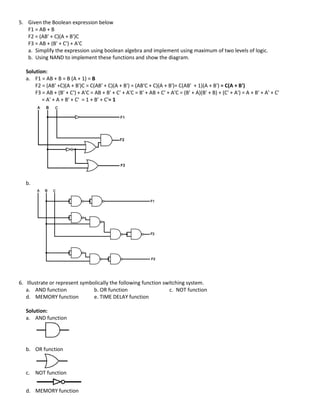

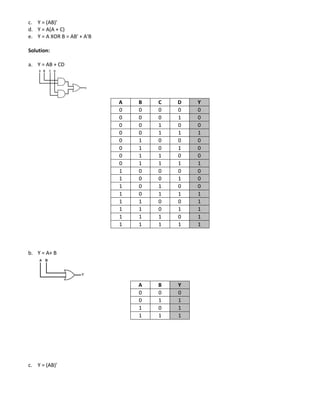

- It provides solutions to simplifying boolean expressions and designing combinational logic circuits from truth tables.

- Examples are given for binary coded decimal to seven segment decoding and frequency point calculations based on input frequency division.

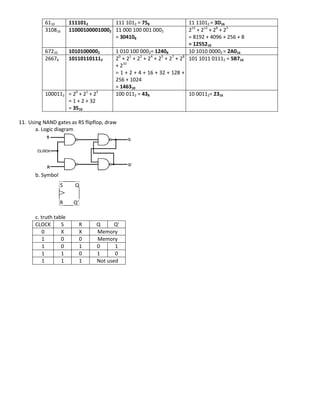

- Conversions between binary, decimal, and hexadecimal number systems are demonstrated.

- The logic diagram, symbol, and truth table for an RS flip-flop implemented with NAND gates is illustrated.