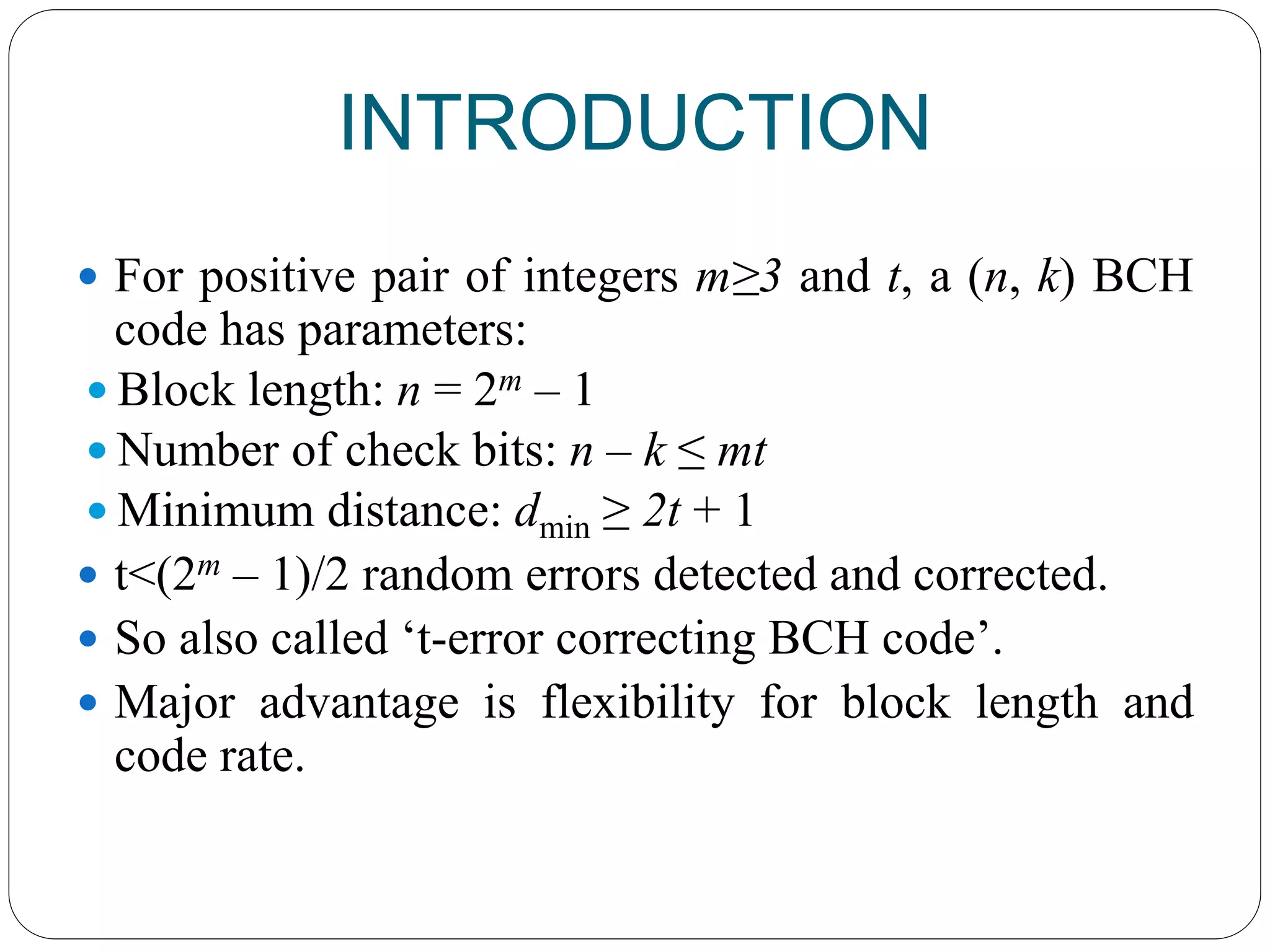

BCH codes are powerful cyclic error-correcting codes used to detect and correct multiple random errors in digital communications, characterized by flexible block lengths and control over code rate. They were discovered in the late 1950s and are particularly effective due to simple decoding methods, yet they can be complex to implement. Applications include satellite communications, digital media storage, and industry standards for video coding and data transmission.