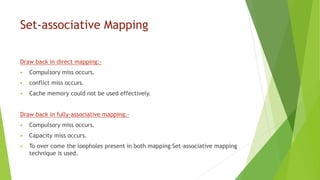

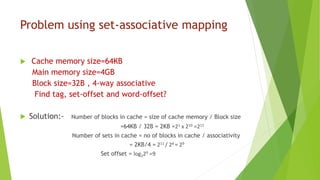

The document discusses cache memory mapping techniques, specifically fully-associative and set-associative mappings, highlighting their advantages and drawbacks, such as conflict and capacity misses. It outlines the calculations necessary for determining tag, set-offset, and word-offset, using a specific cache size example with various associations. The document also includes details on tag-directory size computation based on given parameters.

![Tag-directory size computation

Tag-directory size = Tag x number of blocks

=18 x 211

= 36 x 210

= 36B

Tag-directory size= (tag + number of extra bits given) x (number of blocks)

[if in question it is given that number of dirty_bits=1 and number of modified

bit =2]

Tag-directory size = (18 + 1+ 2) x 211

= 21 x211

= 42 x 2 10

= 42KB](https://image.slidesharecdn.com/associativememoryandset-associativememorymapping-210806162757/85/Associative-memory-and-set-associative-memory-mapping-8-320.jpg)