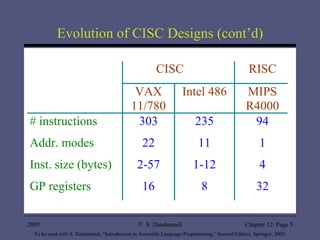

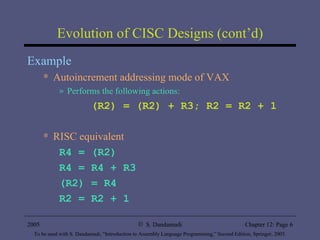

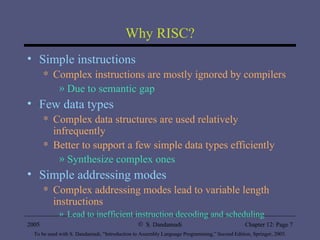

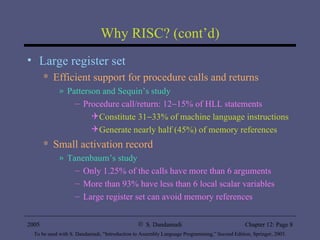

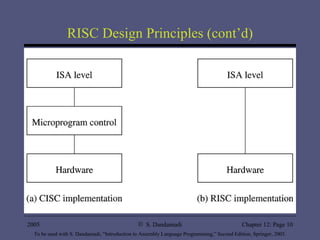

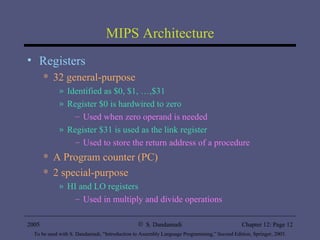

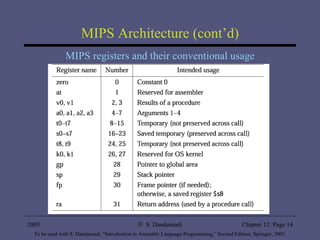

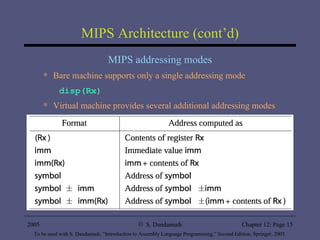

The document discusses the evolution of CISC and RISC processor designs. It outlines the key principles of RISC design including simple instructions, register-to-register operations, simple addressing modes, and fixed-length instructions. It then describes the MIPS architecture, which implements RISC design principles with 32 general-purpose registers, a fixed instruction length, and register-based operations with limited addressing modes.