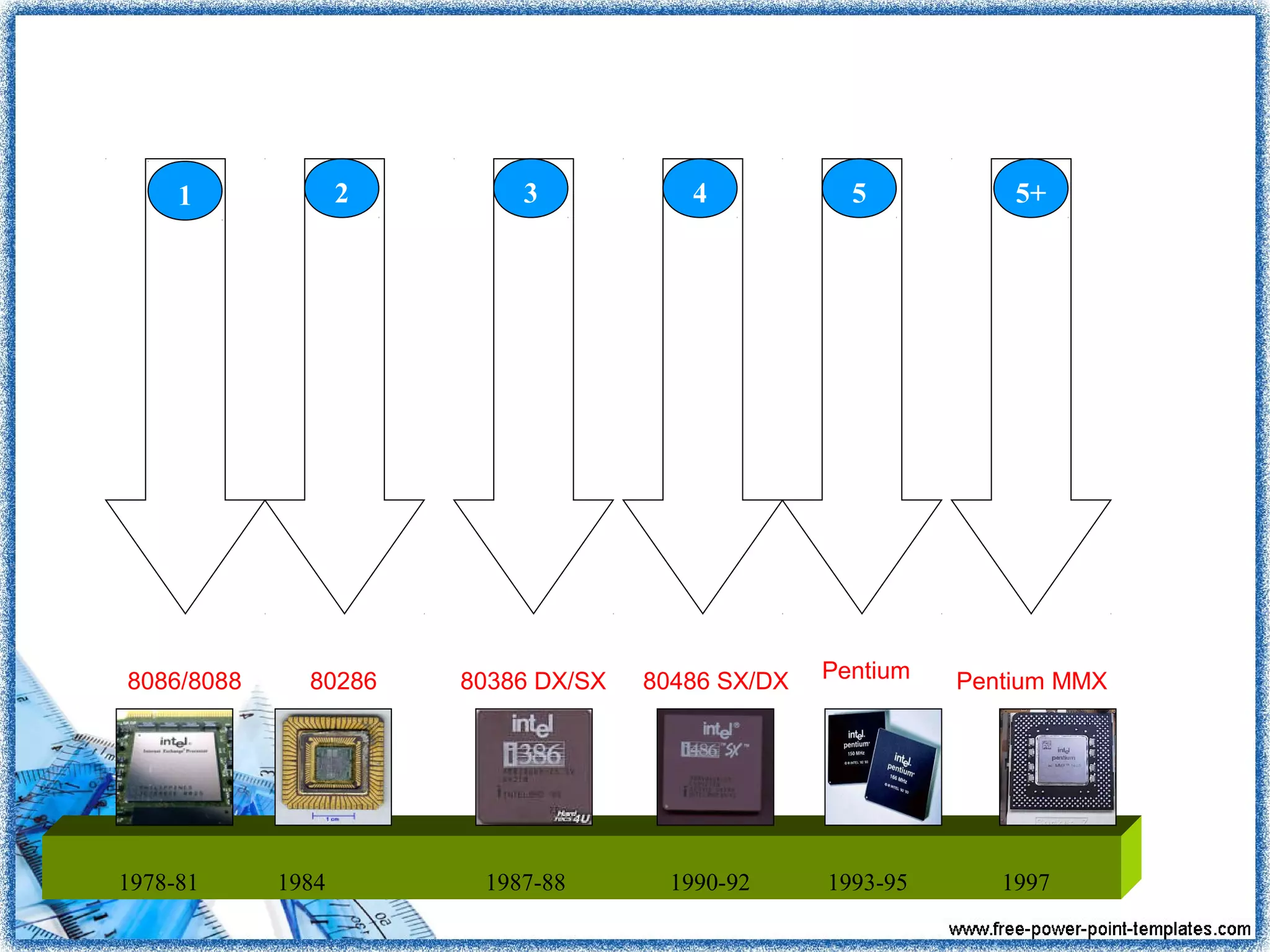

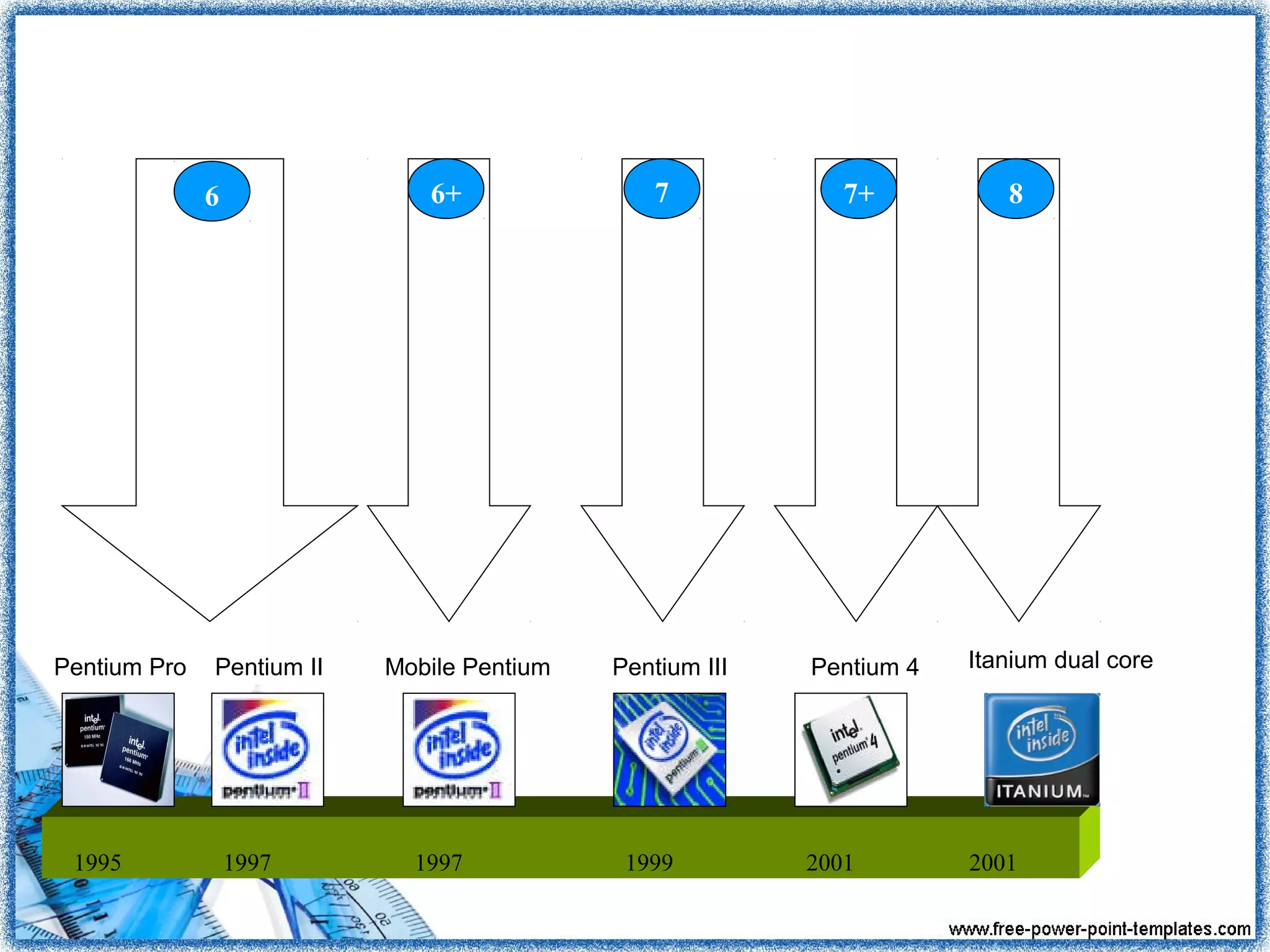

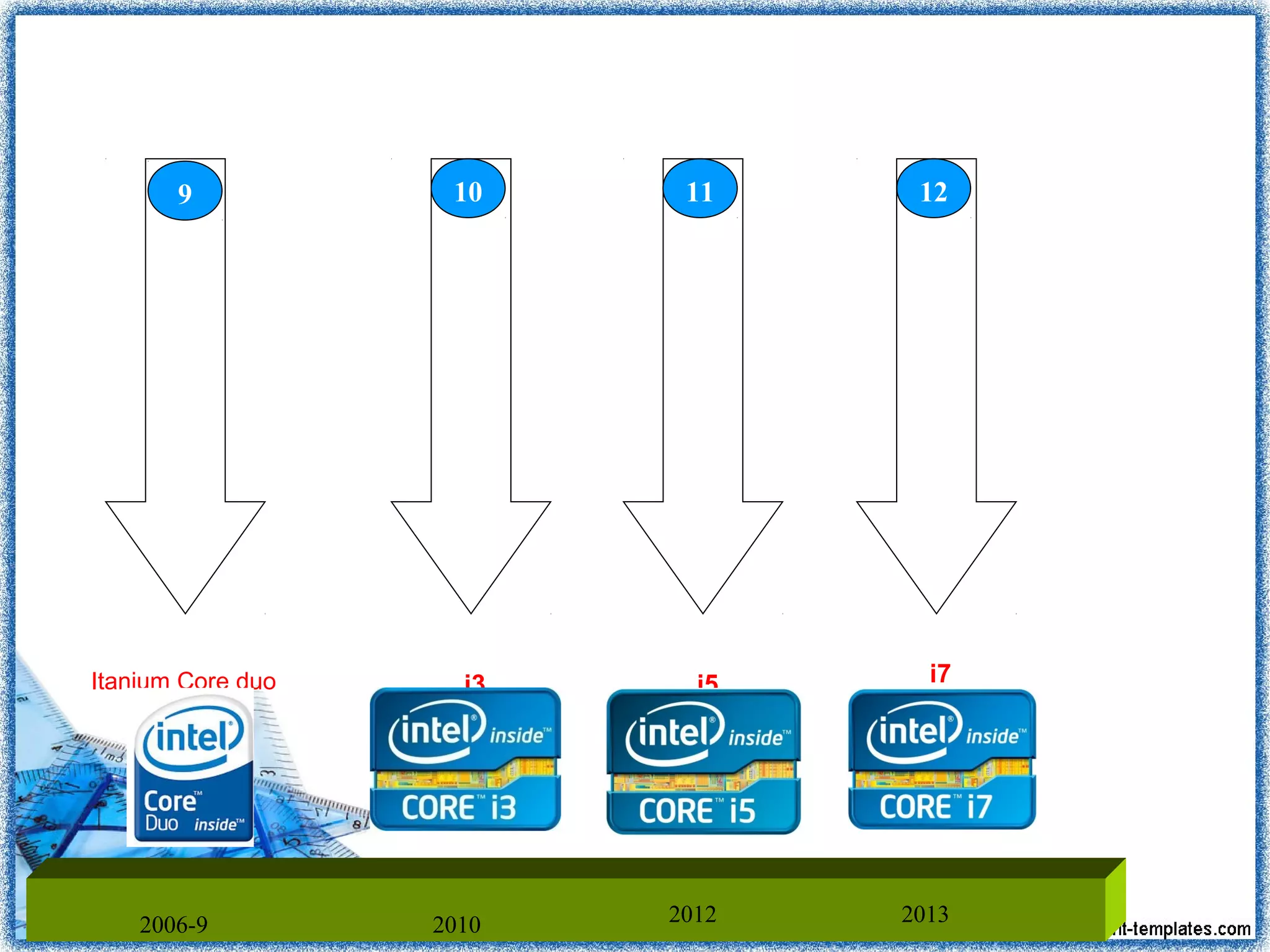

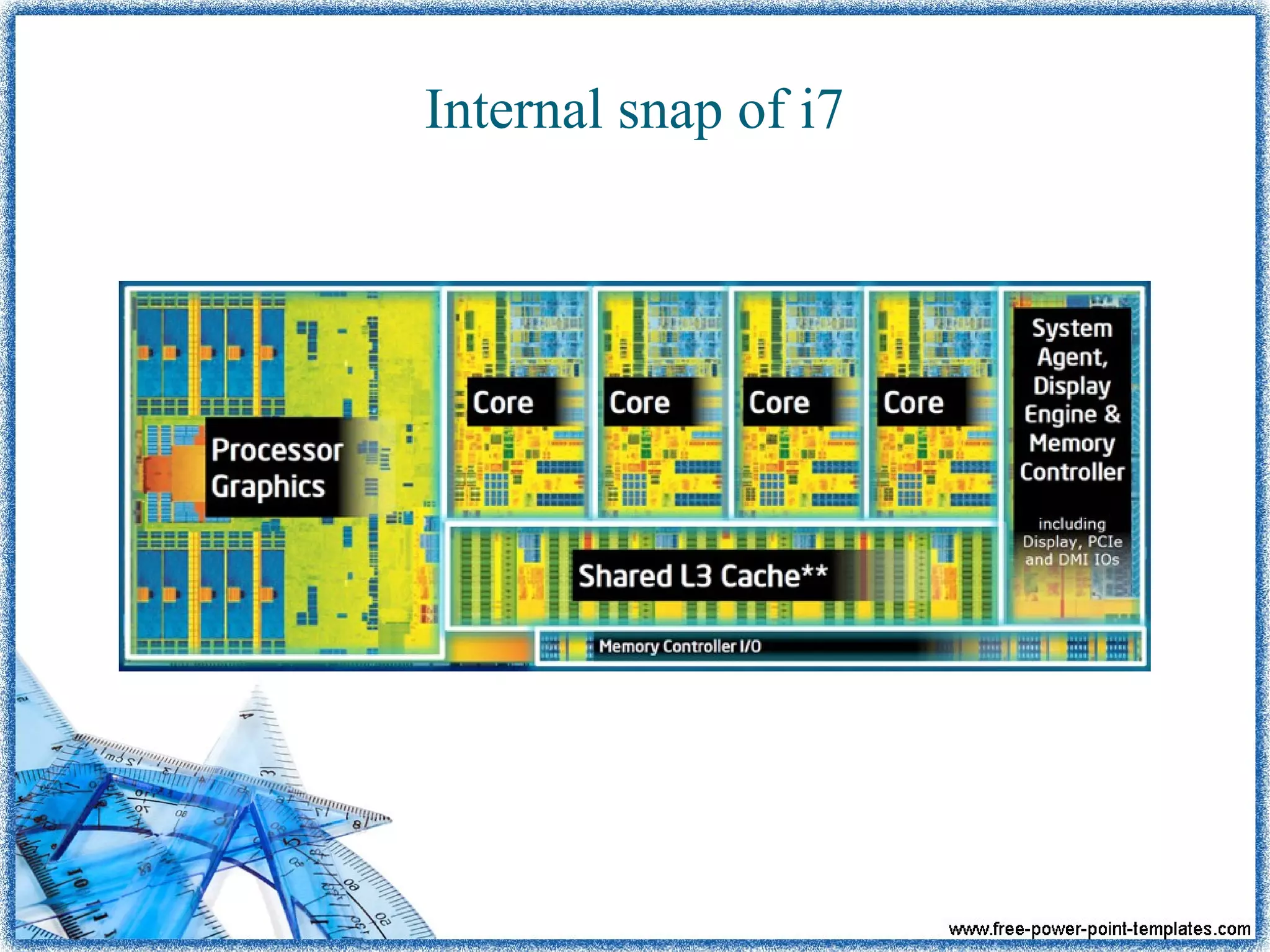

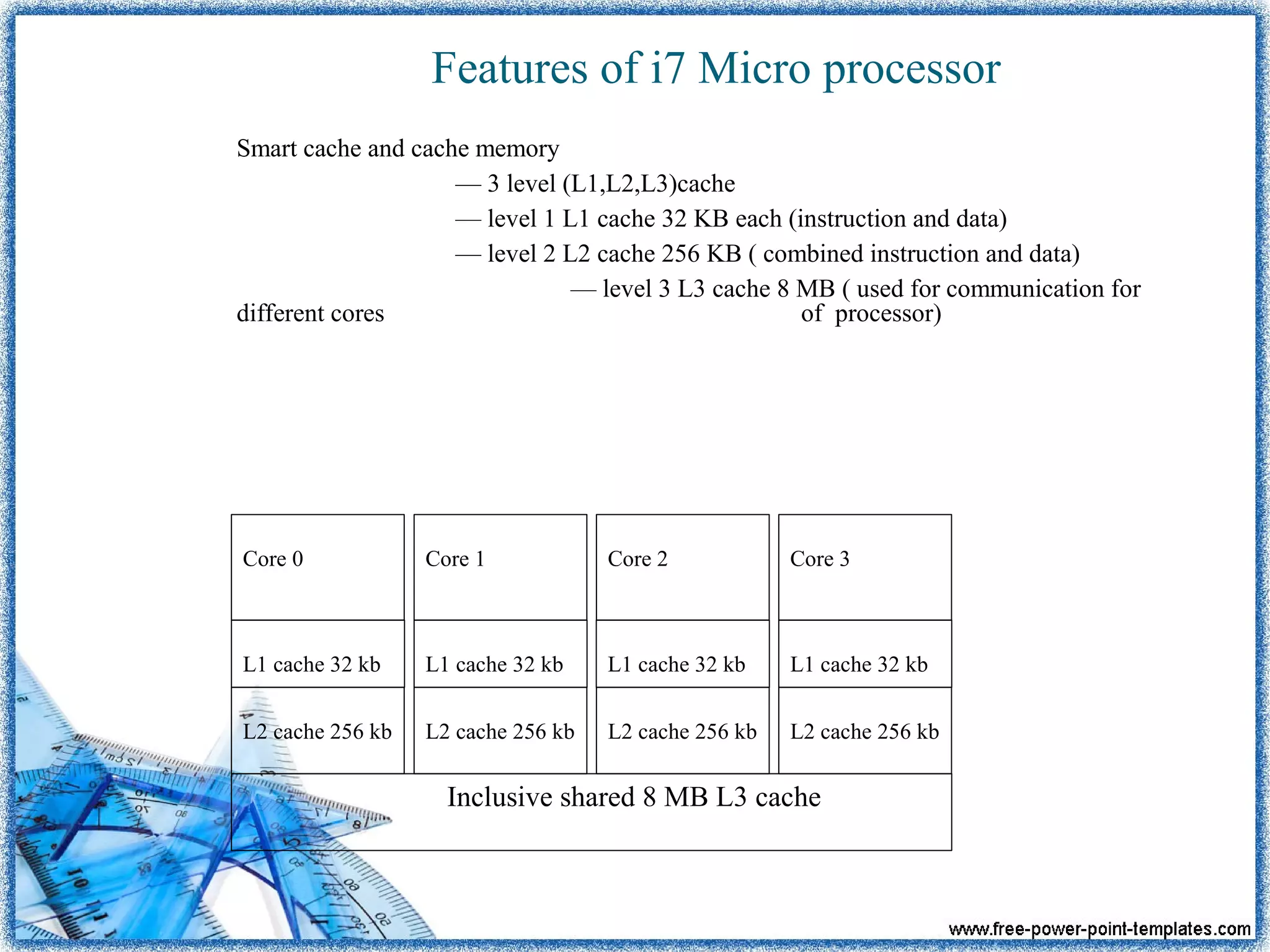

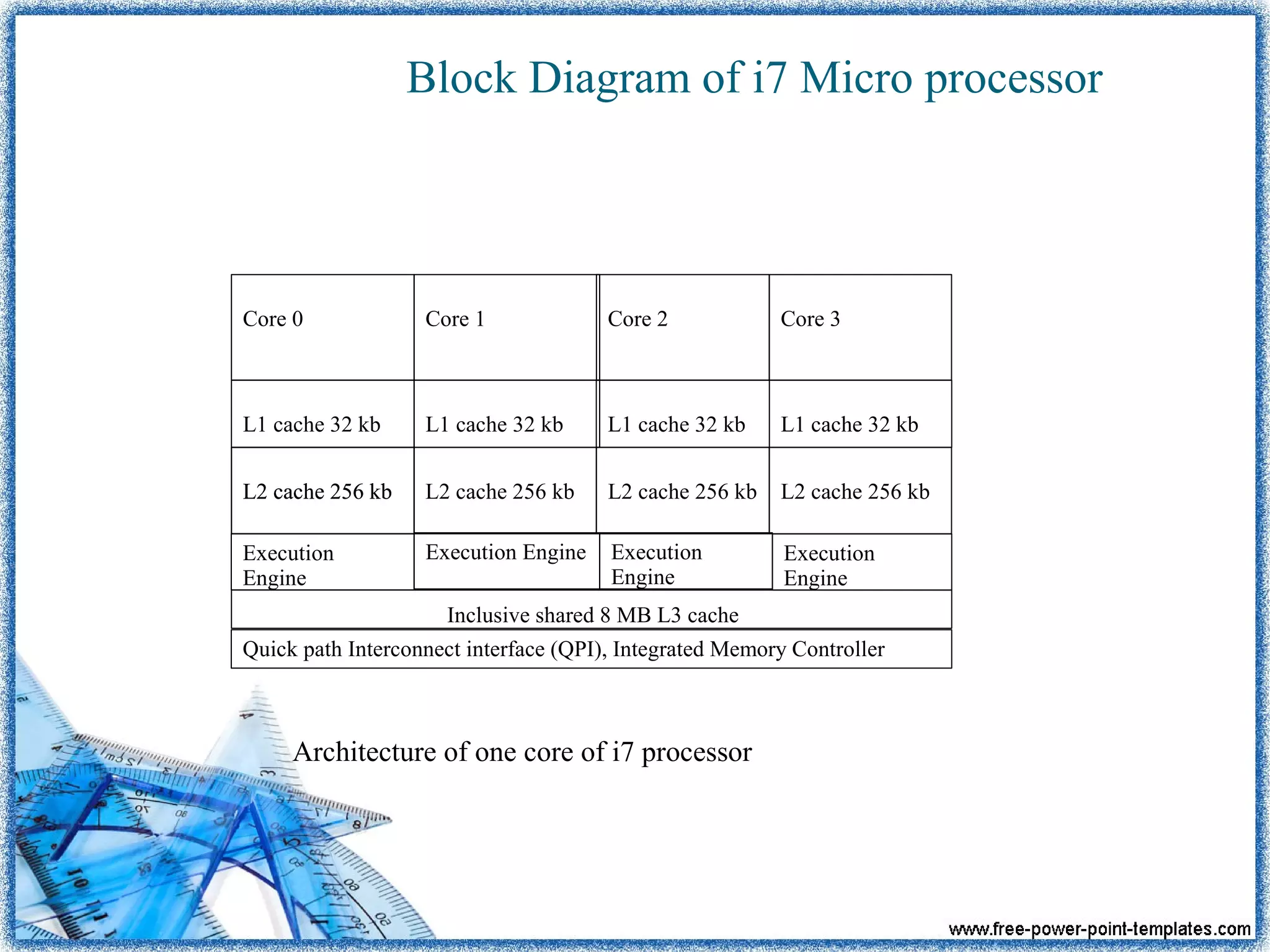

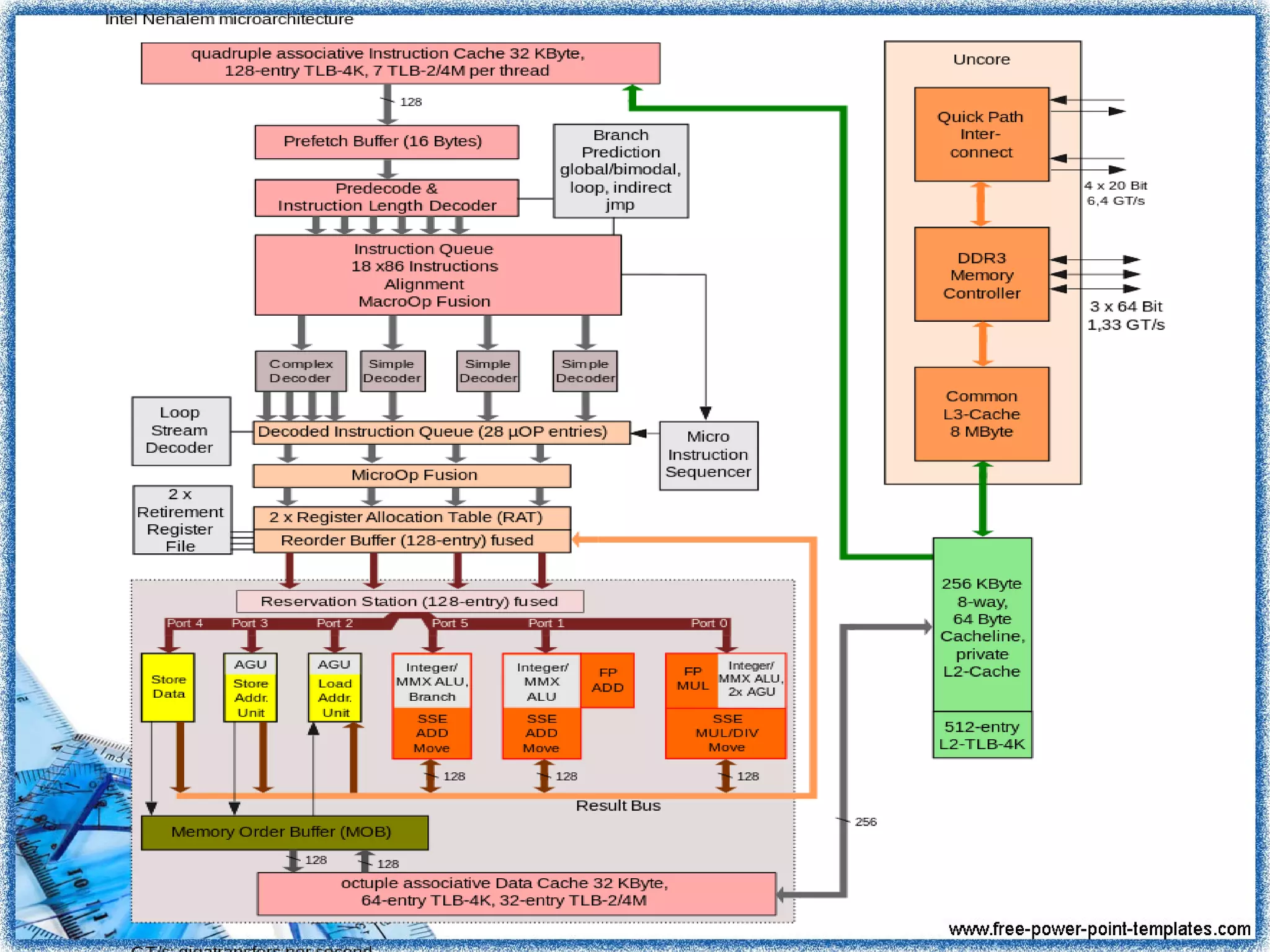

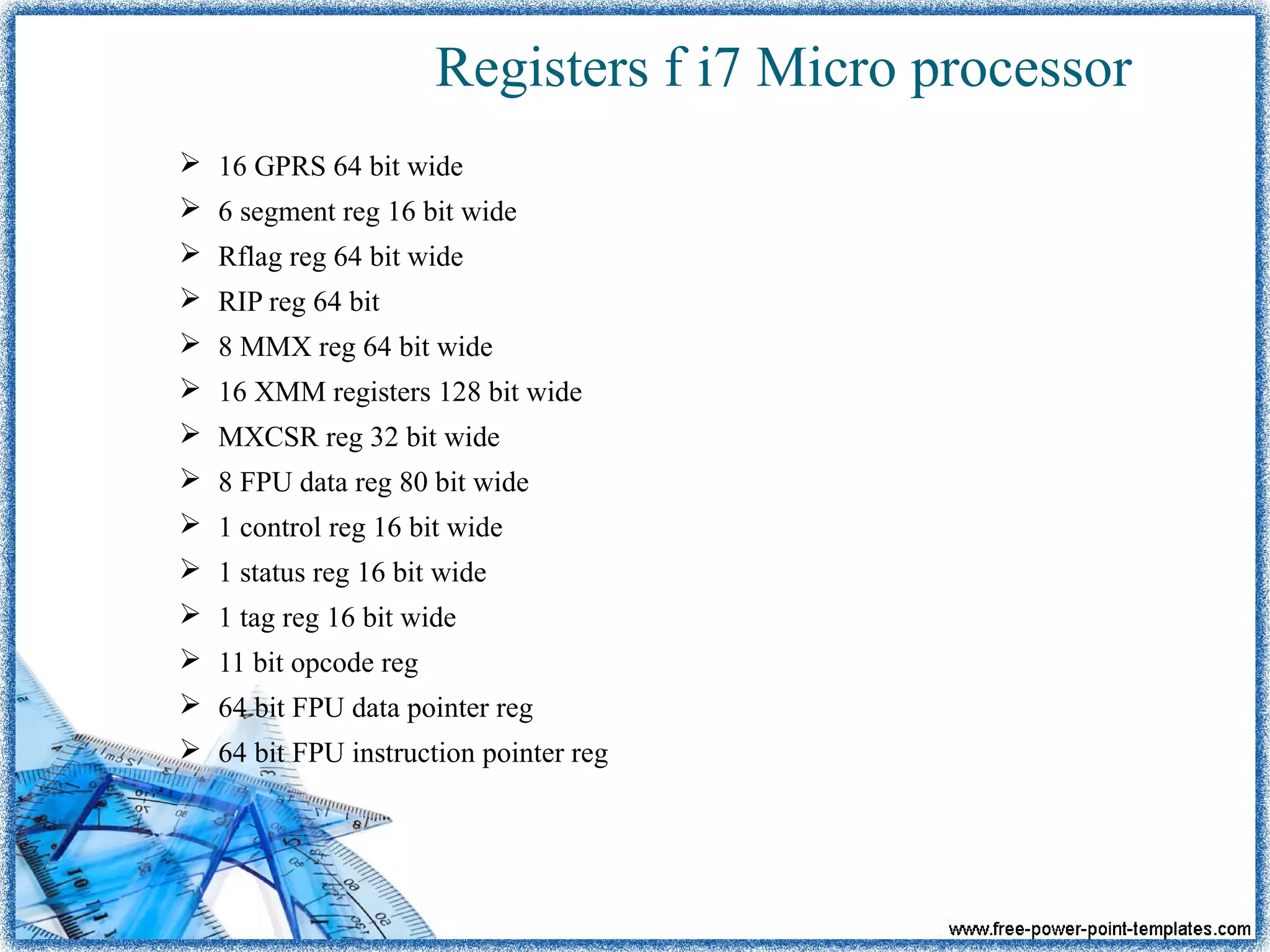

This document provides an overview of Intel processor history and details about the Intel i7 microprocessor. It outlines the evolution of Intel processors from 1978 to 2013, including models like the 8086, 80386, Pentium, and Core i series. The document then describes key features of the Intel i7 including its quad-core design, support for multiple threads, integrated memory controller, cache structure, and technologies like hyper-threading, turbo boost, and virtualization support. Diagrams of the i7 architecture and its registers are also included.