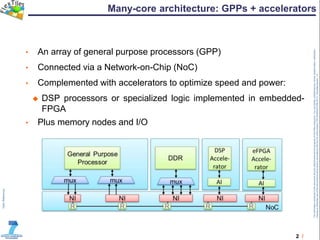

The document presents an overview of the Flextiles FP7 project, focusing on a low-power DSP accelerator integrated into a heterogeneous many-core architecture developed by CSEM. It describes CSEM's research programs, the architecture of the DSP accelerator, and the ultra-low power processors in the Icyflex family, emphasizing their applications and features. Additionally, it highlights the project's collaboration and objectives within the European Commission's funding framework.

![11 /

TheinformationcontainedinthisdocumentandanyattachmentsarethepropertyofFlexTilesconsortium.Youareherebynotifiedthatanyreview,dissemination,distribution,

copyingorotherwiseuseofthisdocumentmustbedoneinaccordancewiththeCAoftheproject(TRT/DJ/624412785.2011).Templateversion1.0

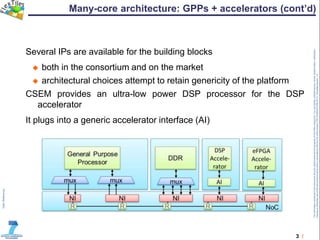

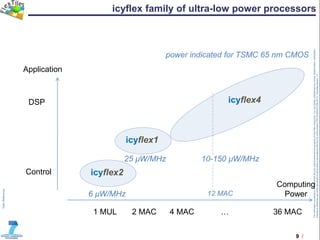

icyflex2 vs icyflex4

Feature icyflex2 icyflex4 VPS=2

Optimized for Control DSP

P, X, Y memory buses,

ISA, HW loops,

saturation, …

Instruction word [bits] 32 (1 or 2 sub) 64 (1, 2 or 3 sub)

Memory access [bits] 8, 16 or 32 2x (8, 16, 32, 64, 128)

Data processing [bits] 16 or 32, trunc 2x (16 or 32 or 64), full

Single Instr. Multiple Data (SIMD) No Yes, up to 8 MAC

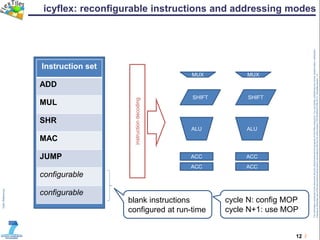

Instruction set is reconfigurable

on the fly

No Yes

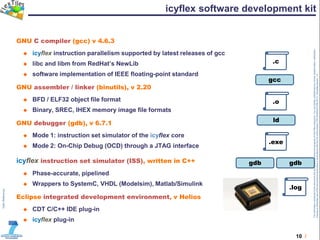

Software Development Kit (SDK) GNU-based tool suite (gcc, gdb) + cycle-

accurate instruction set simulator (ISS)

Hardware Devt Kit (HDK) FPGA-based, customizable

VPS = Vector Processing Slices in the Vector Processing Unit of the DSP](https://image.slidesharecdn.com/jr4bnv9ty2rn94zbxpg4-signature-28971b684801a615727cb292d36adf0c4f641a8d4e0e4974b03ea9e226d783cb-poli-140724063028-phpapp01/85/Conference-on-Adaptive-Hardware-and-Systems-AHS-14-The-DSP-for-FlexTiles-12-320.jpg)