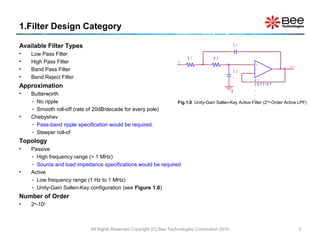

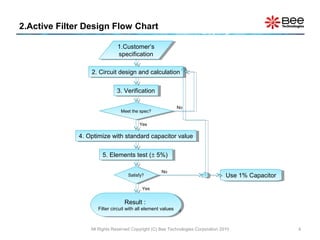

This document describes the design process for an active low pass filter. It includes:

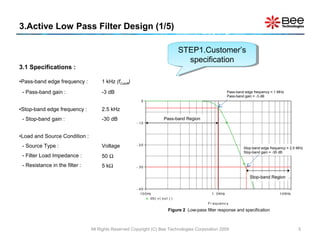

1) Specifying the filter requirements including passband, stopband frequencies and gains.

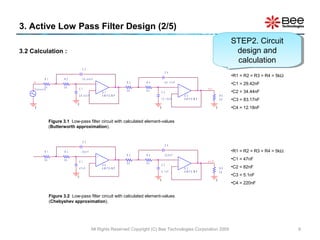

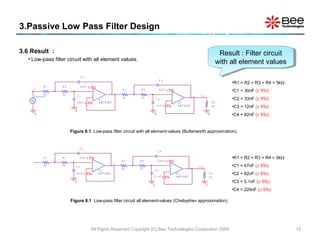

2) Calculating the element values using Butterworth and Chebyshev approximations.

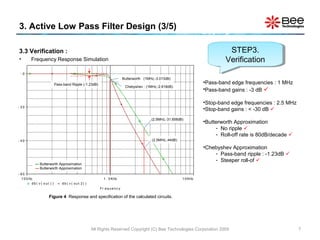

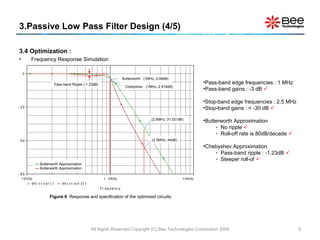

3) Verifying the frequency response meets specifications.

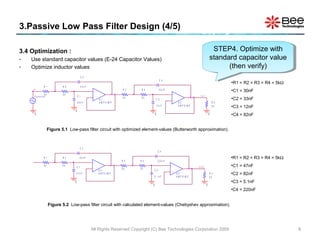

4) Optimizing values using standard capacitor sizes.

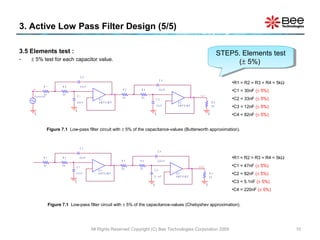

5) Testing elements with ±5% tolerance.

The result is the filter circuit with all calculated element values that meets the design specifications.