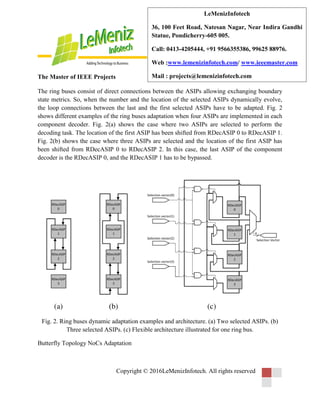

This document presents a design for a dynamically reconfigurable multiprocessor architecture for turbo decoding, aimed at improving flexibility and throughput for multistandard wireless communication. The proposed architecture enhances existing systems by offering fast reconfiguration while maintaining decoding performance, addressing issues in latency and scalability. It includes advanced features like a bus-based communication infrastructure and adaptable ring buses for efficient configuration management.