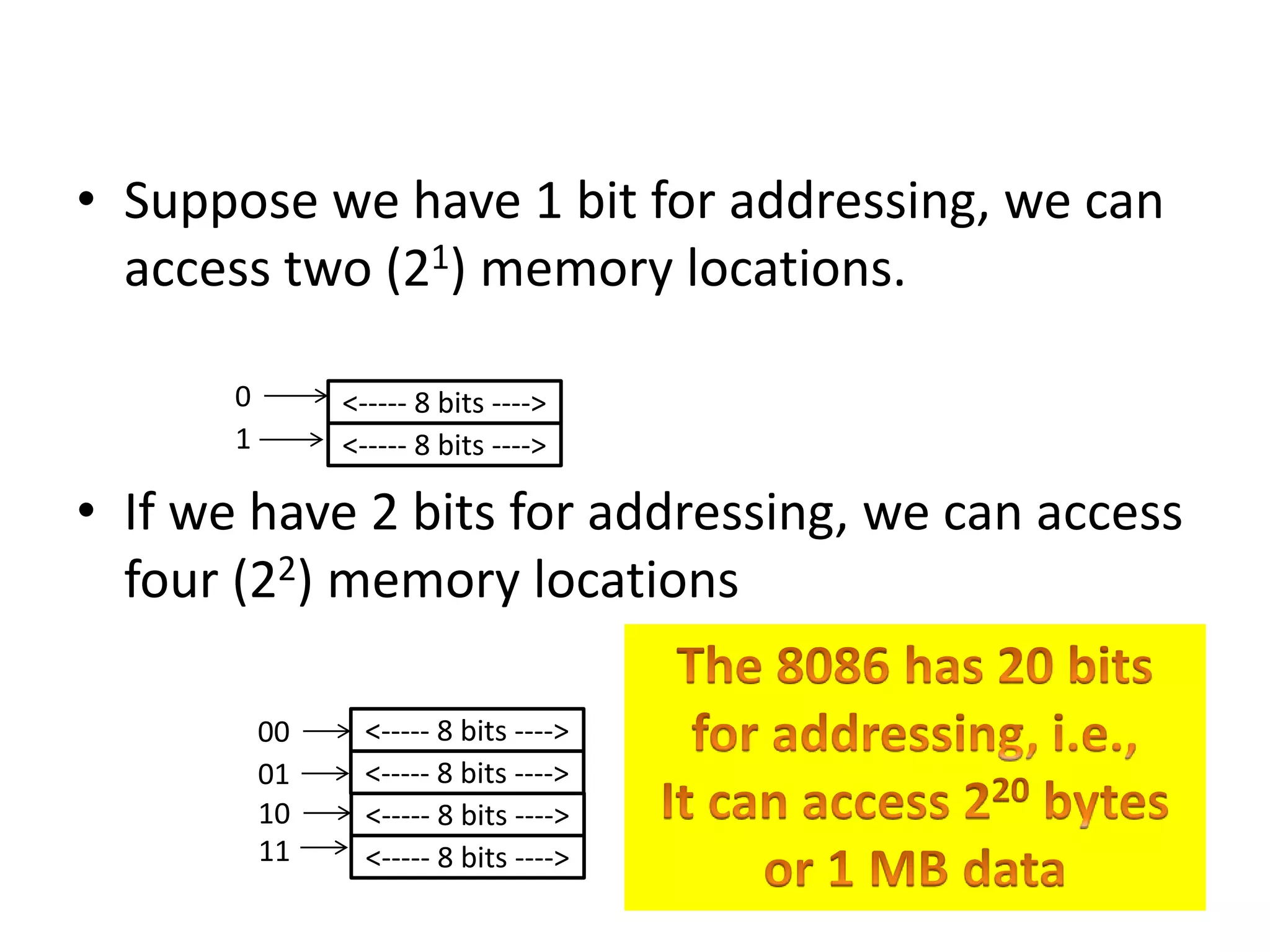

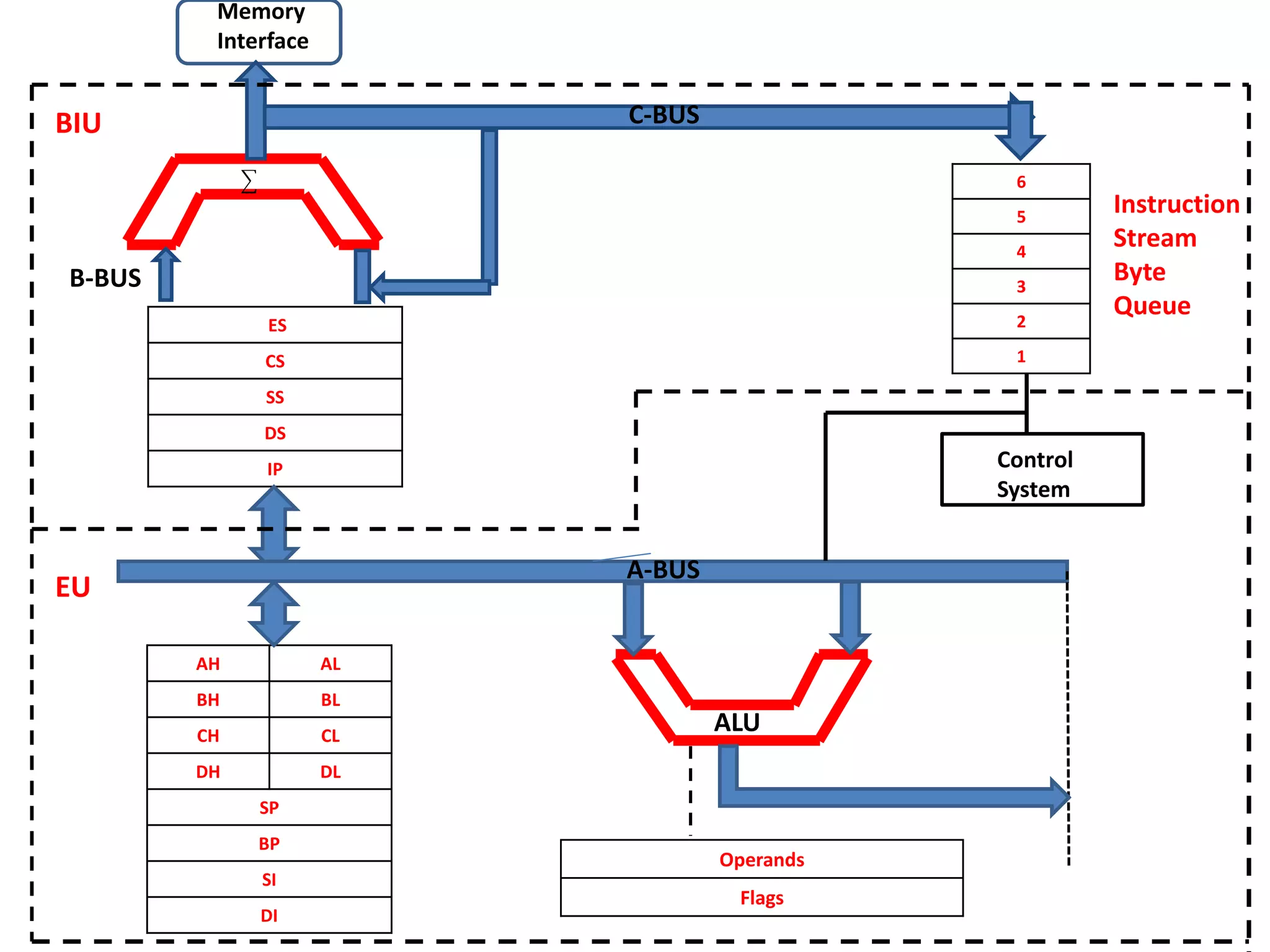

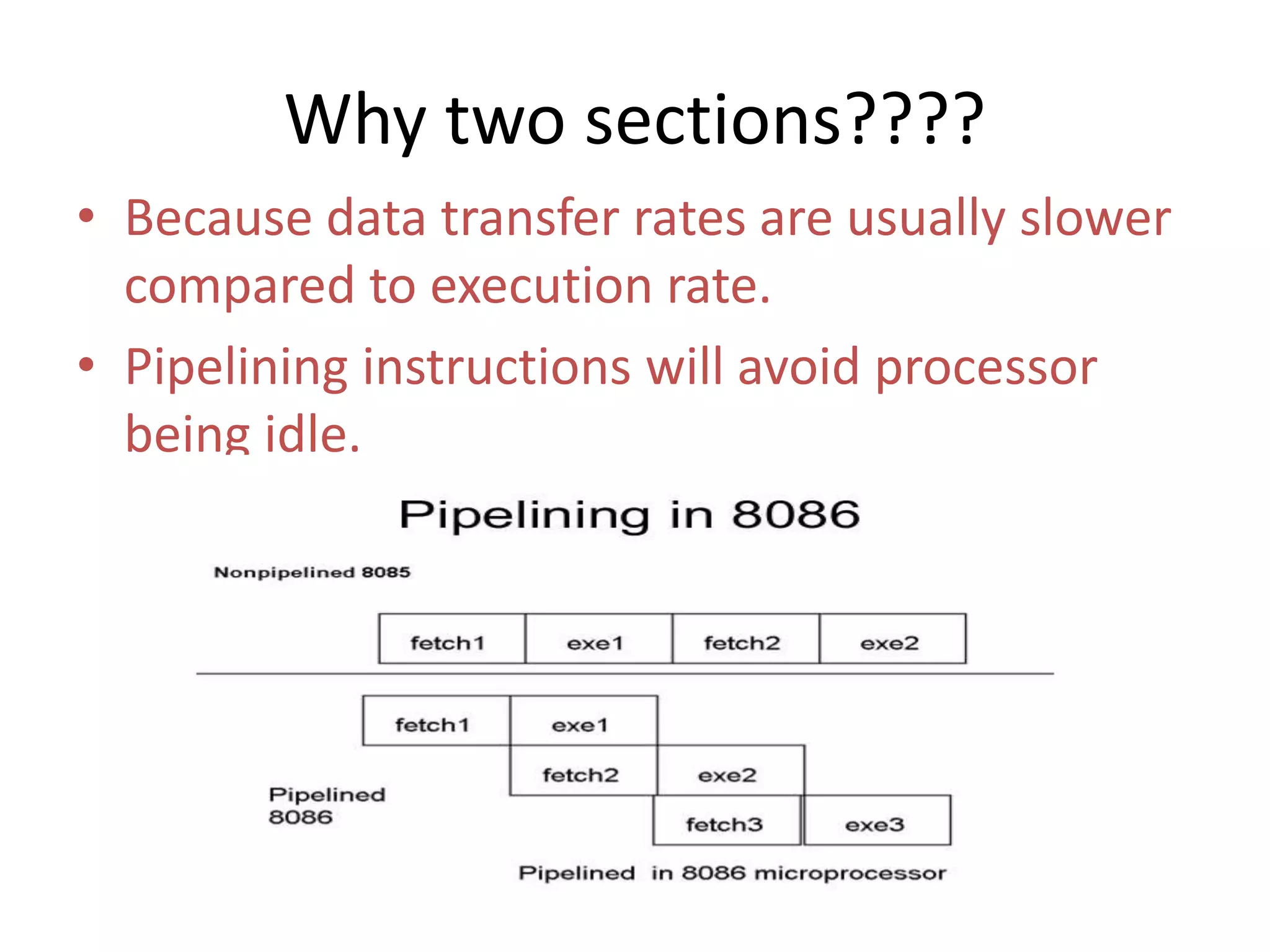

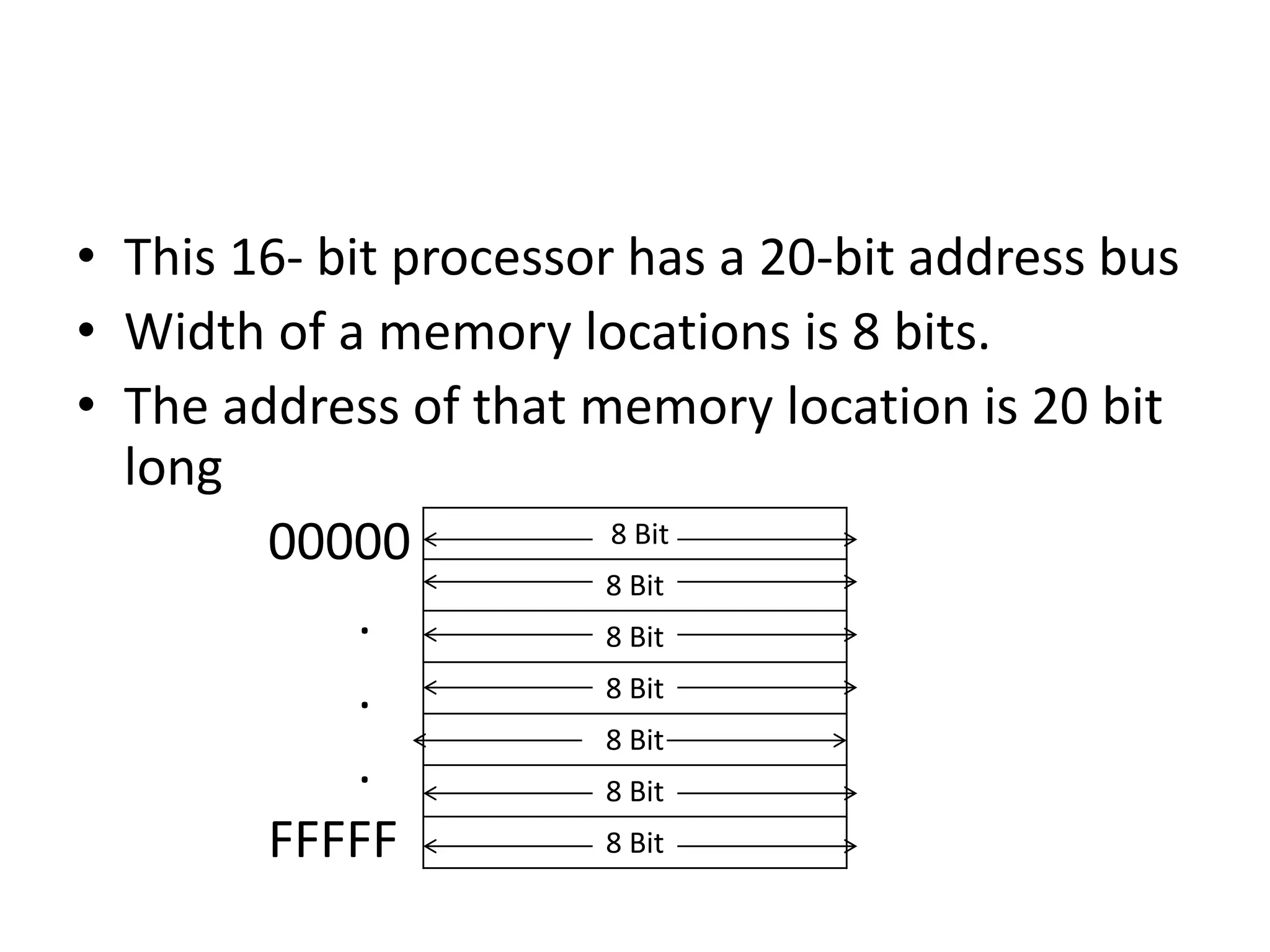

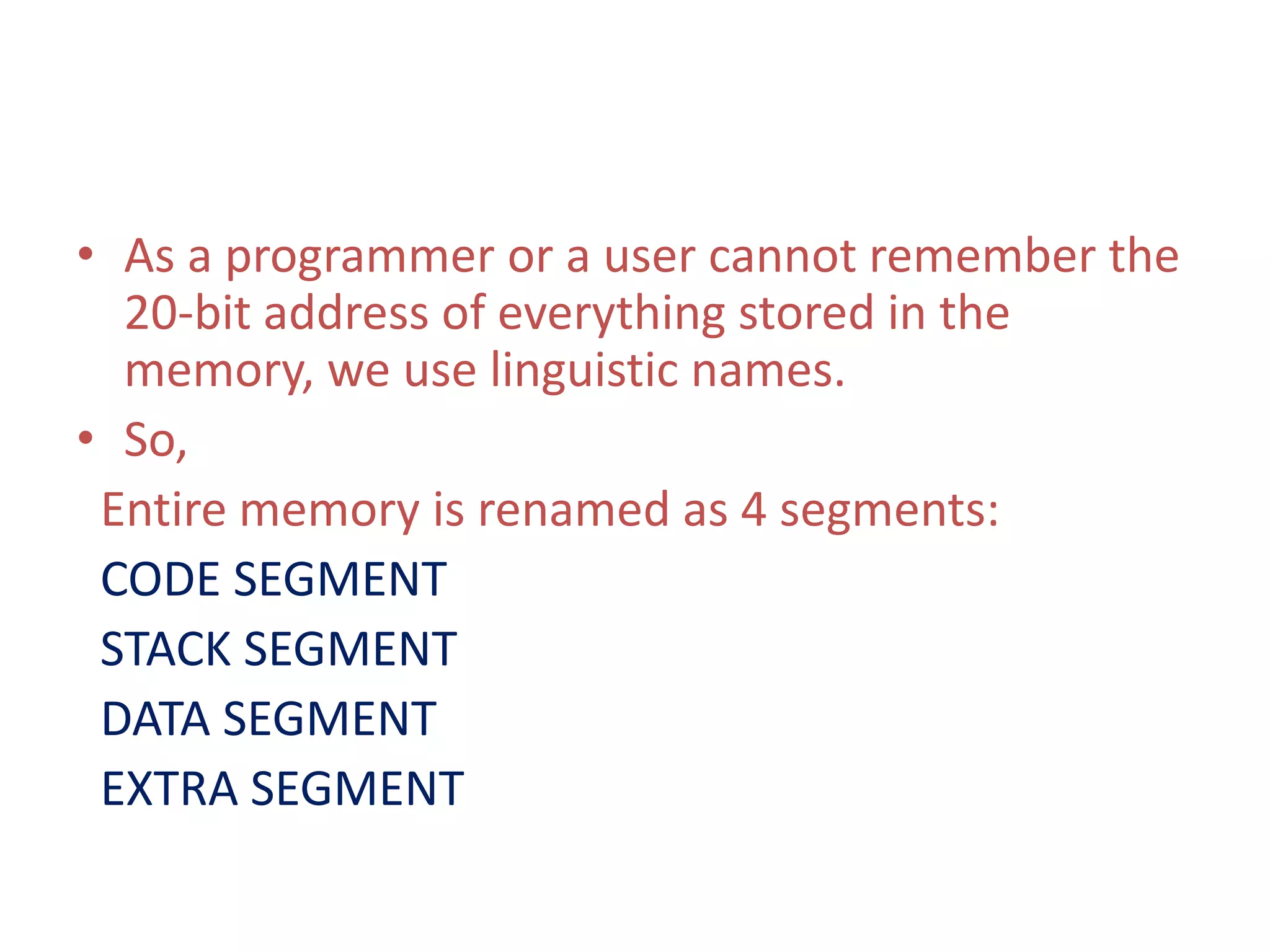

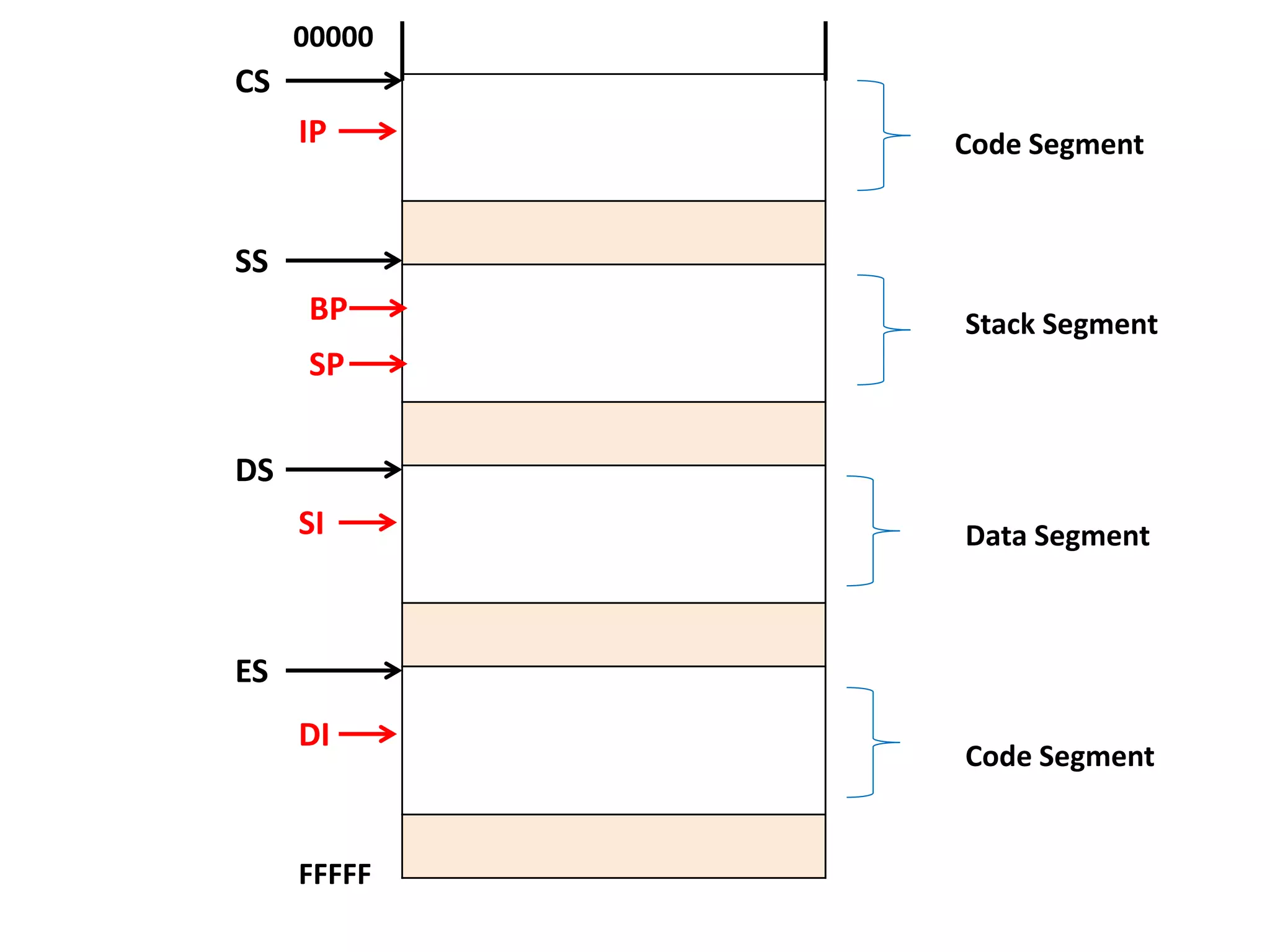

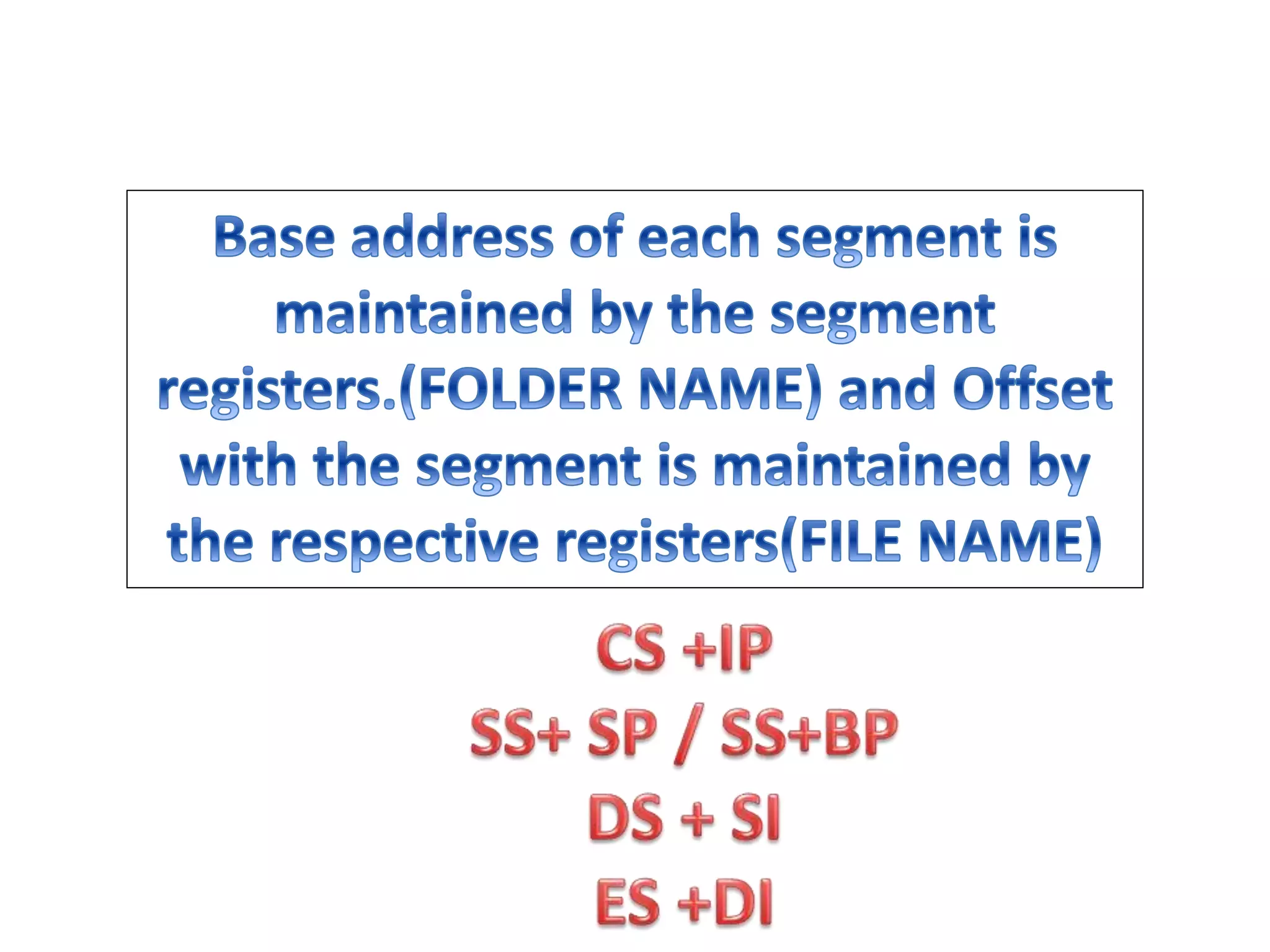

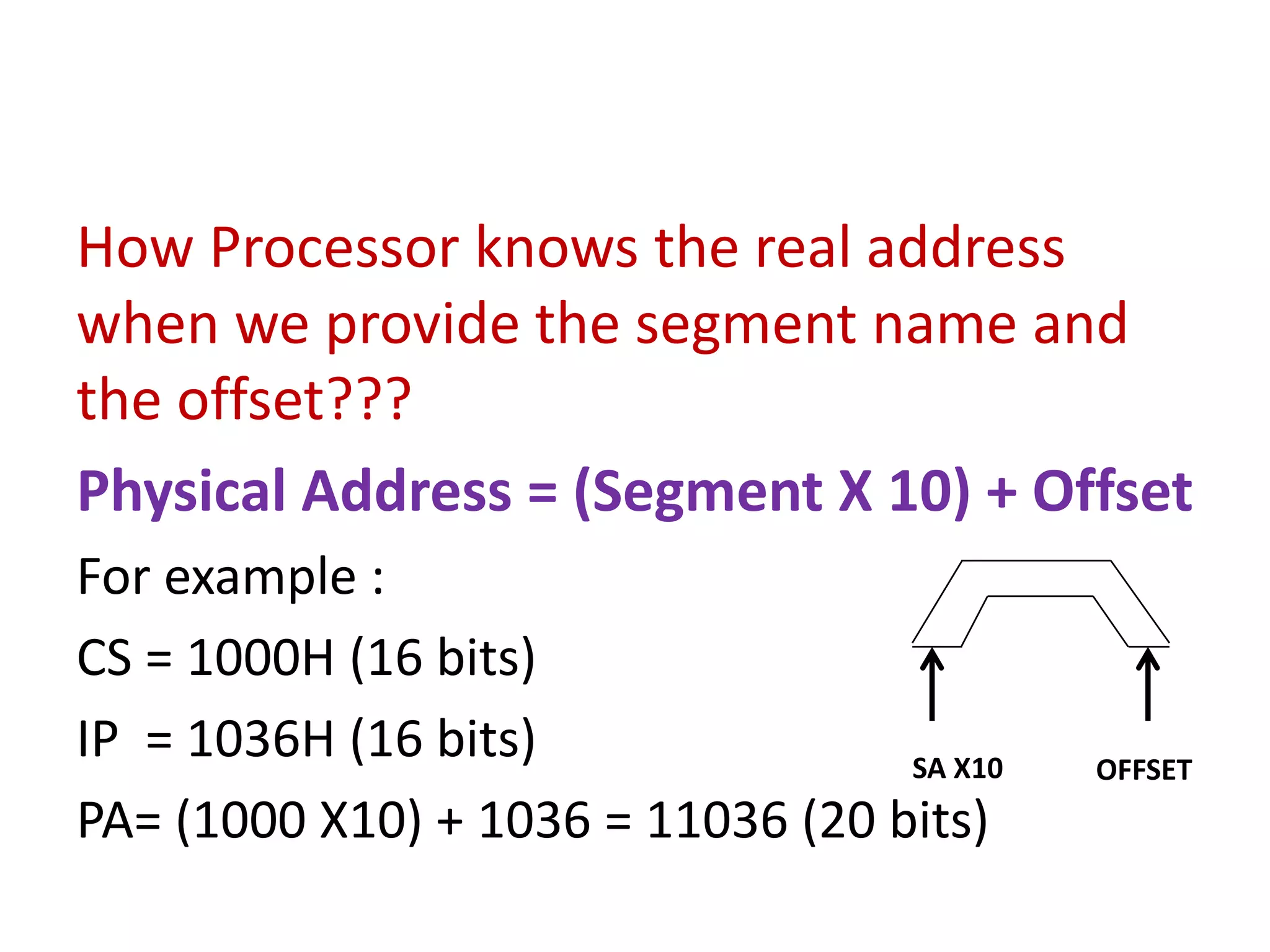

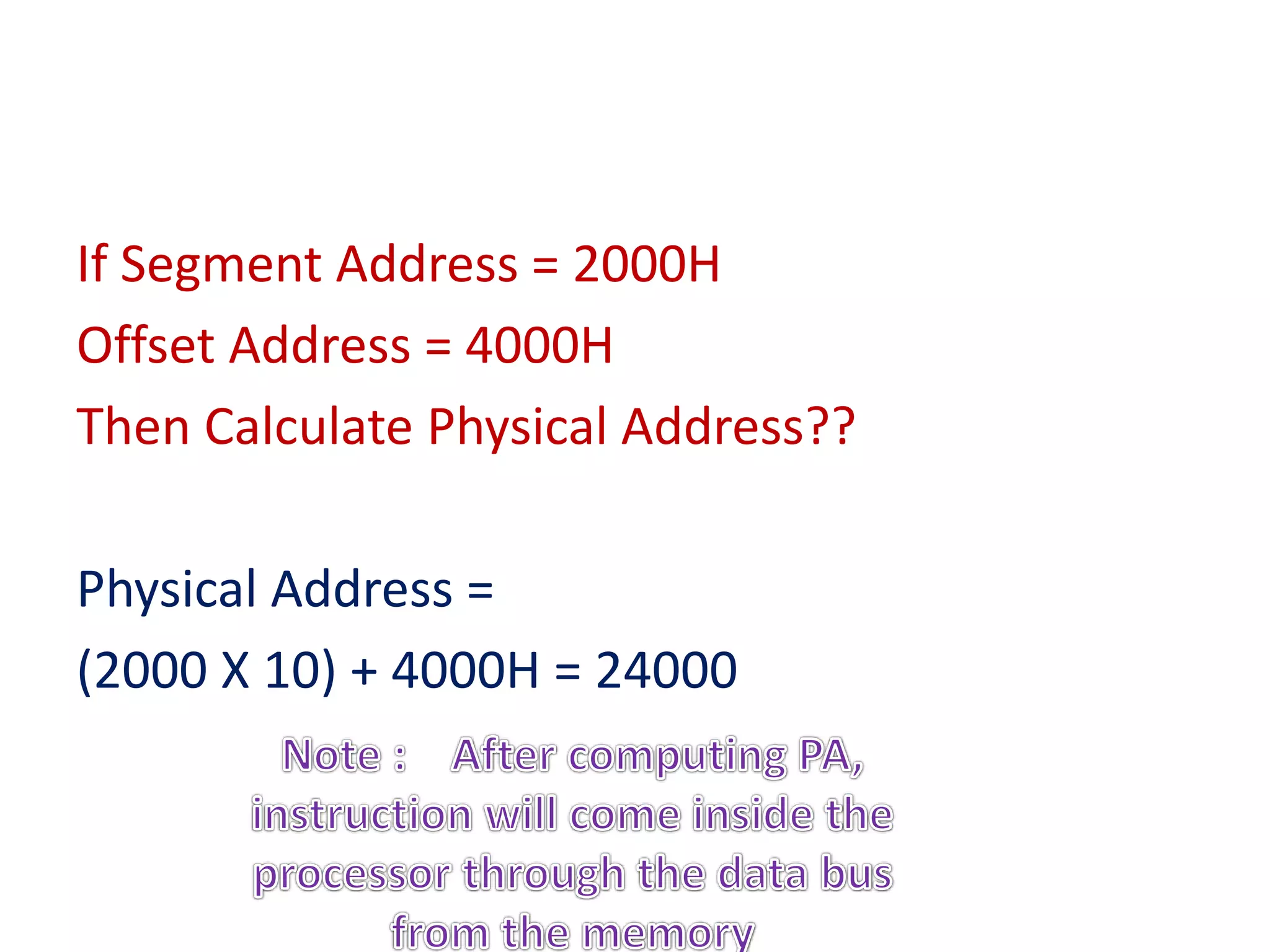

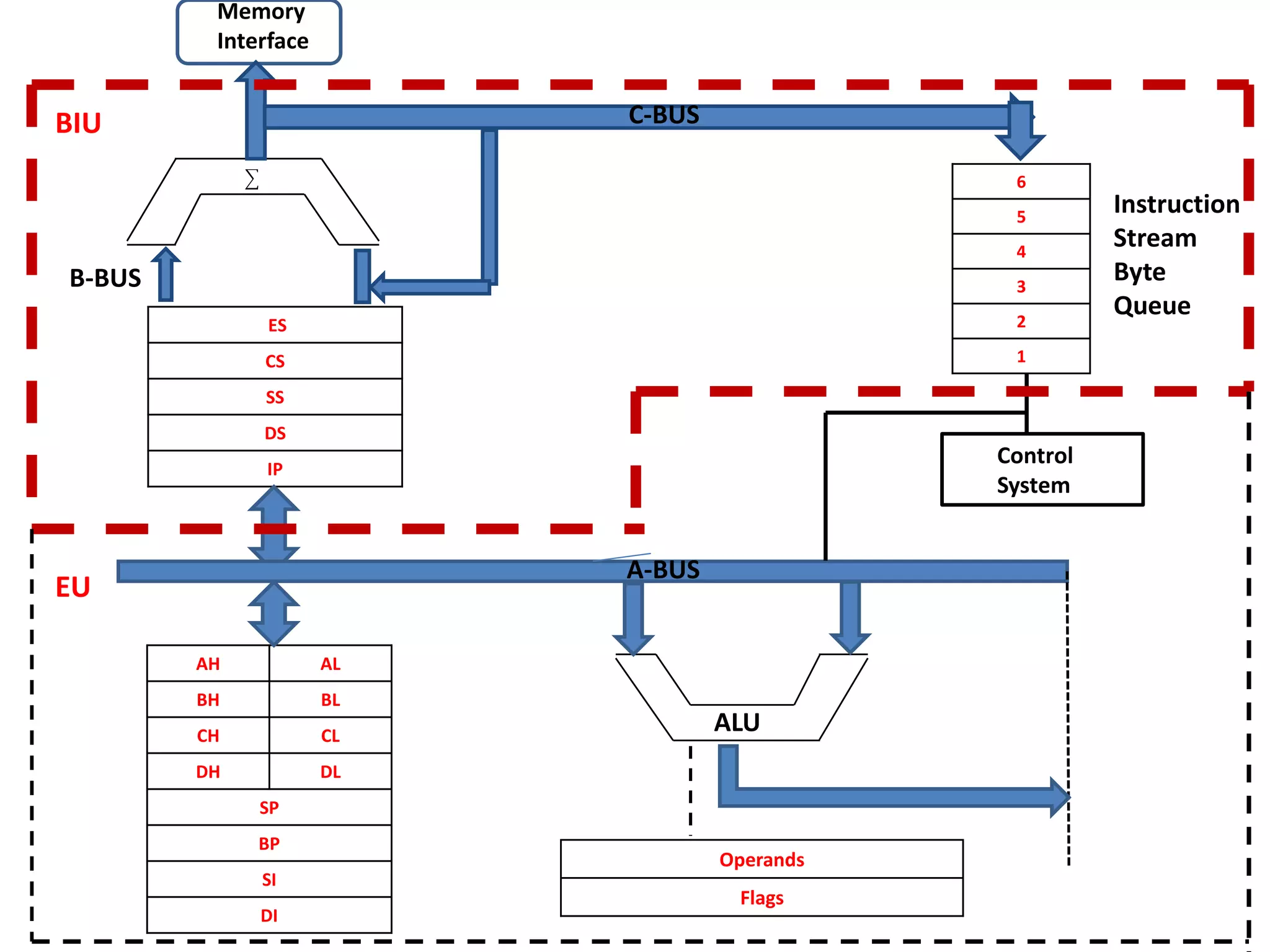

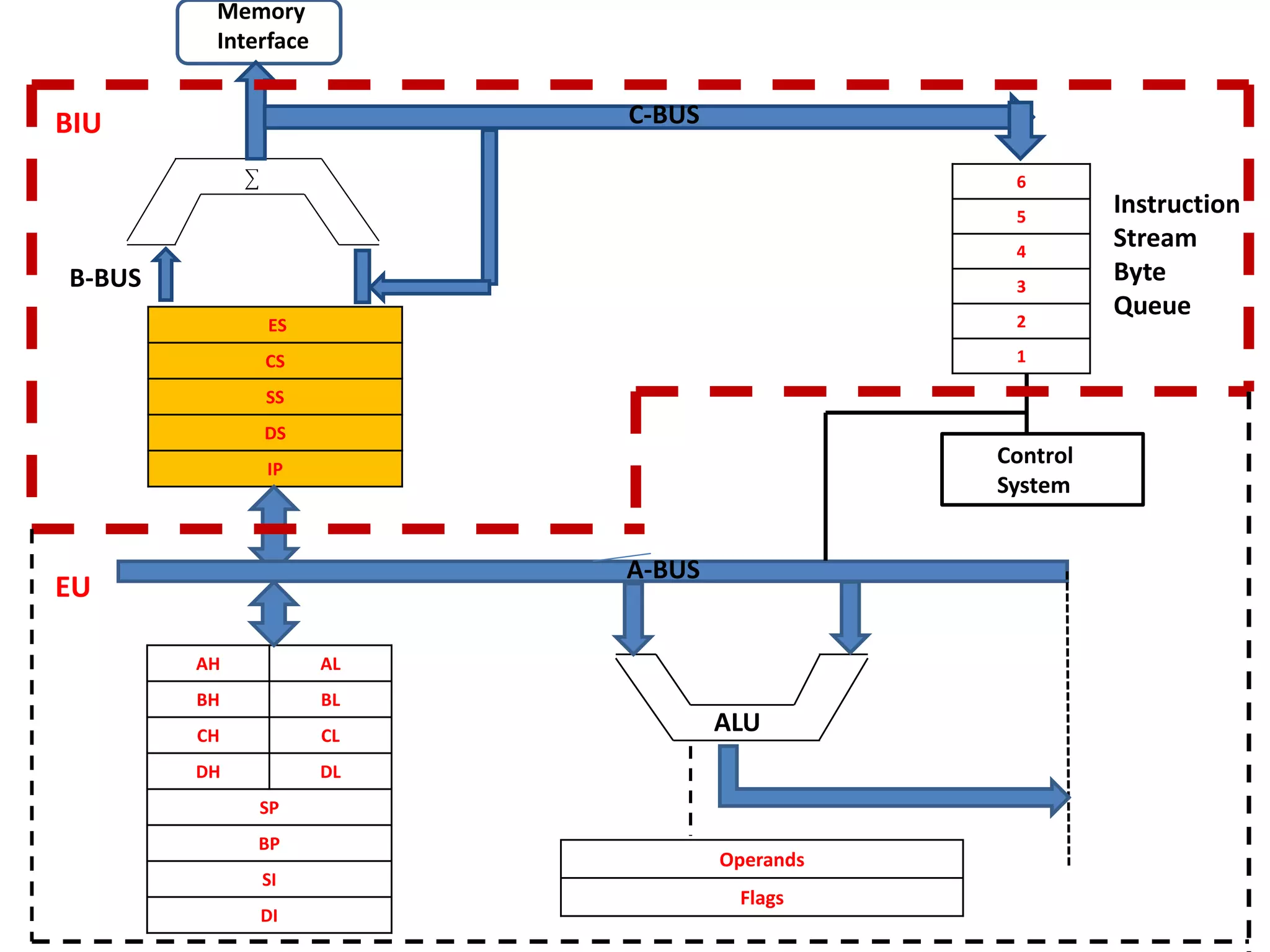

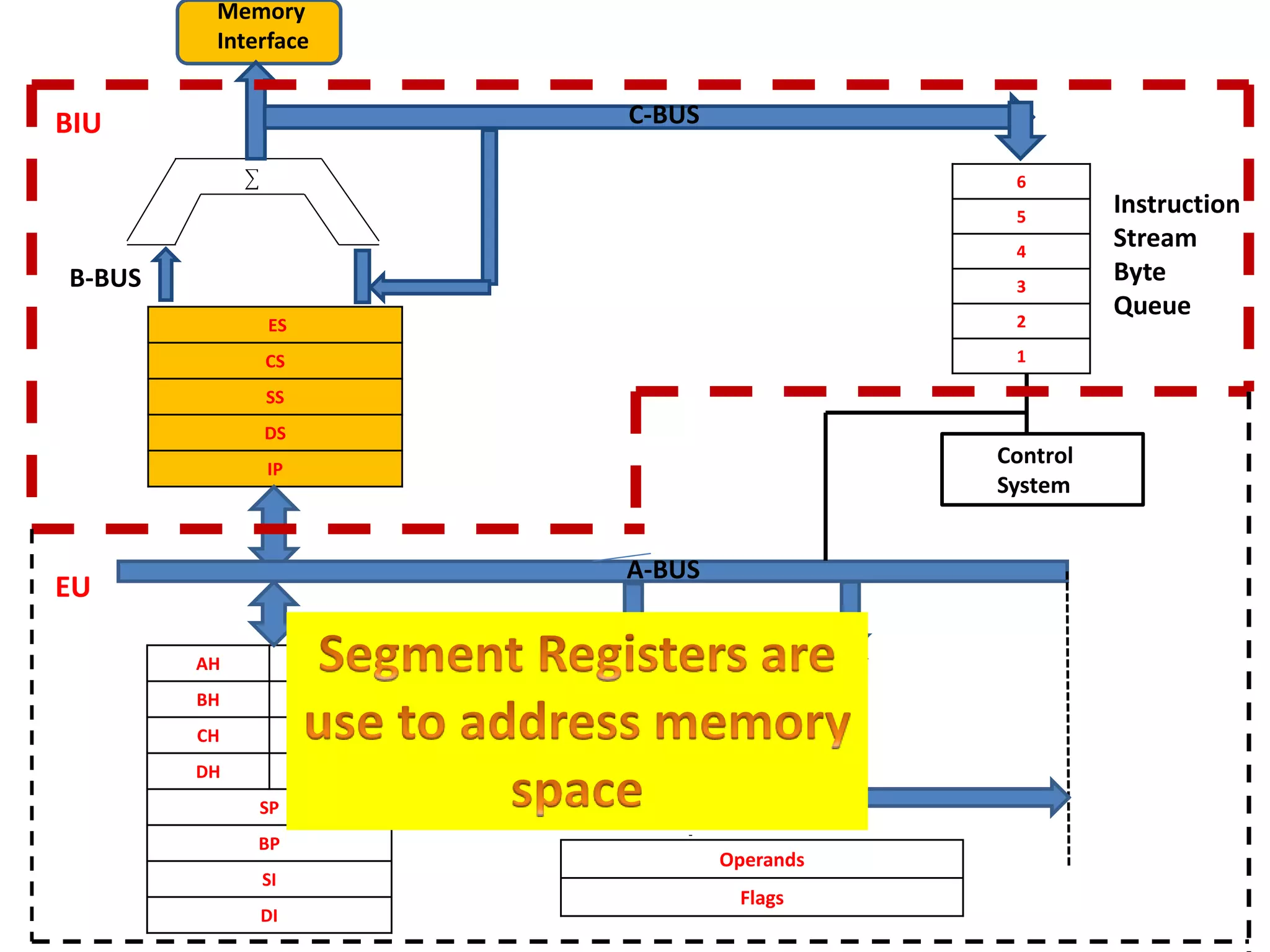

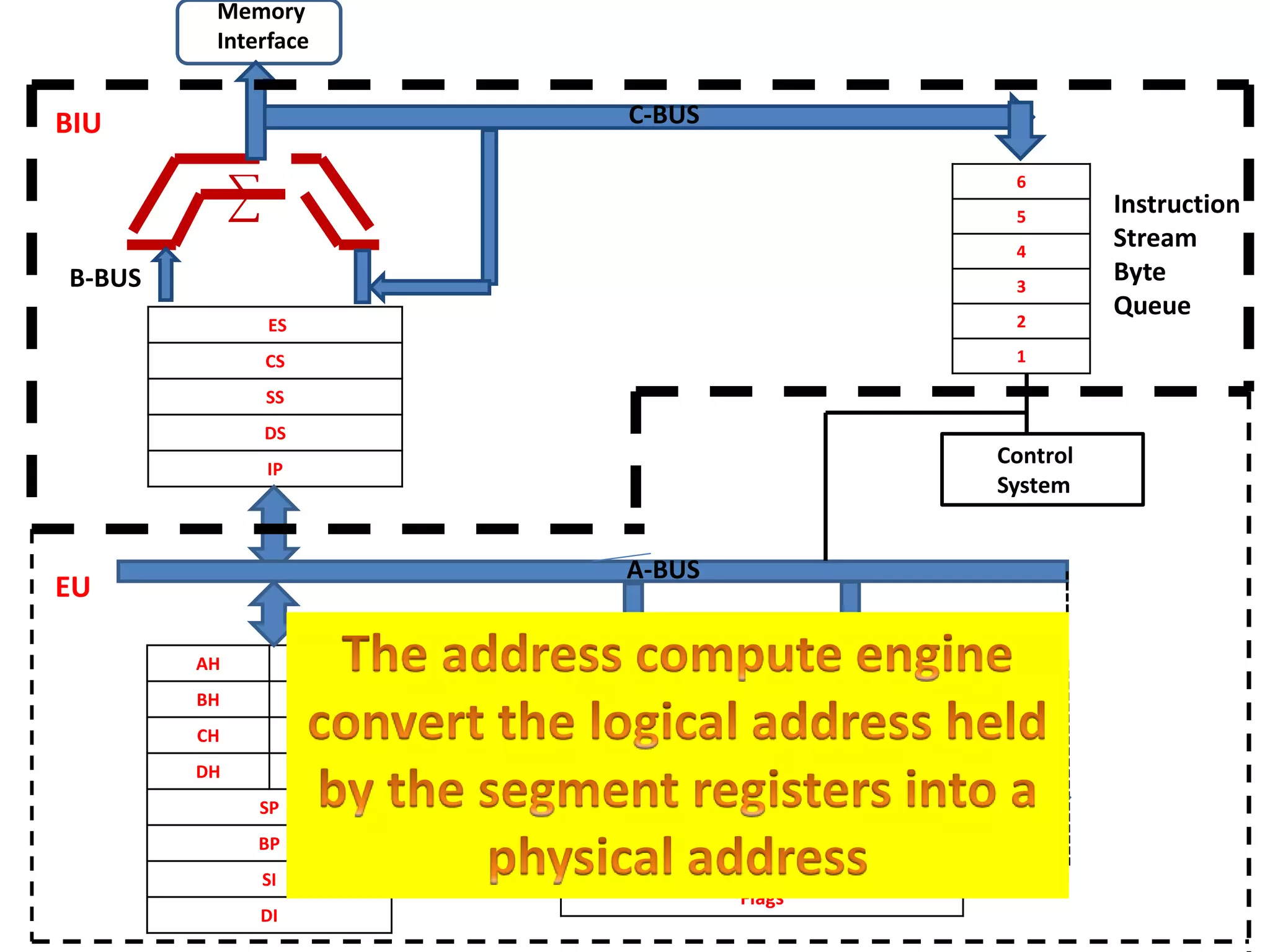

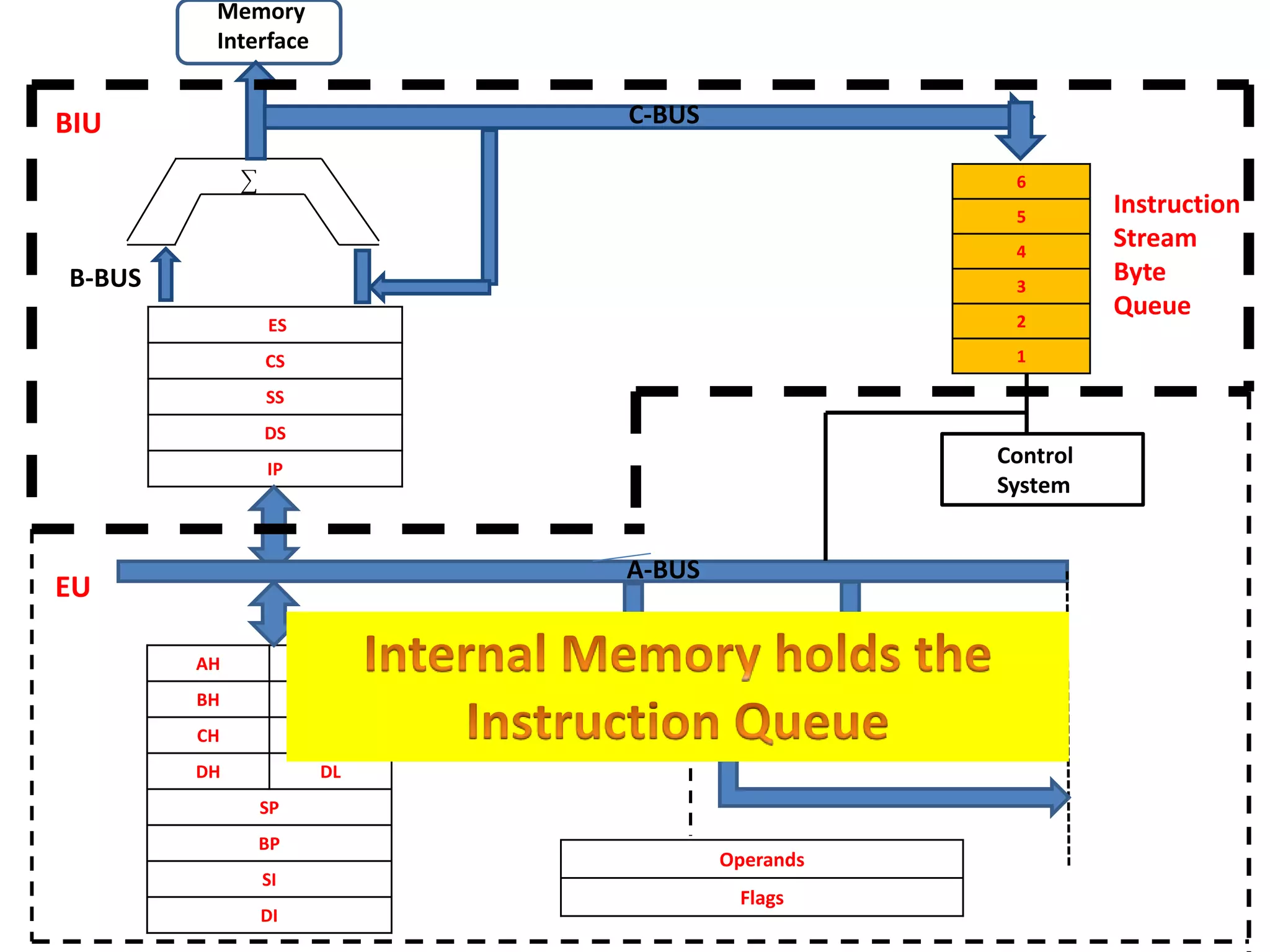

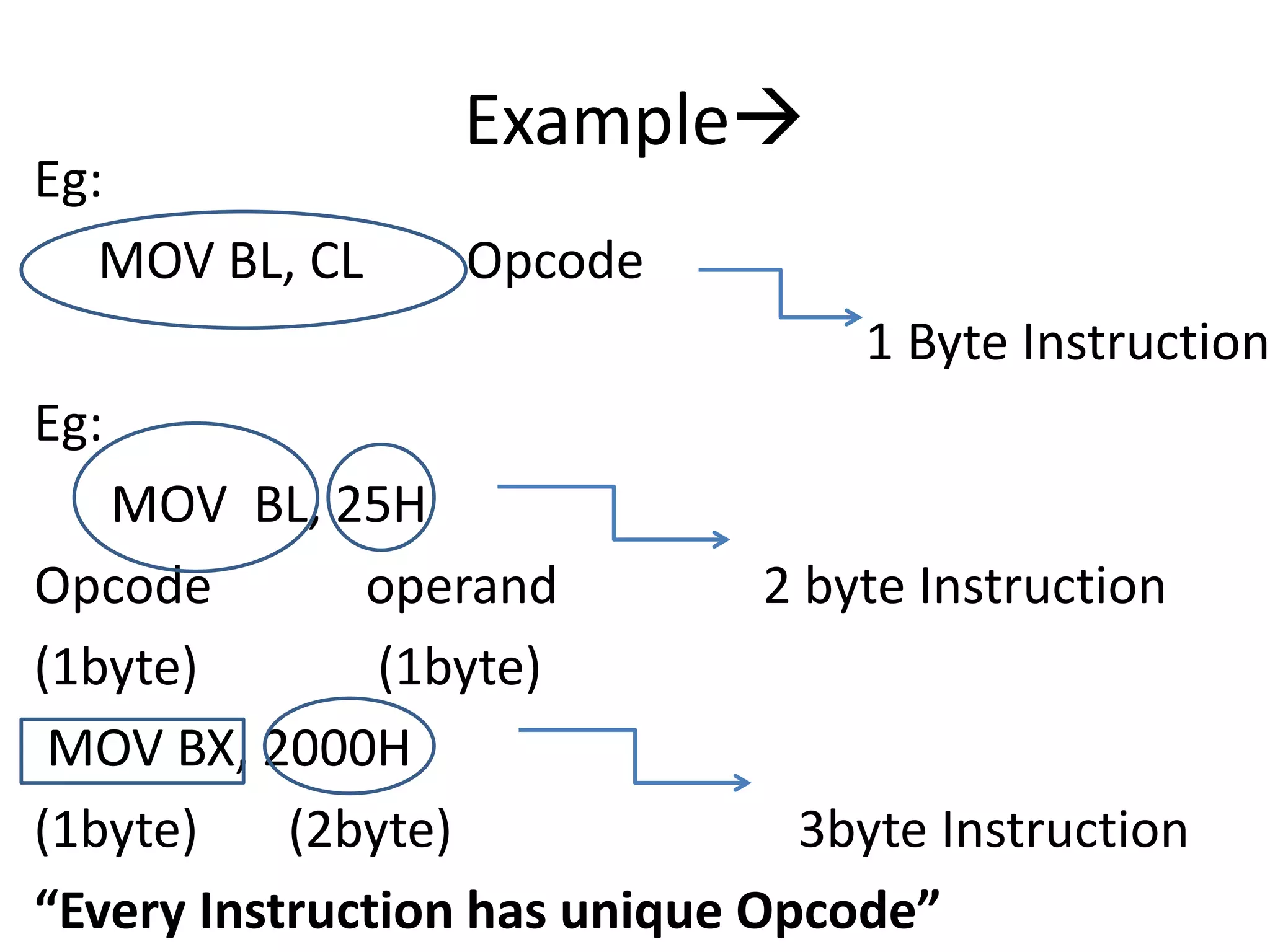

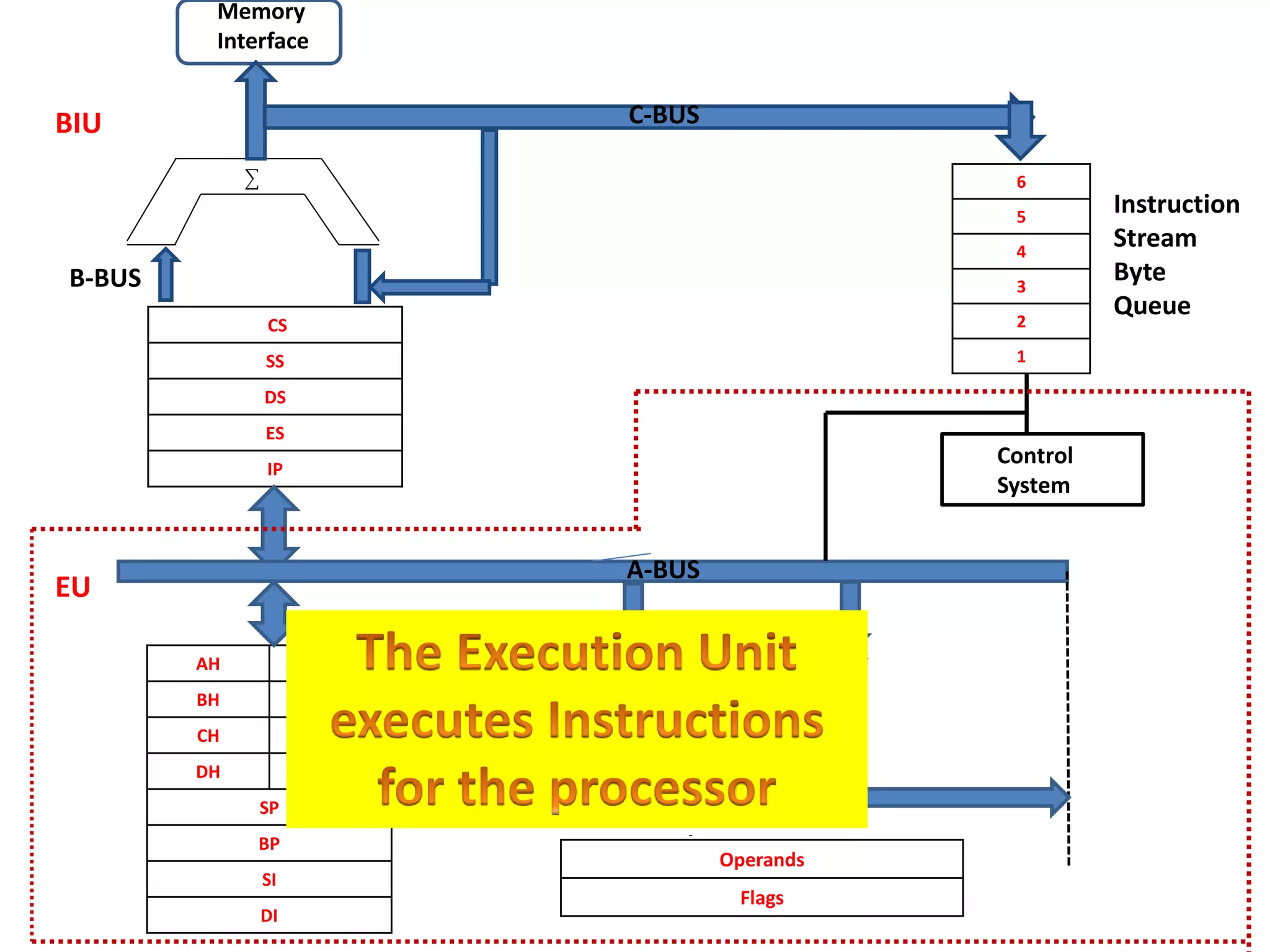

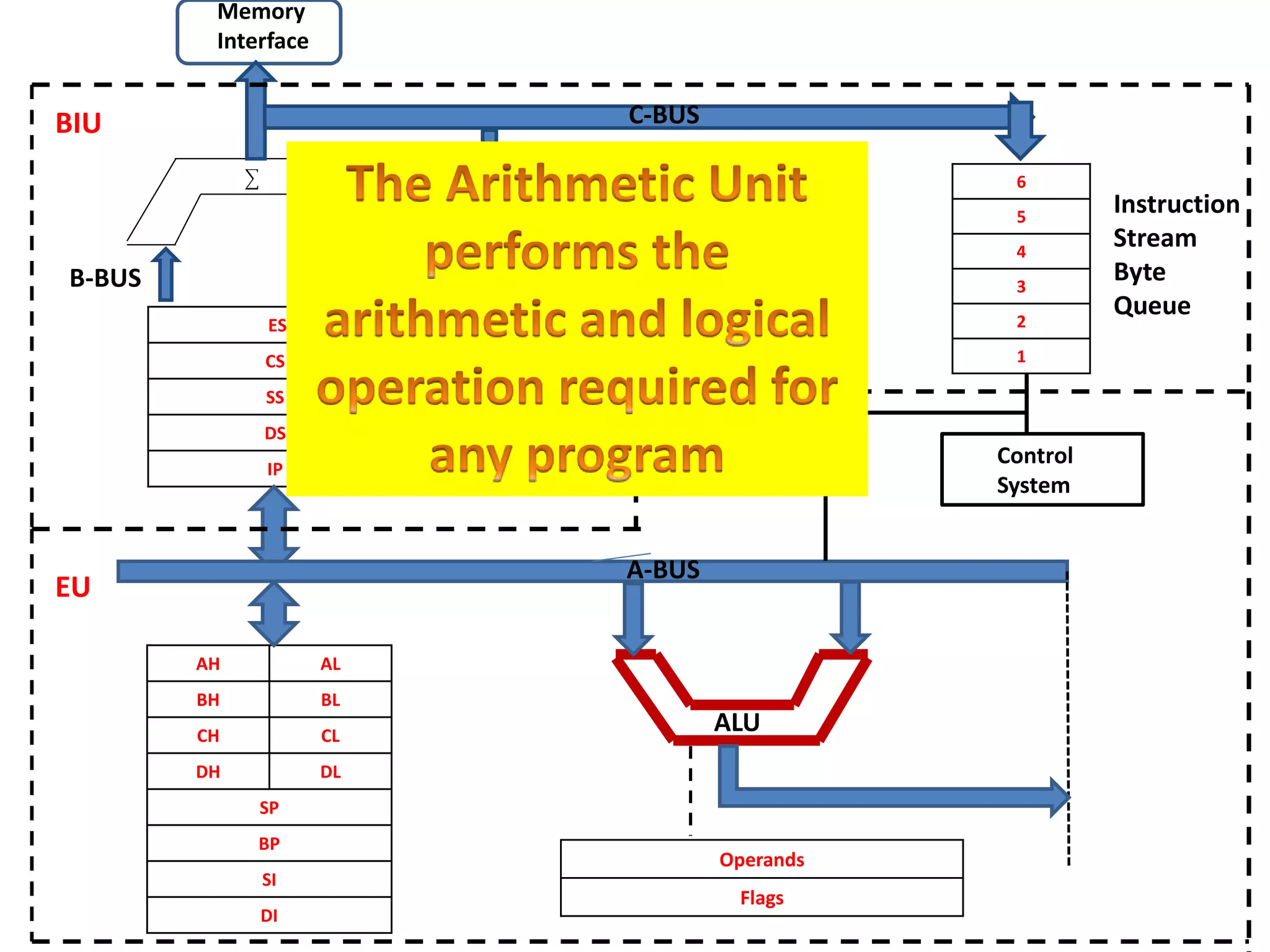

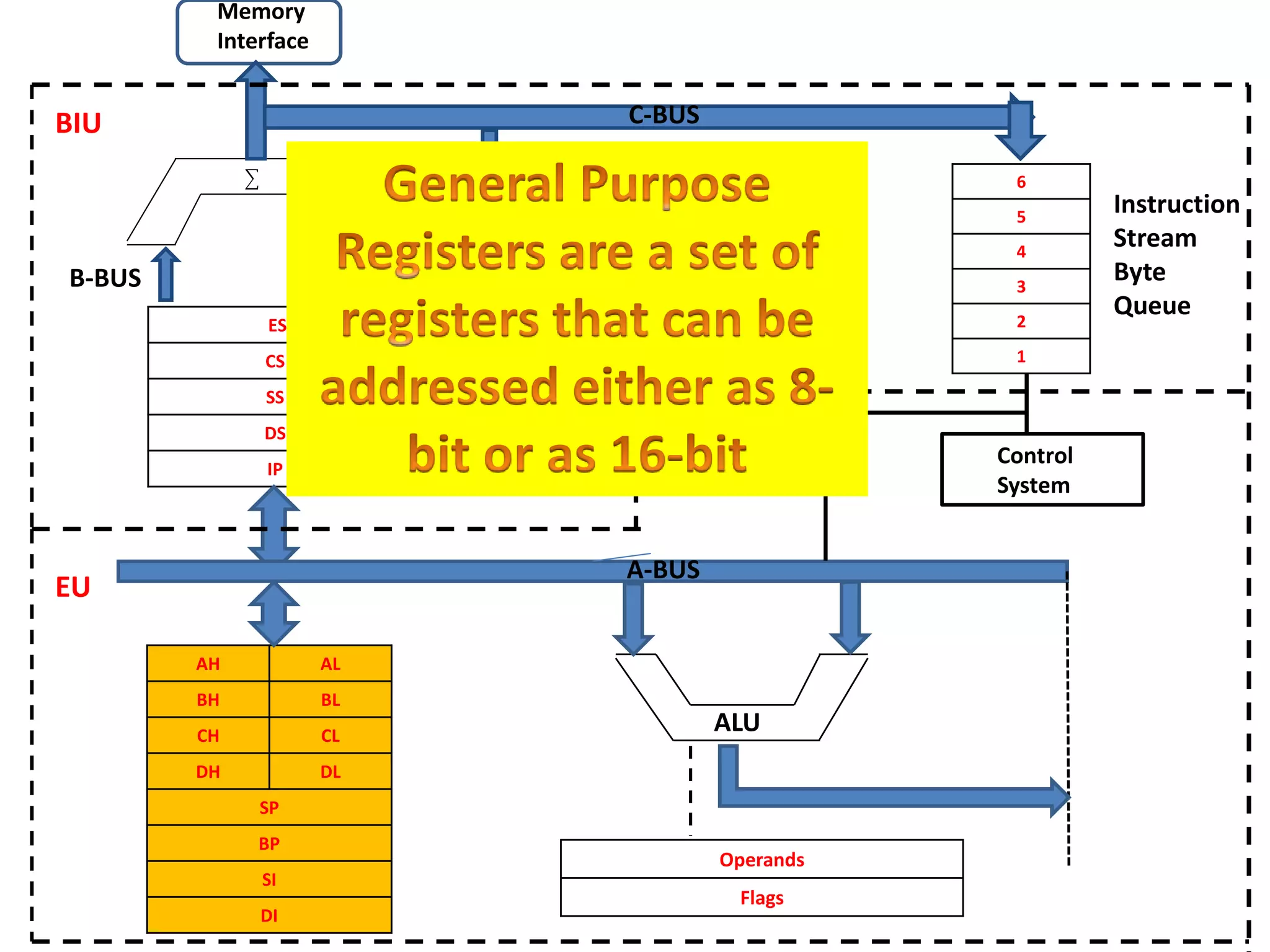

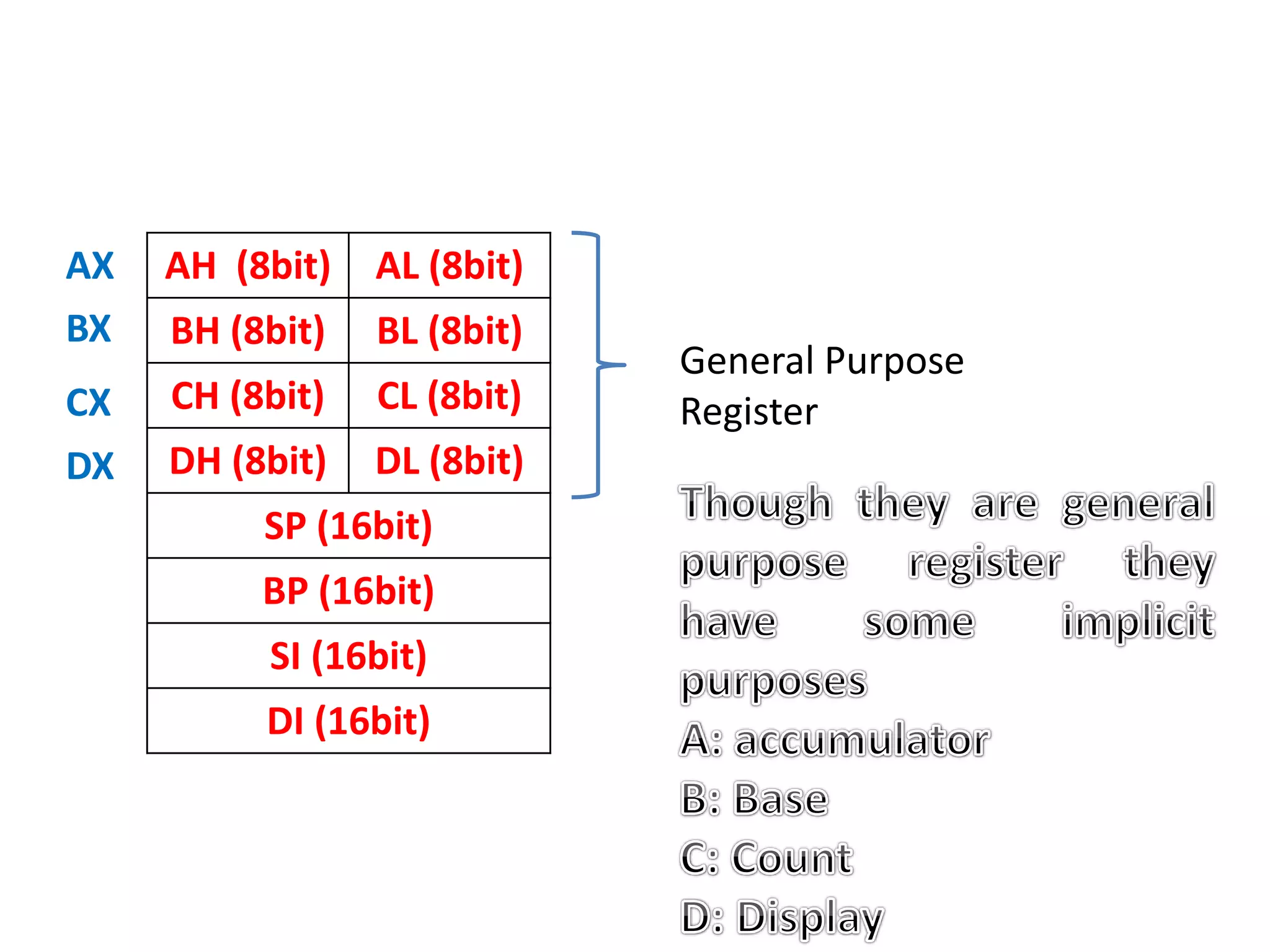

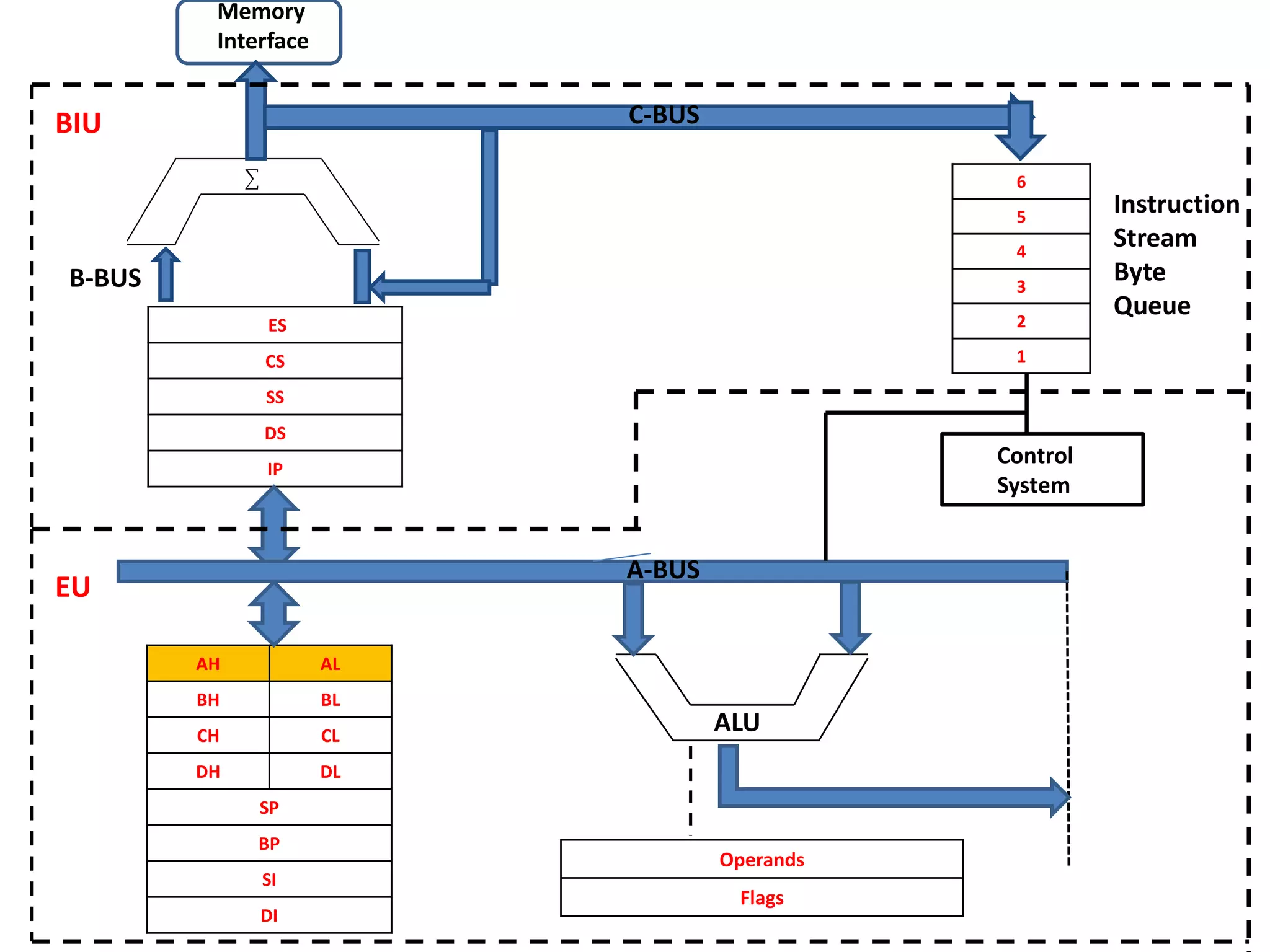

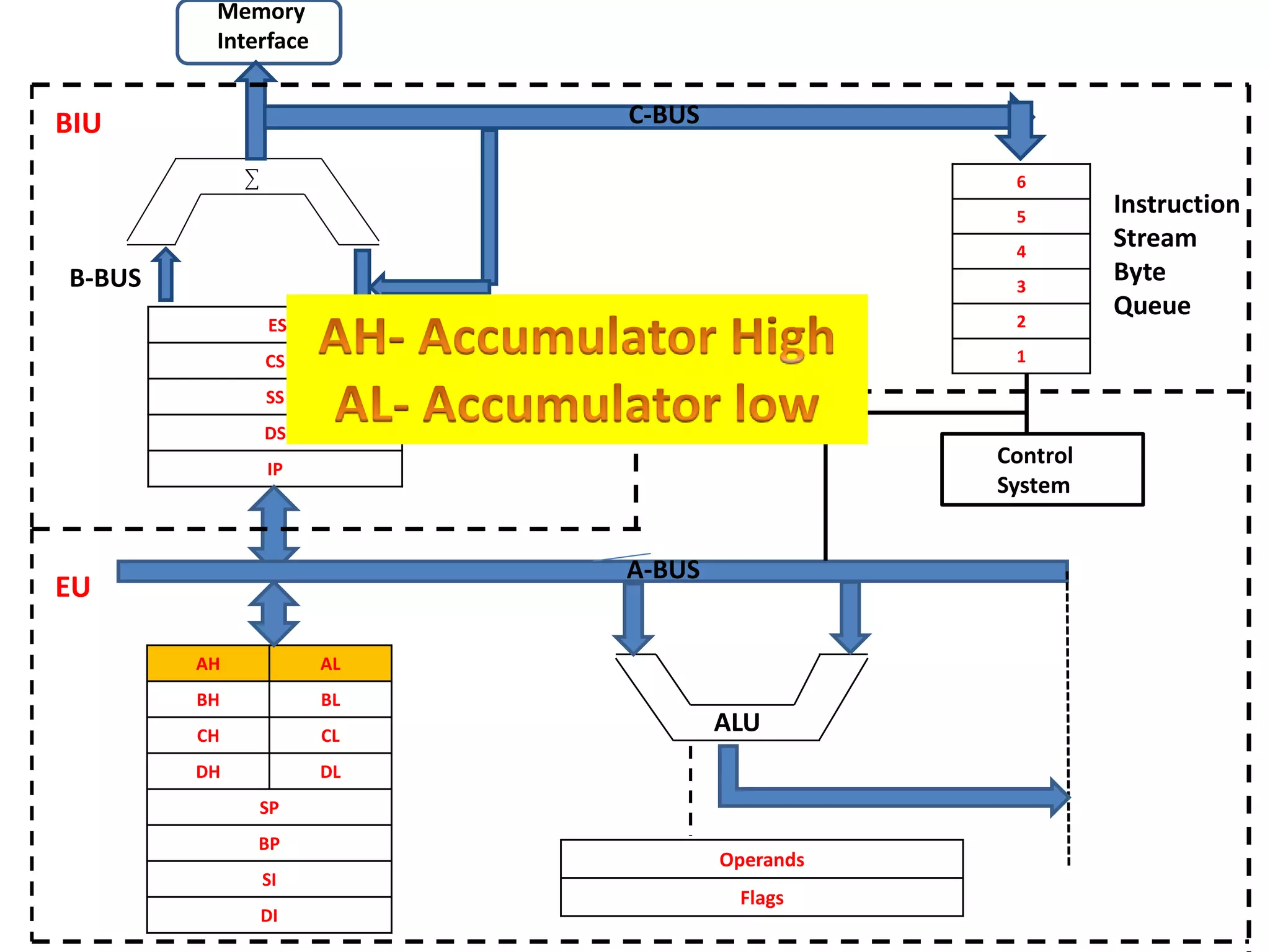

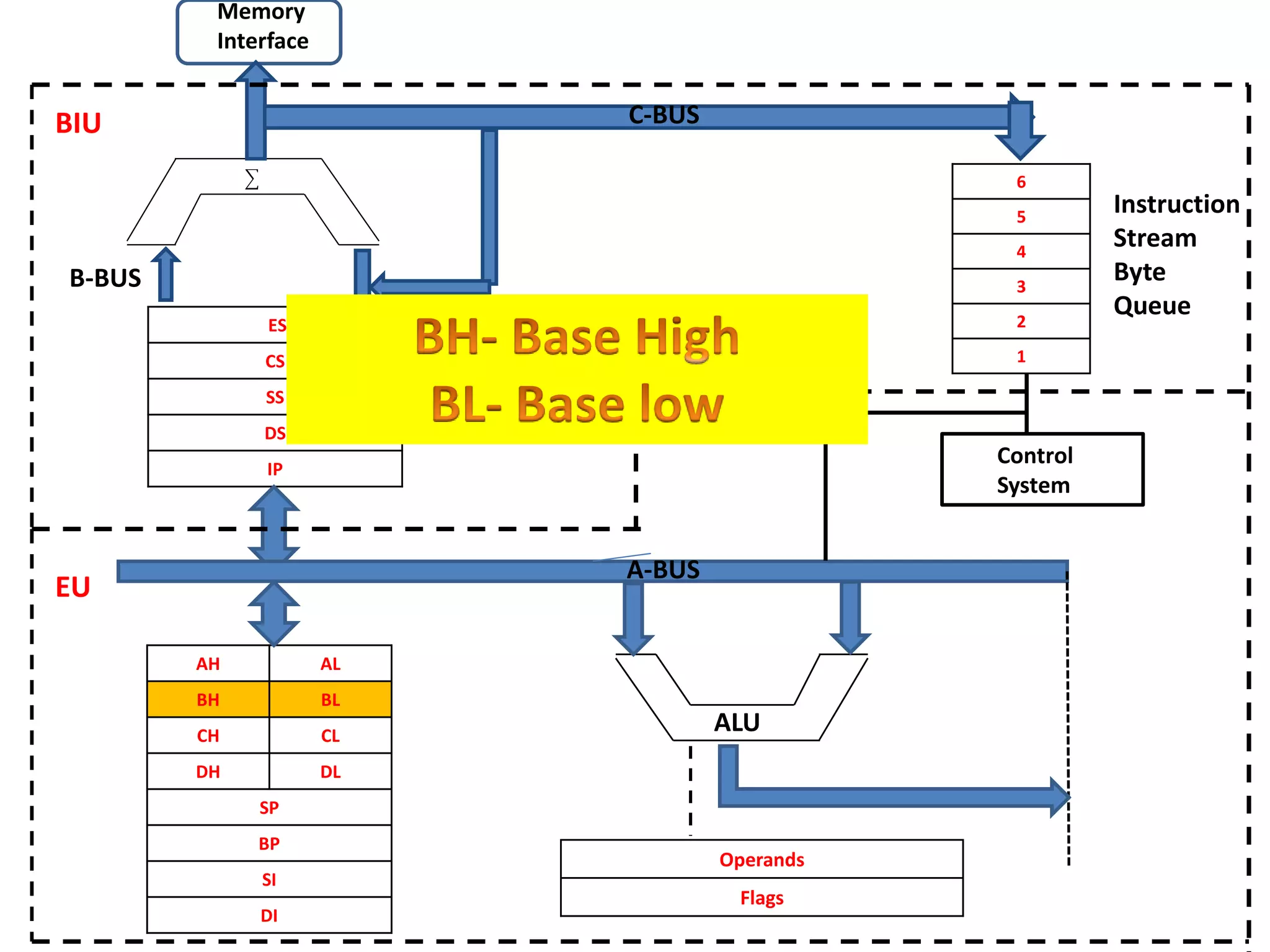

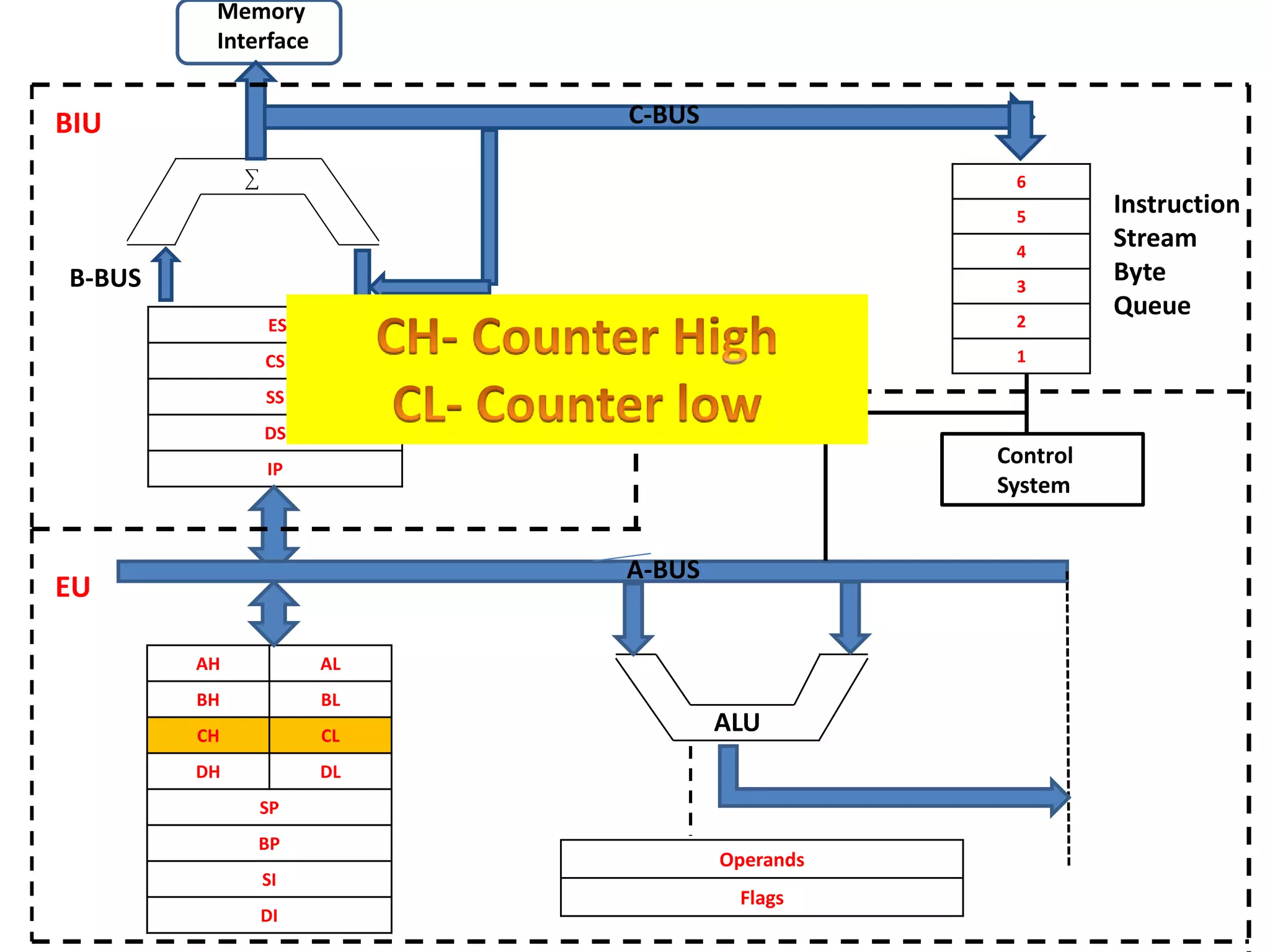

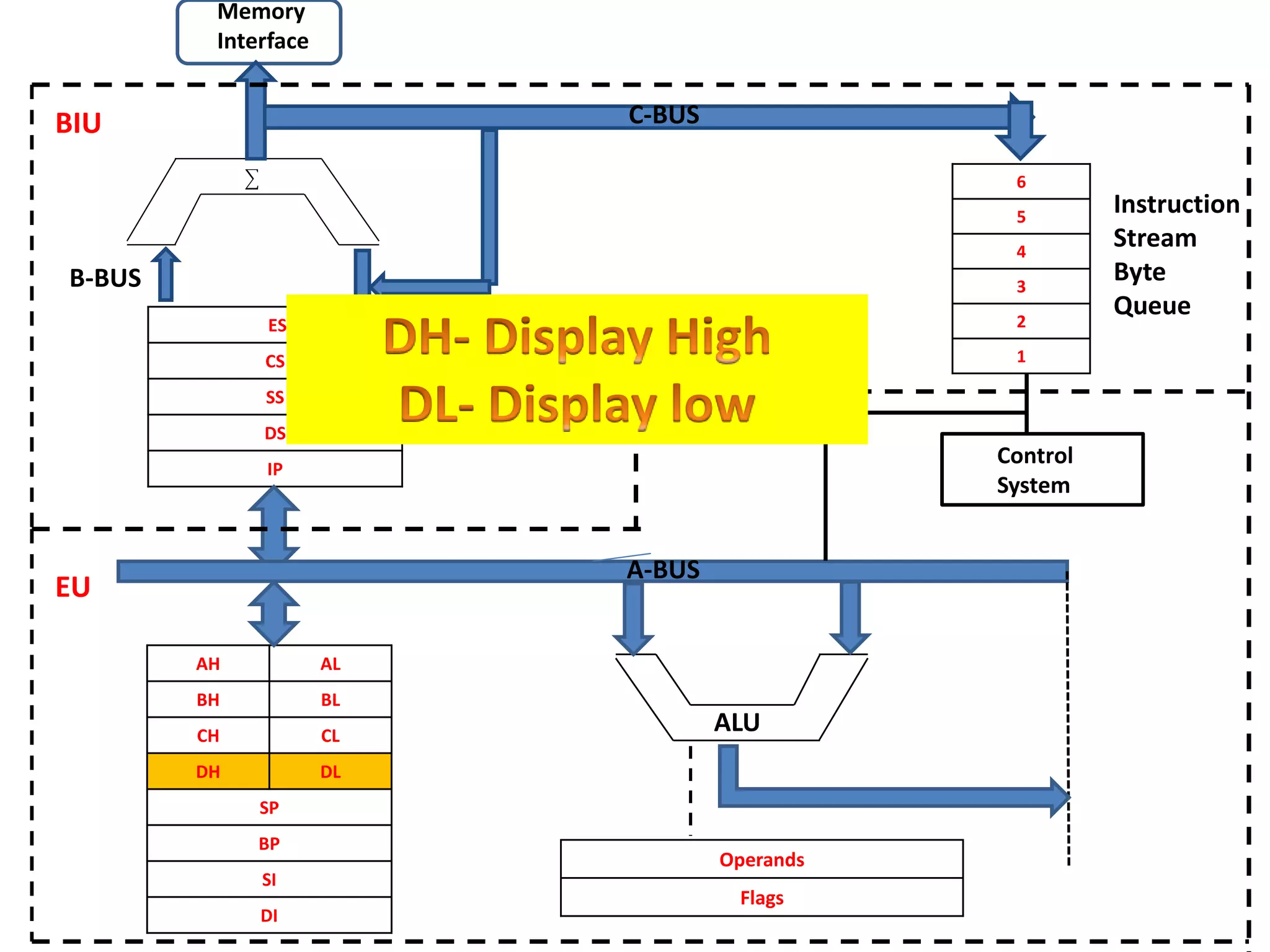

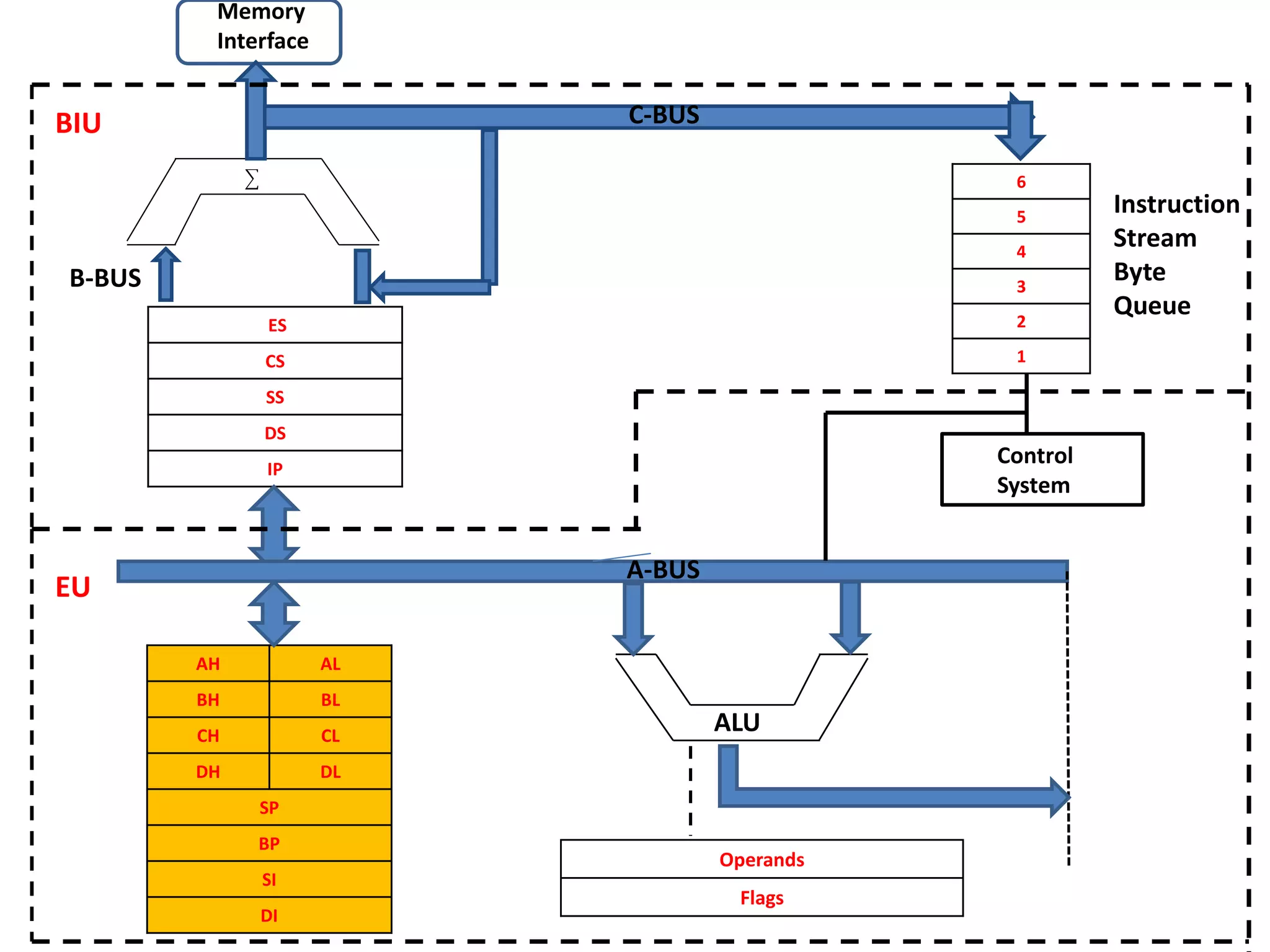

The 8086 architecture is a 16-bit processor that can transfer 16 bits of data at a time and perform arithmetic and logical operations on 16-bit data. It has a 16-bit data bus, 16-bit internal registers, and a 20-bit address bus. The architecture has two main sections - the Bus Interface Unit which handles data transfer and fetching instructions, and the Execution Unit which decodes and executes instructions using components like the ALU.