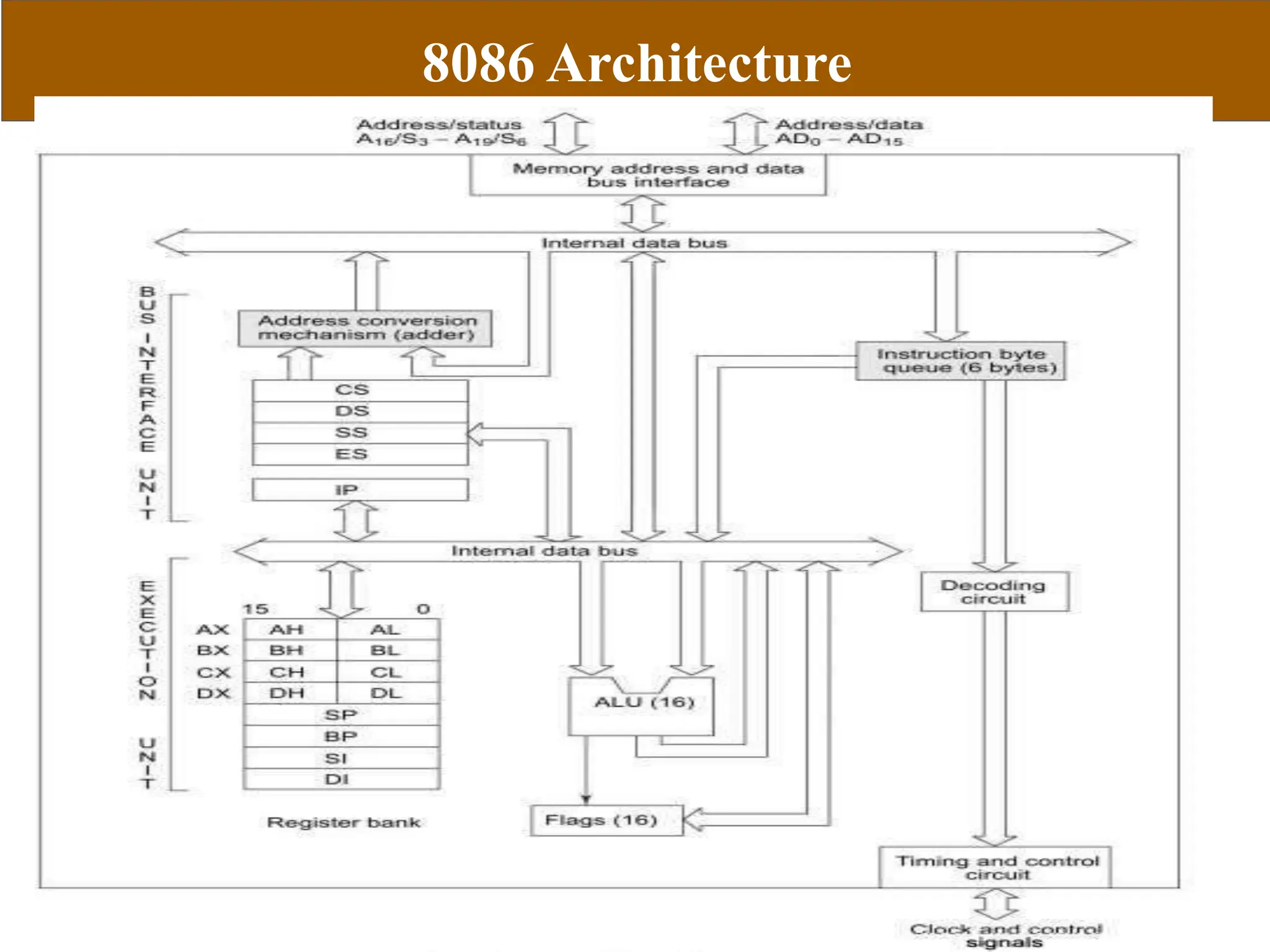

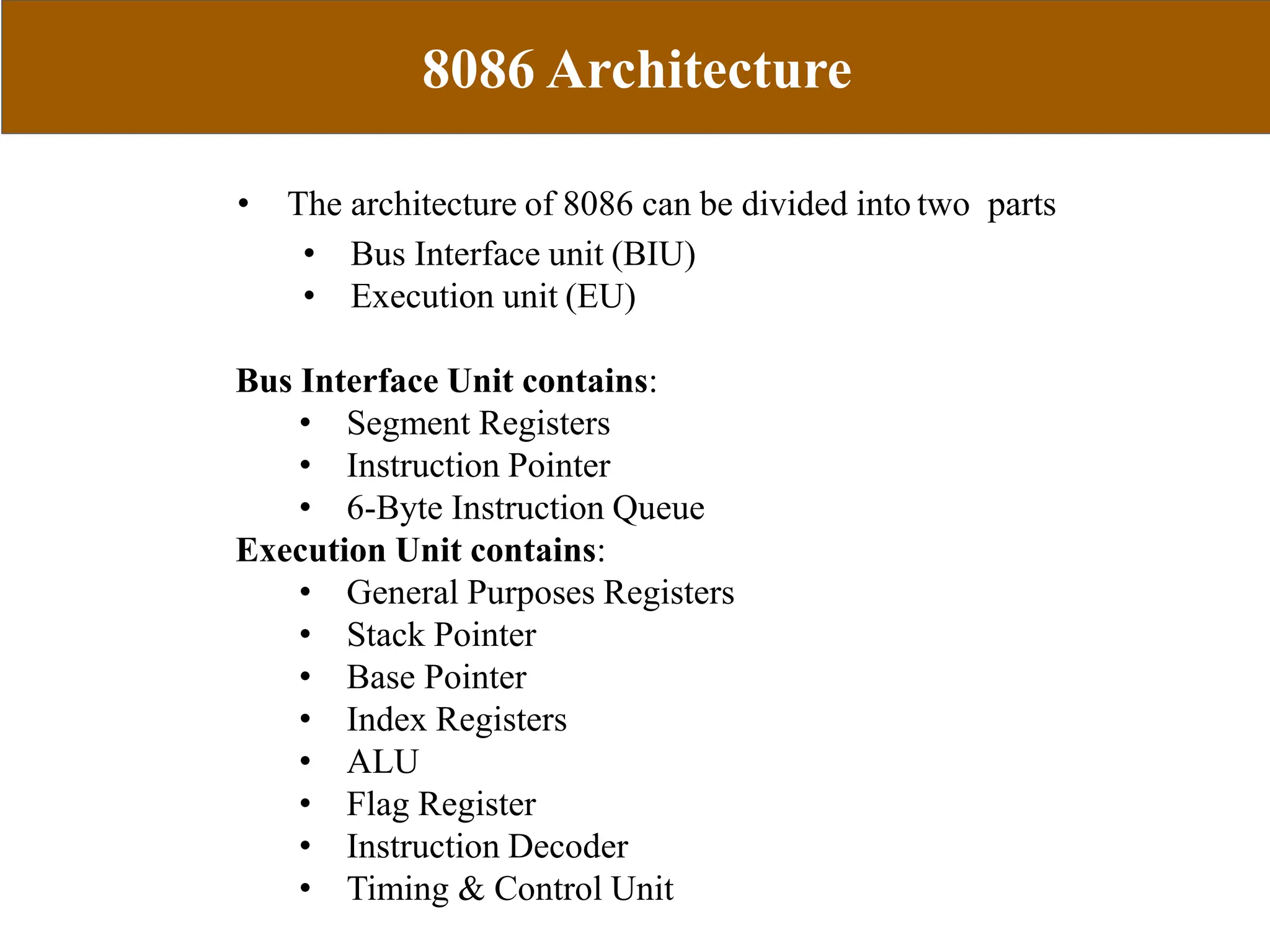

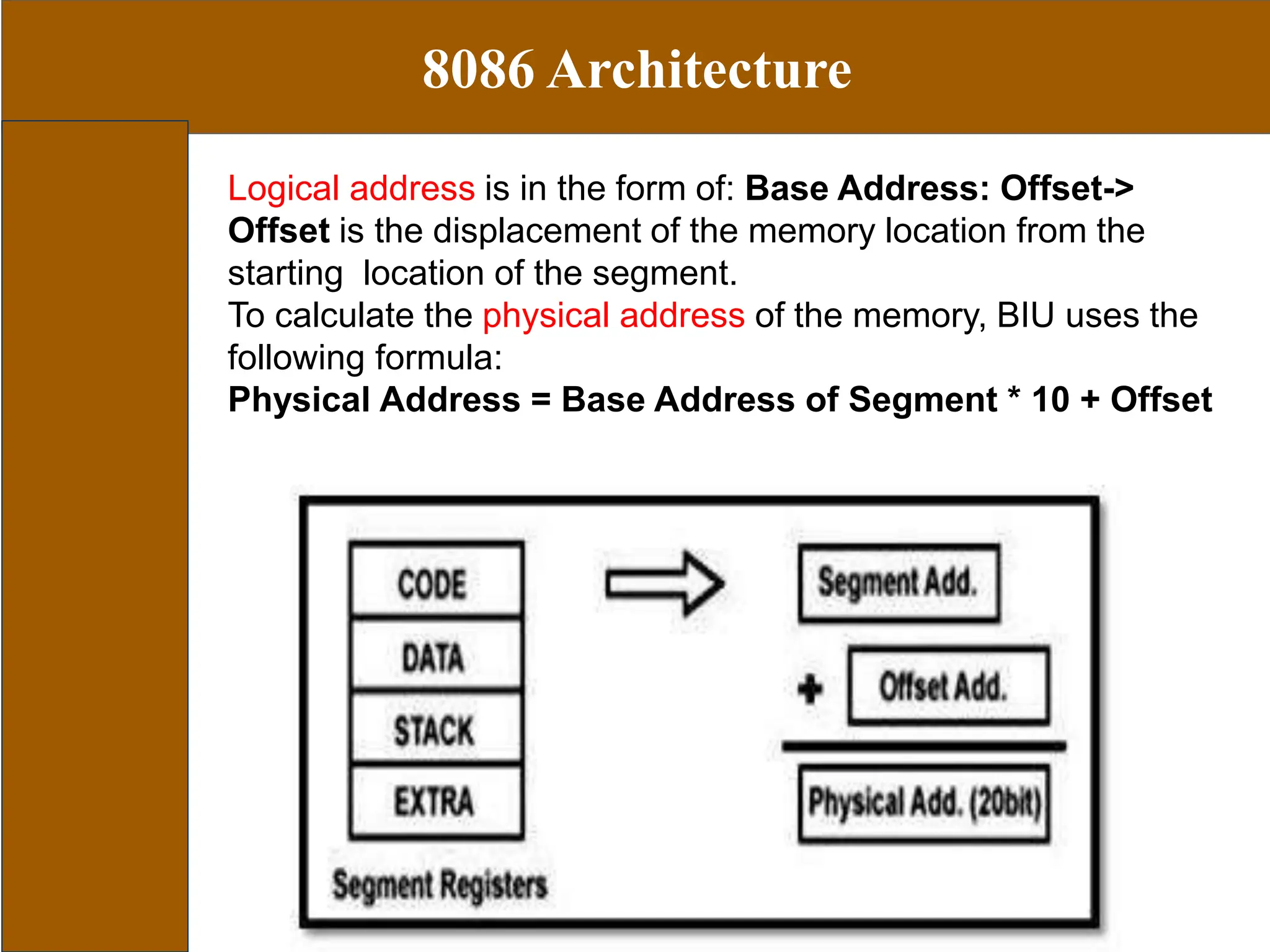

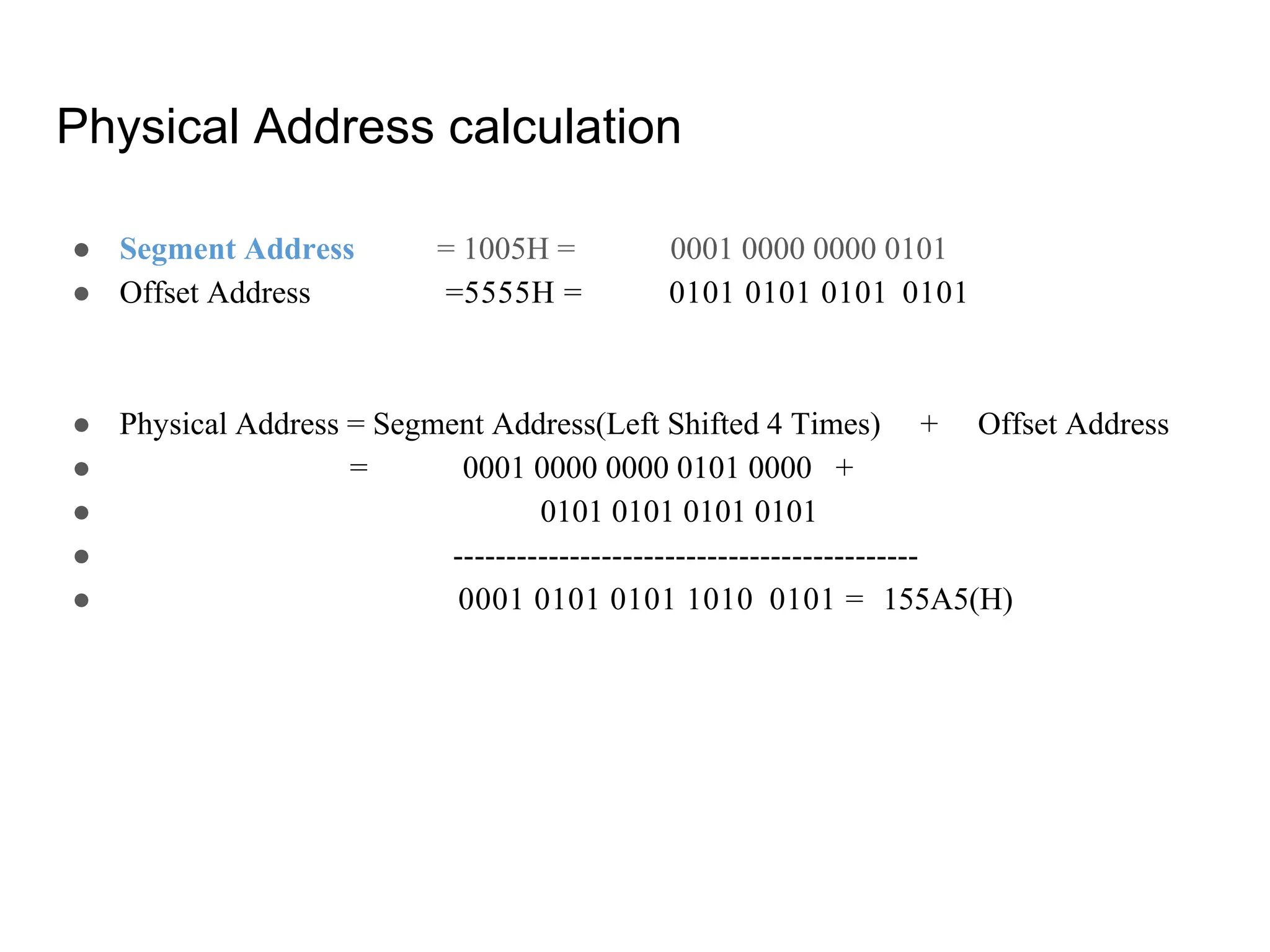

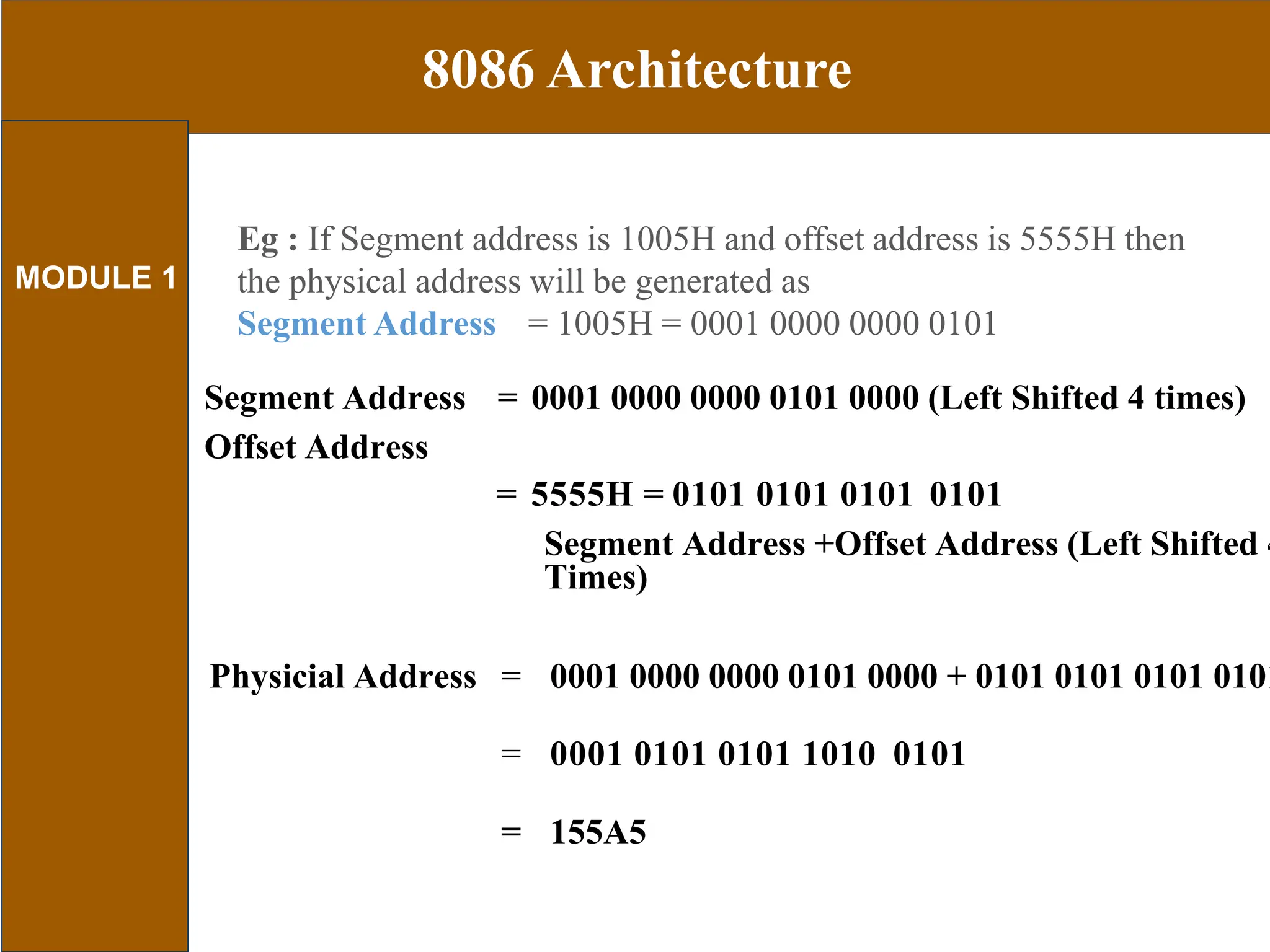

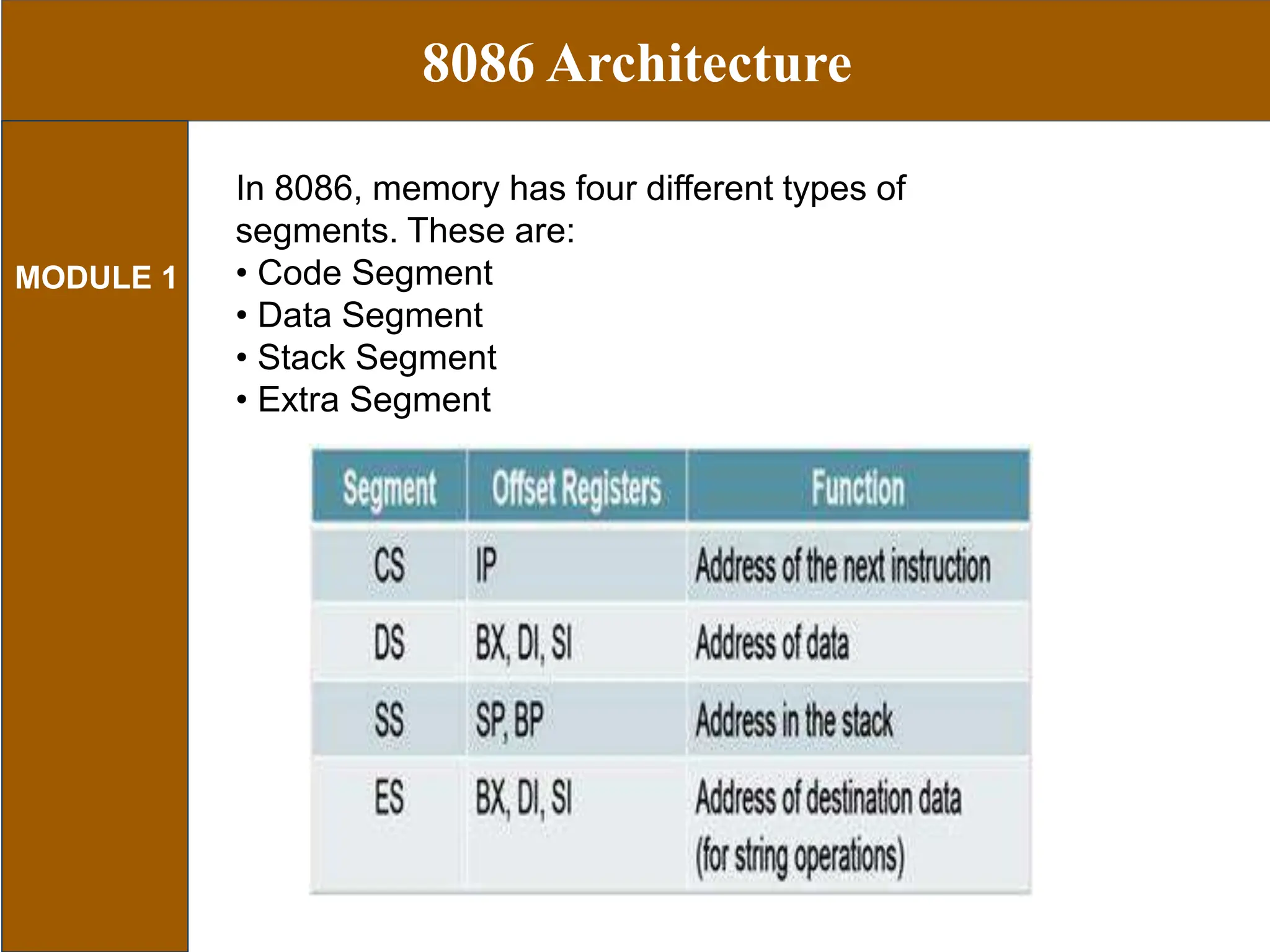

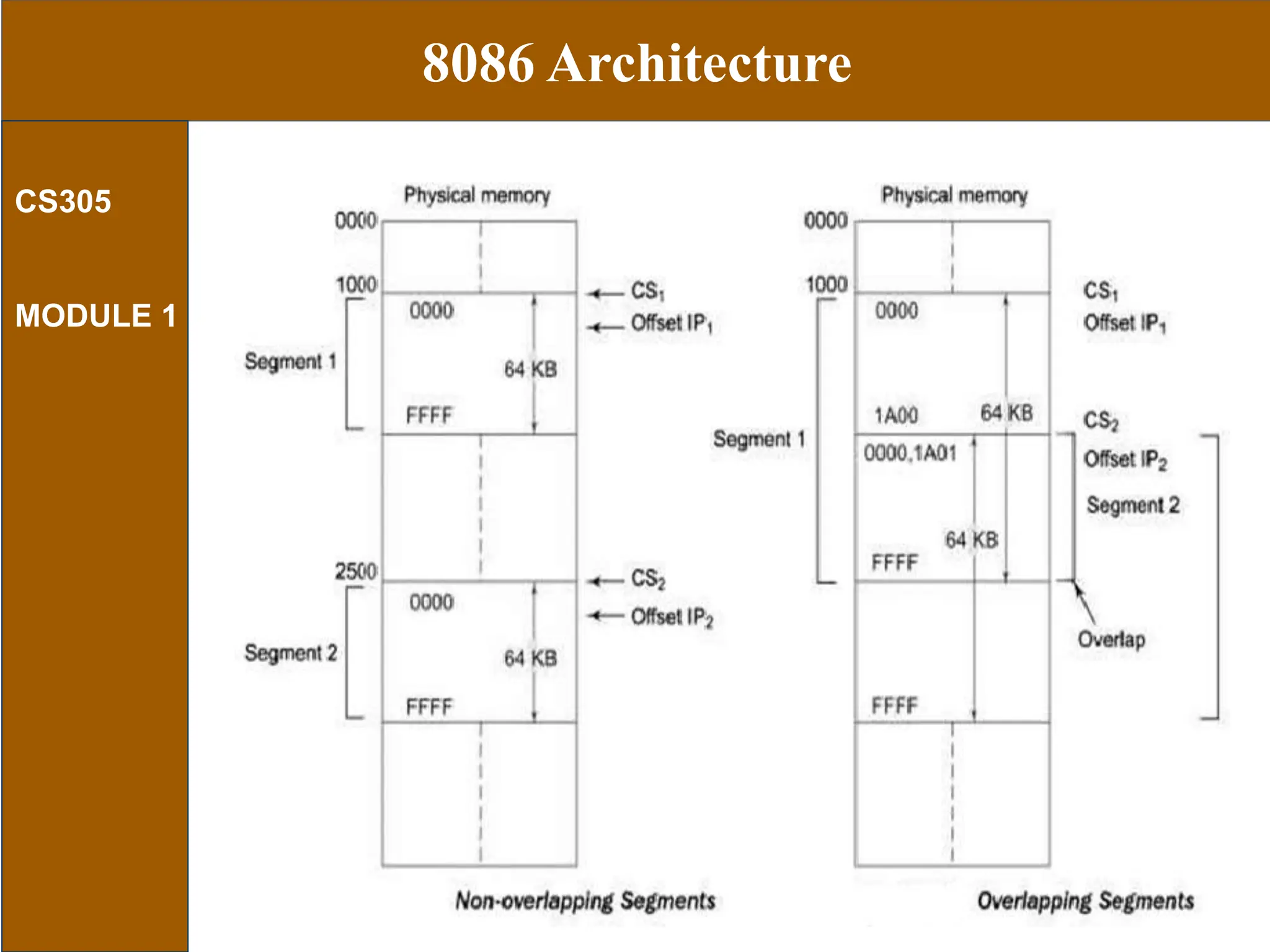

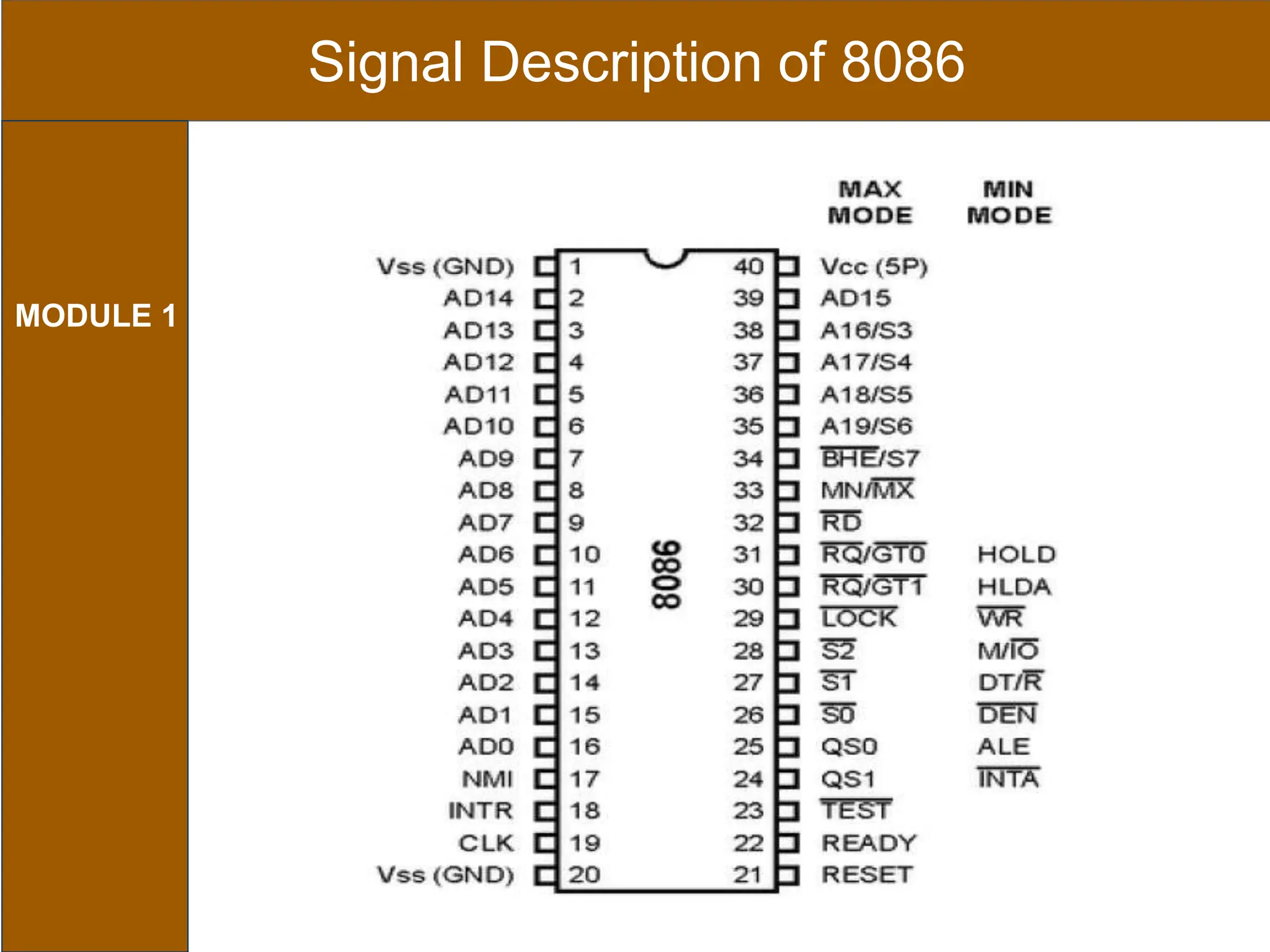

The document details the architecture of the 8086 microprocessor, including its components such as the bus interface unit and execution unit, and describes its segmented memory addressing scheme. It explains how physical and logical addresses are calculated, as well as the distinction between overlapping and non-overlapping segments. Additionally, the document highlights the advantages of the segmented memory scheme and provides information about the 8086's specifications and capabilities as the first 16-bit microprocessor.