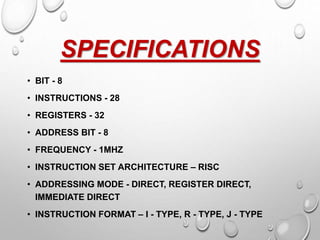

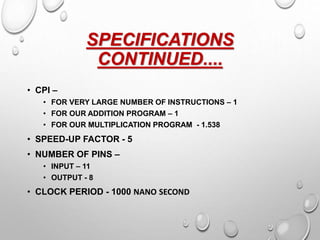

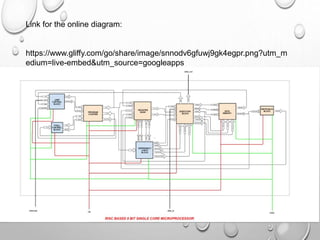

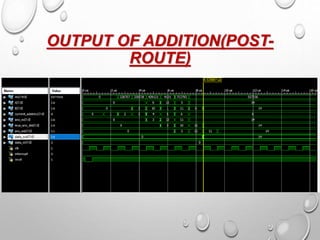

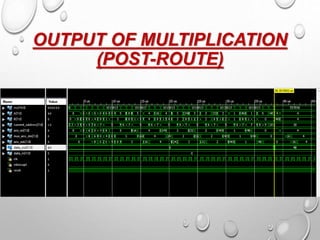

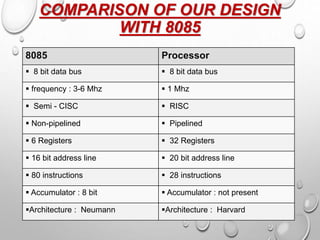

The document summarizes a group's presentation on designing an 8-bit MIPS processor. It describes the processor as an 8-bit RISC-based single core microprocessor that can perform arithmetic and logical operations. It provides details on the motivation, specifications, architecture, instruction formats, performance comparisons to an 8085 processor, challenges faced, and feedback from instructors. The group implemented a pipelined processor with 32 registers, 28 instructions, and addressed memory separately from the data memory.