This document is an instructional presentation on digital electronics and the fundamentals of the 8085 microprocessor, intended for educational purposes. It covers the architecture, instruction set, addressing modes, and operational features of the 8085 microprocessor, providing systematic content that includes lecture-wise breakdowns, summaries, and practice questions. The material aims to enhance the teaching methods and understanding of microprocessor functionality among students.

![LECTURE 50:- MICROPROCESSOR Subroutines

123

123

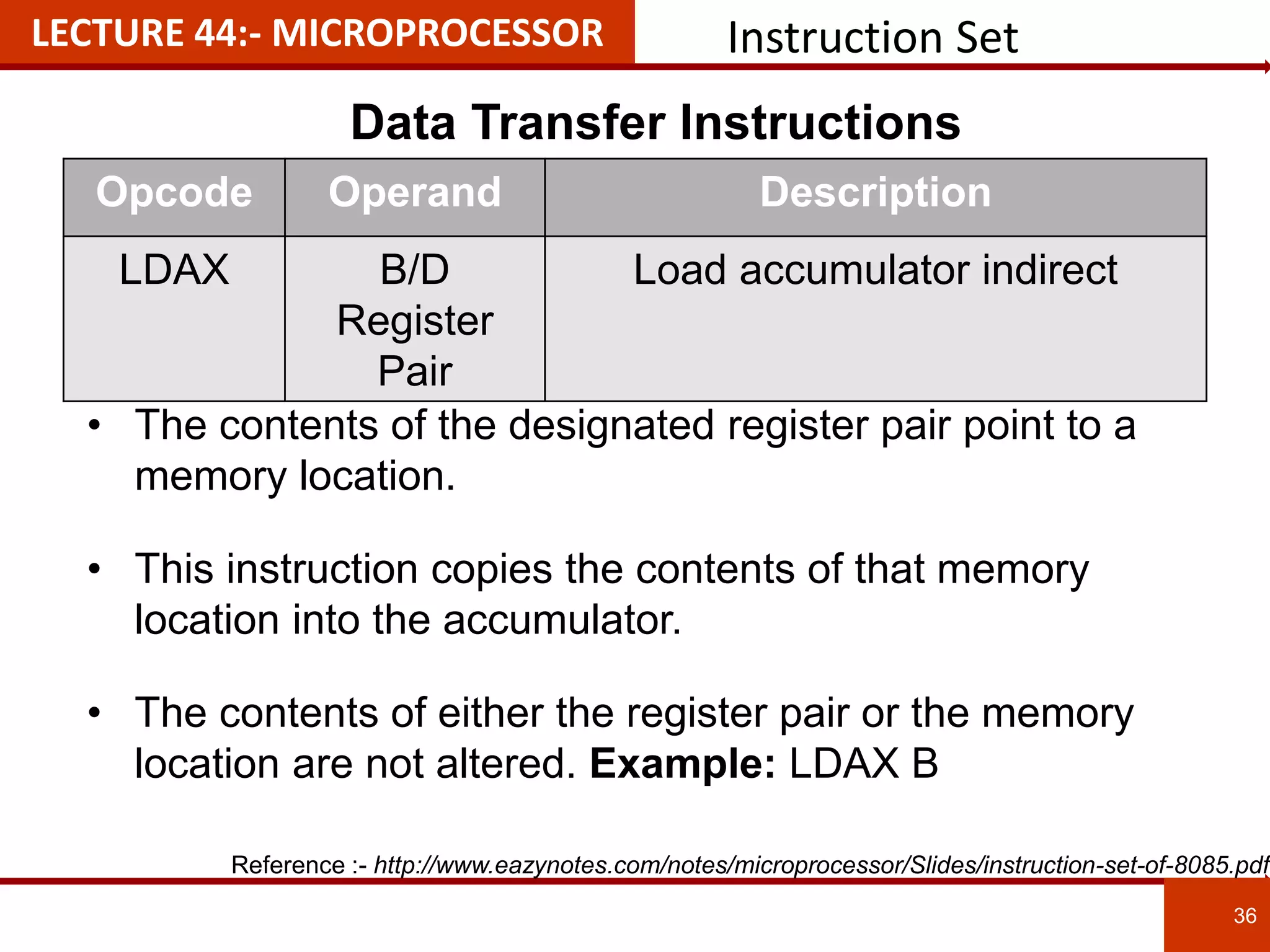

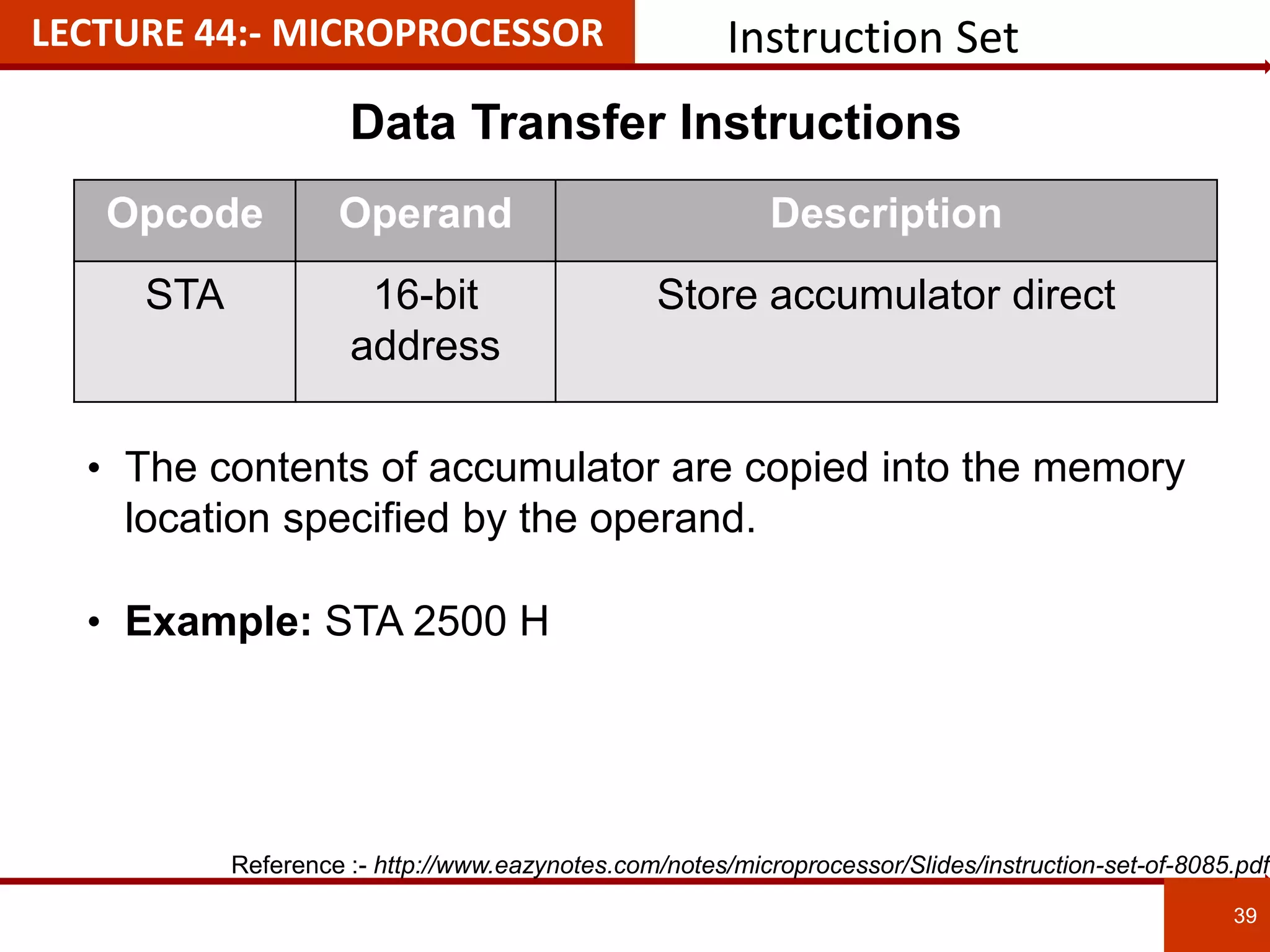

The CALL Instruction

• MP Reads the subroutine address from the next two

memory location and stores the higher order 8bit of the

address in the W register and stores the lower order 8bit

of the address in the Z register

–Pushe the address of the instruction immediately

following the CALL onto the stack [Return address]

–Loads the program counter with the 16-bit address

supplied with the CALL instruction from WZ register.

Reference :- http://www.aust.edu/cse/moinul/Stack_and_Subroutine.pdf](https://image.slidesharecdn.com/defm-ii-191029082037/75/Digital-Electronics-Fundamental-of-Microprocessor-II-123-2048.jpg)

![191

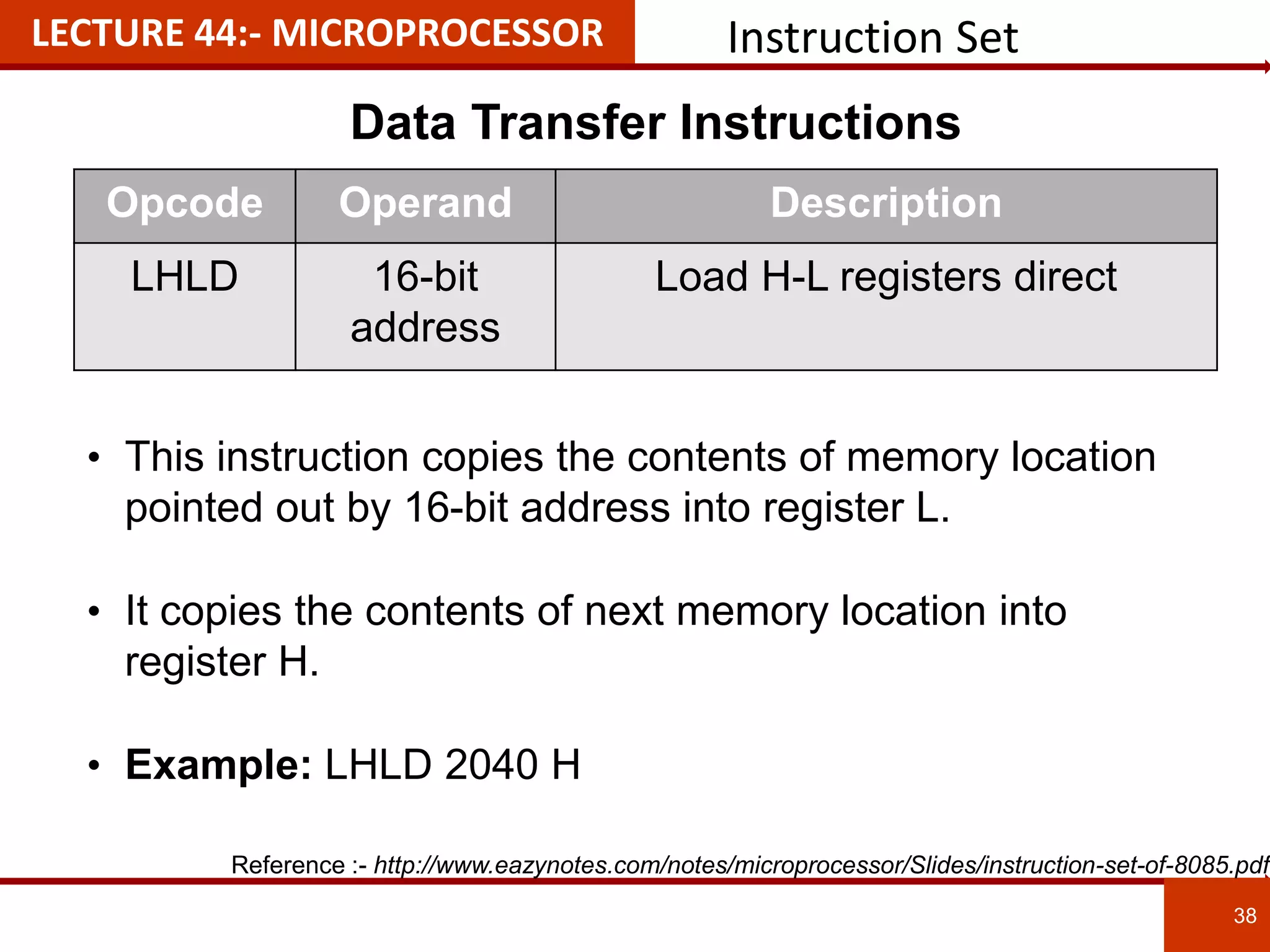

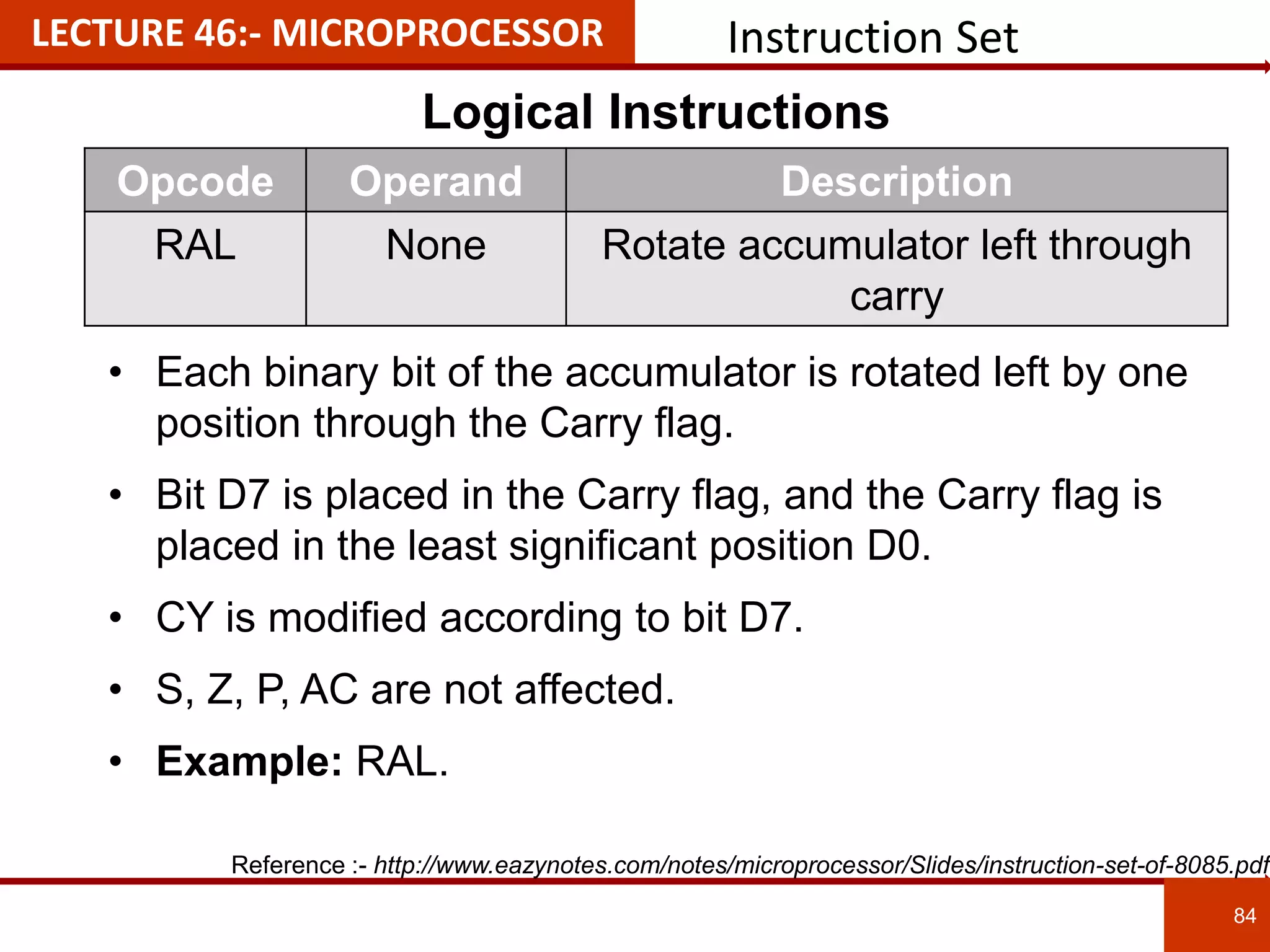

Write a program and to generate square generator using

DAC.

Start: MVI A,00 :Intialise ‘A’ with ’00’

OUT C8 :Load the control words

CALL Delay :Call delay sutroutine

MVI A,FF :Intialise ‘A’ with ‘FF

OUT C8 :A -> C8

CALL Delay :Call delay subroutine

JMP Start :Jump to start

Delay: MVI B,05 :B -> 05

Loop1:MVI C,FF :[C] => FF

Loop2:DCR C :Decrement ‘C’ register

JNZ Loop2 :Jump on no zero

DCR B :Decrement ‘B’ register

JNZ Loop1 :Jump on n zero

RET :Return to main program

Assembly Language ProgramLECTURE 60:- INTERRUPT](https://image.slidesharecdn.com/defm-ii-191029082037/75/Digital-Electronics-Fundamental-of-Microprocessor-II-191-2048.jpg)