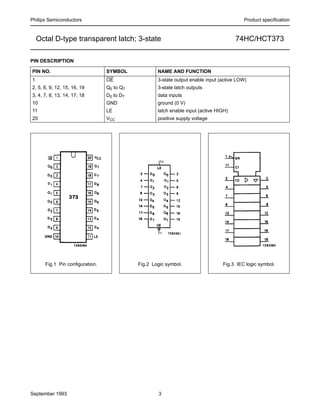

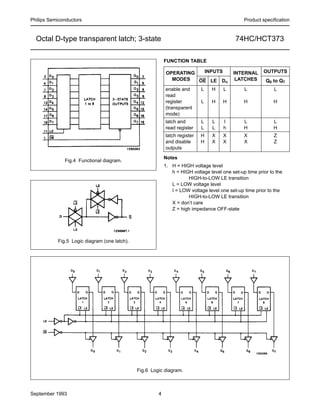

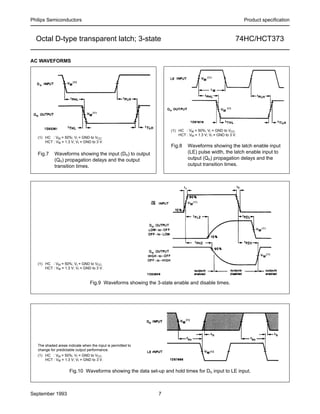

The document provides information about the 74HC/HCT373 integrated circuit. It is an octal D-type transparent latch with 3-state outputs. It features separate data and latch enable inputs for each latch, as well as a common 3-state output enable input. When the latch enable input is high, data enters the latches transparently from the data inputs. When low, the latches store the previous data. The 3-state outputs provide high impedance when the output enable is high.