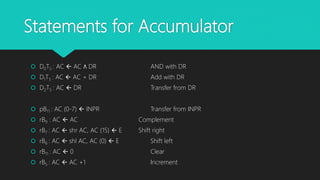

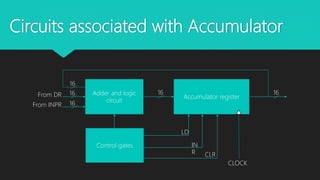

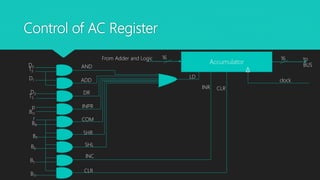

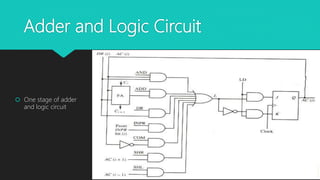

The accumulator logic receives inputs from the arithmetic circuit (AC), data register (DR), and input register. It performs logic and arithmetic operations on these inputs and stores the results. These operations include AND, addition, transfer from DR, transfer from input register, complement, shift right/left, increment, and clear. The accumulator register is controlled by gates and stores the output of the adder and logic circuit. The adder and logic circuit consists of 16 identical stages, each performing logic operations on one bit and using a full adder to generate the output bit.