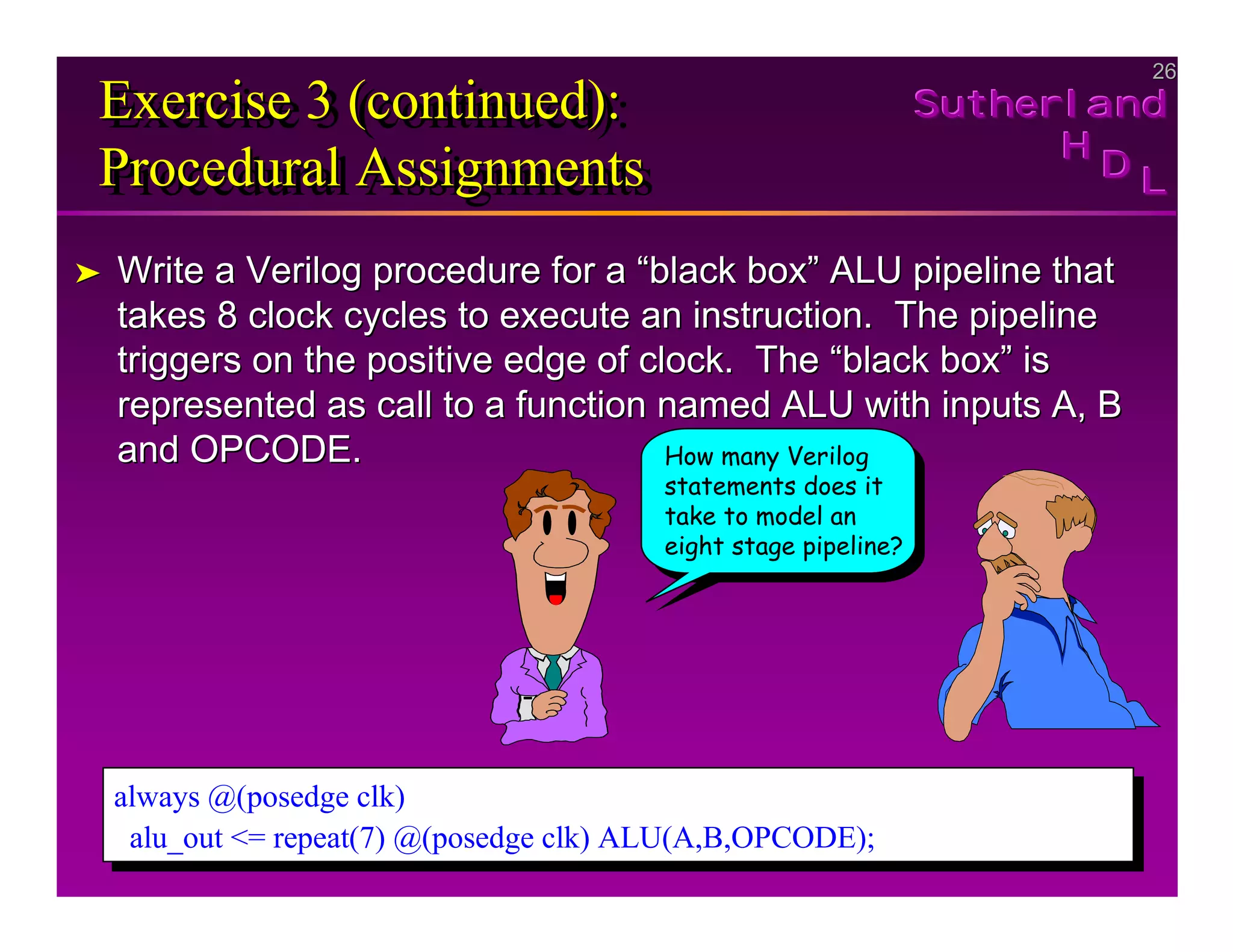

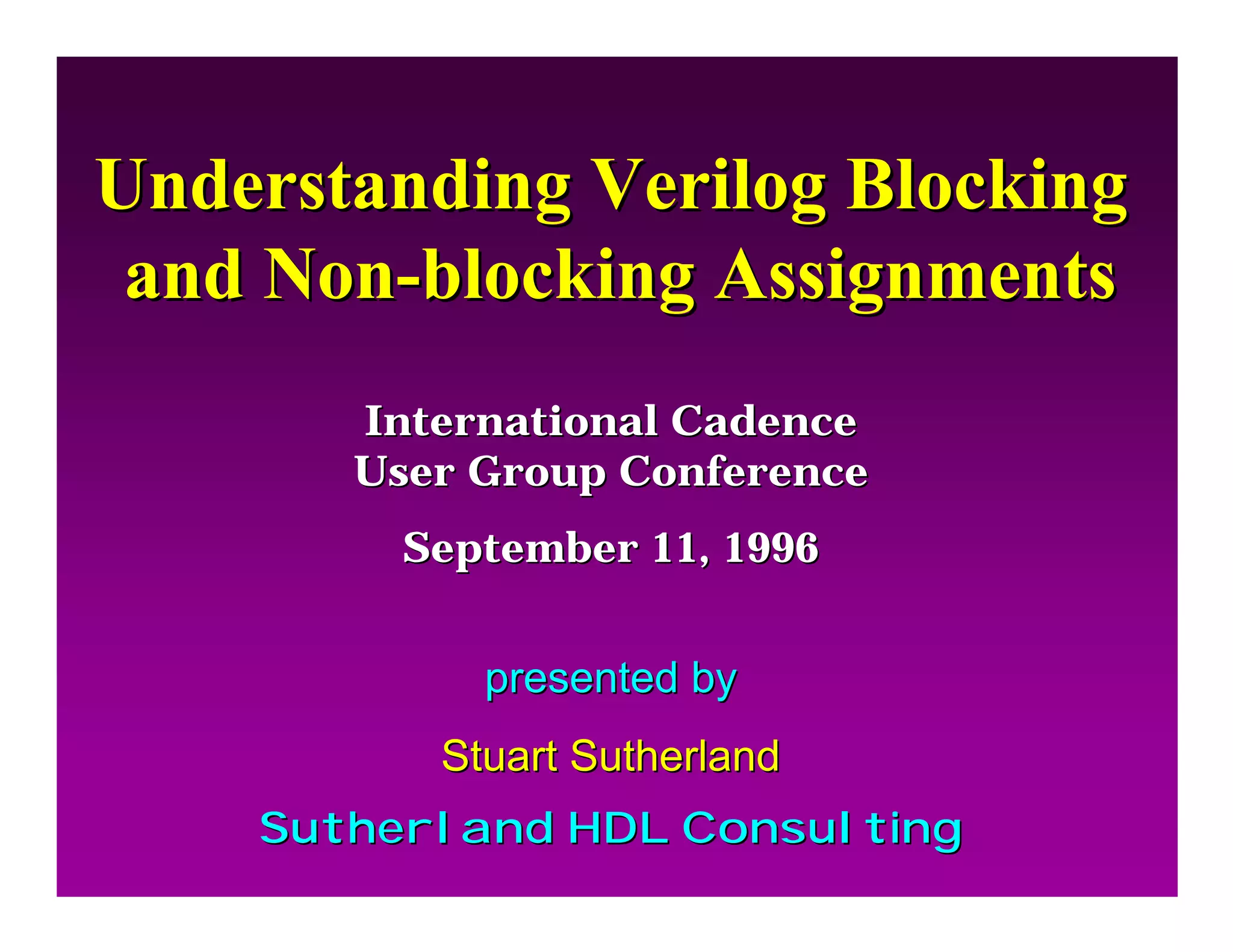

This document summarizes a presentation on understanding blocking and non-blocking assignments in Verilog. The key points are:

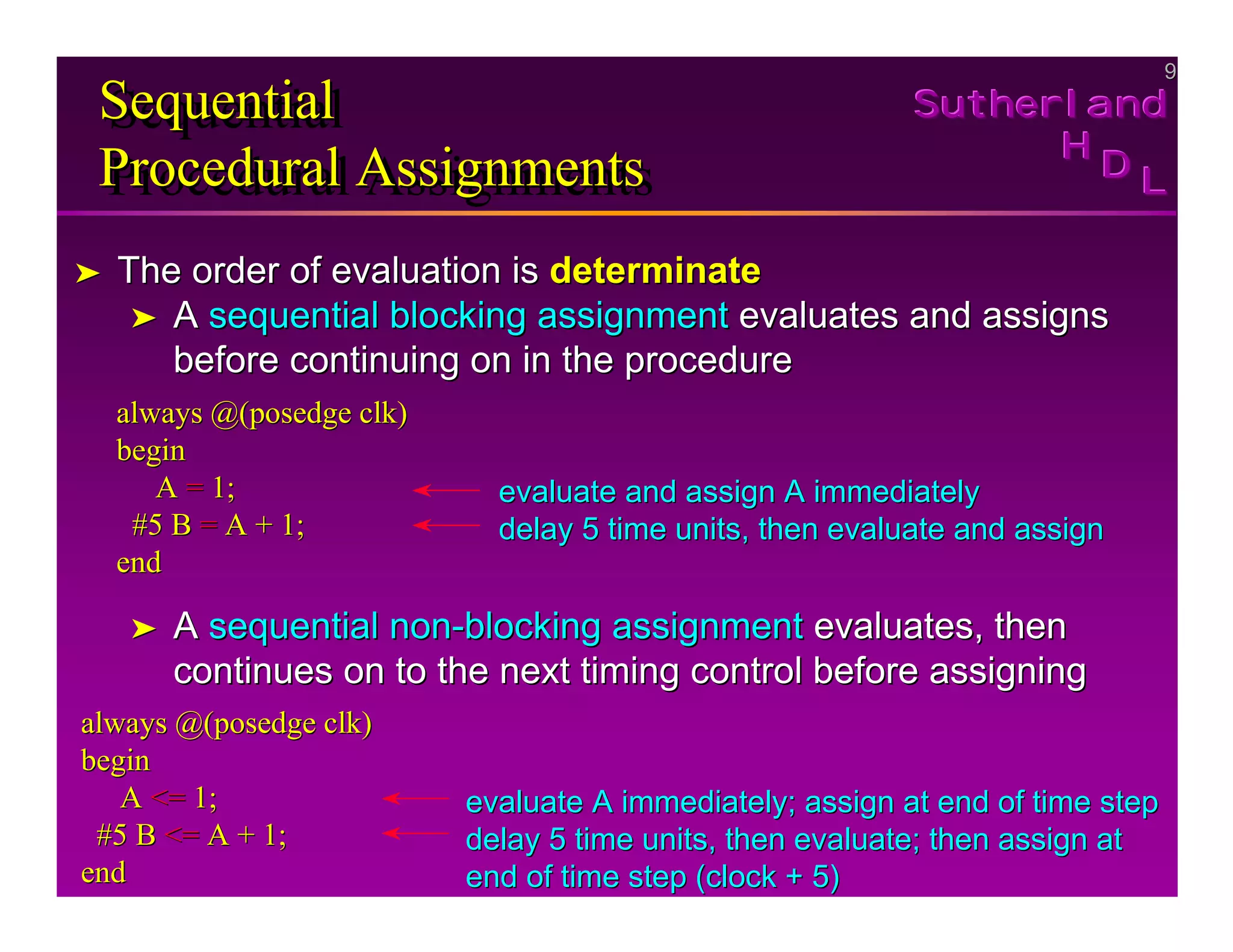

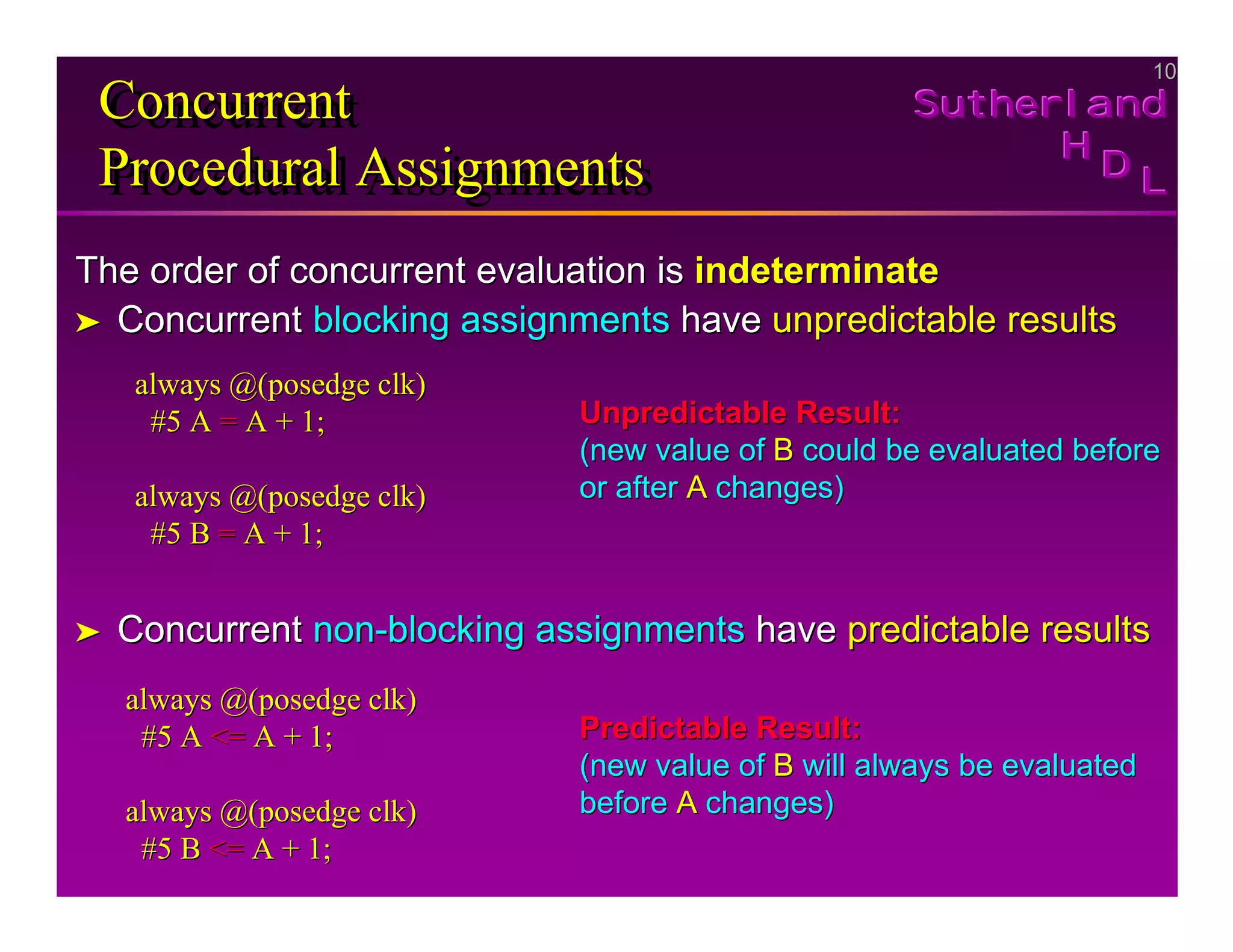

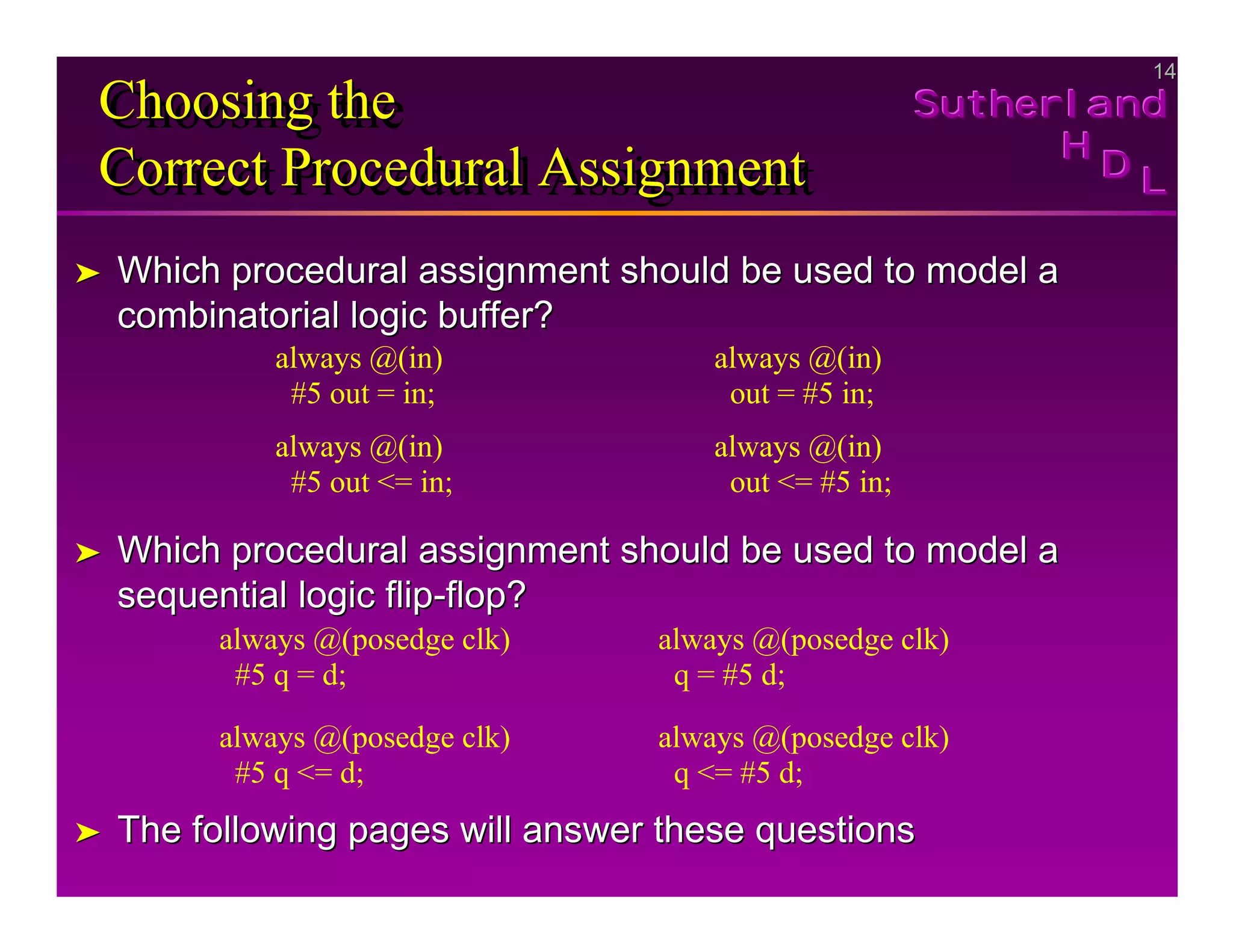

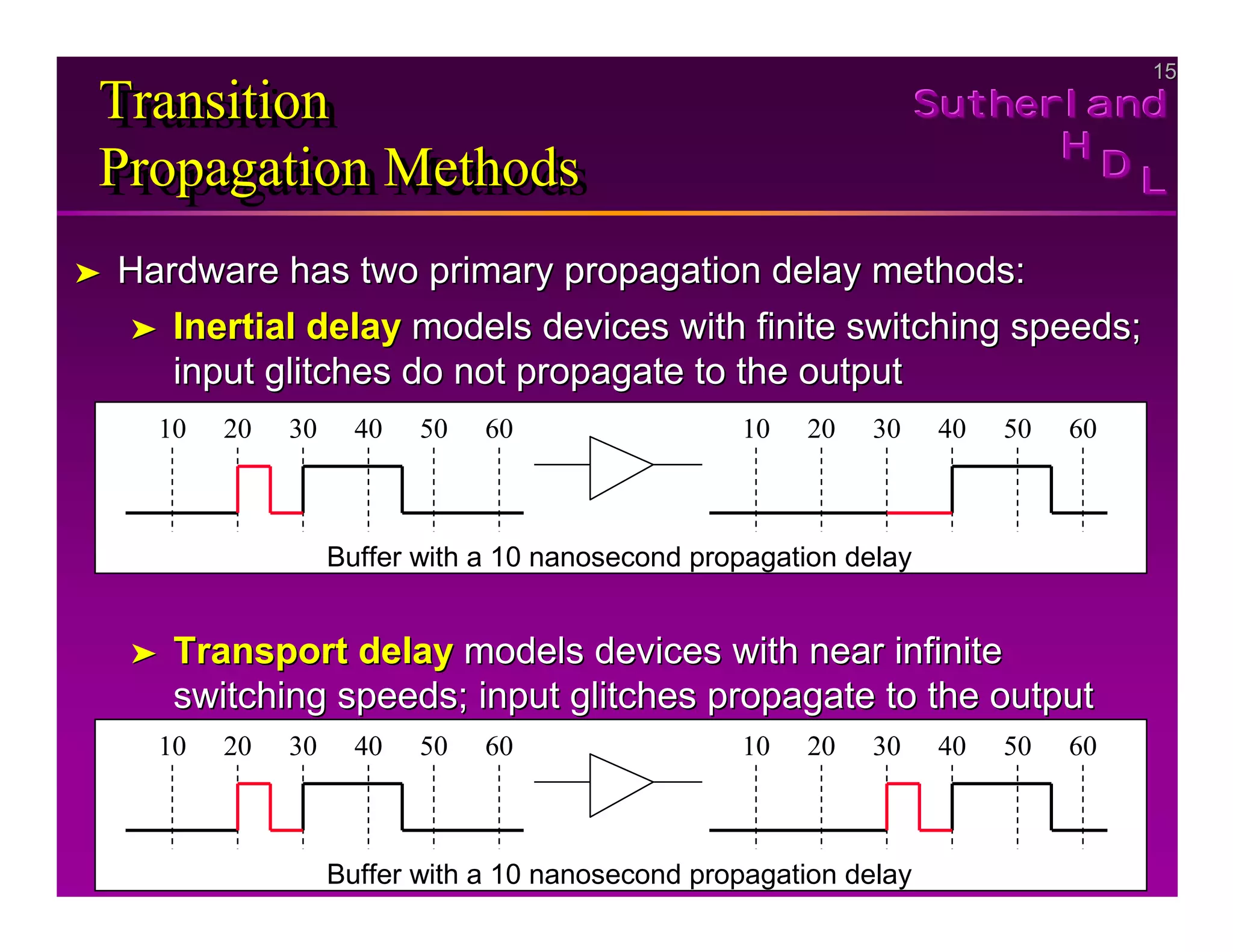

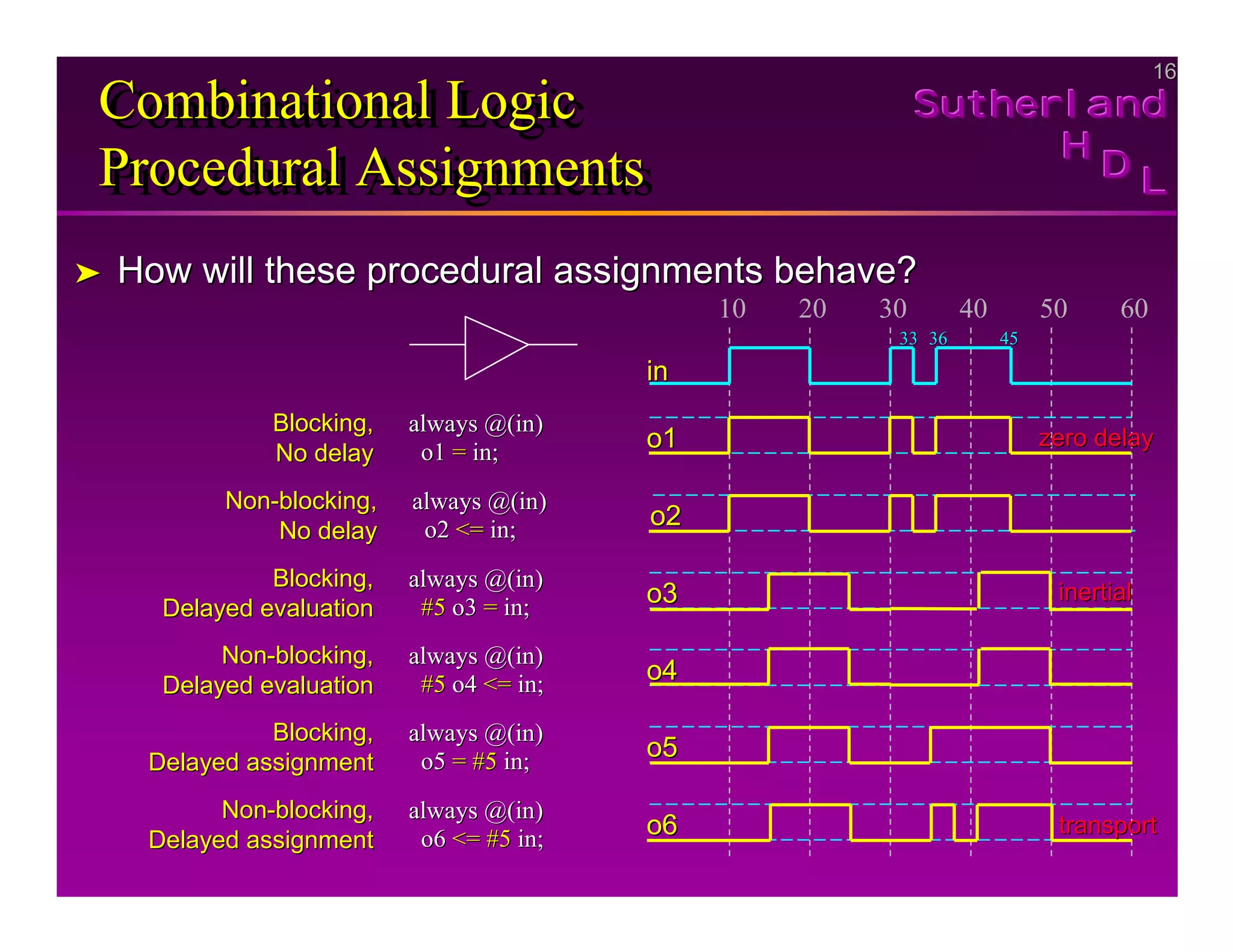

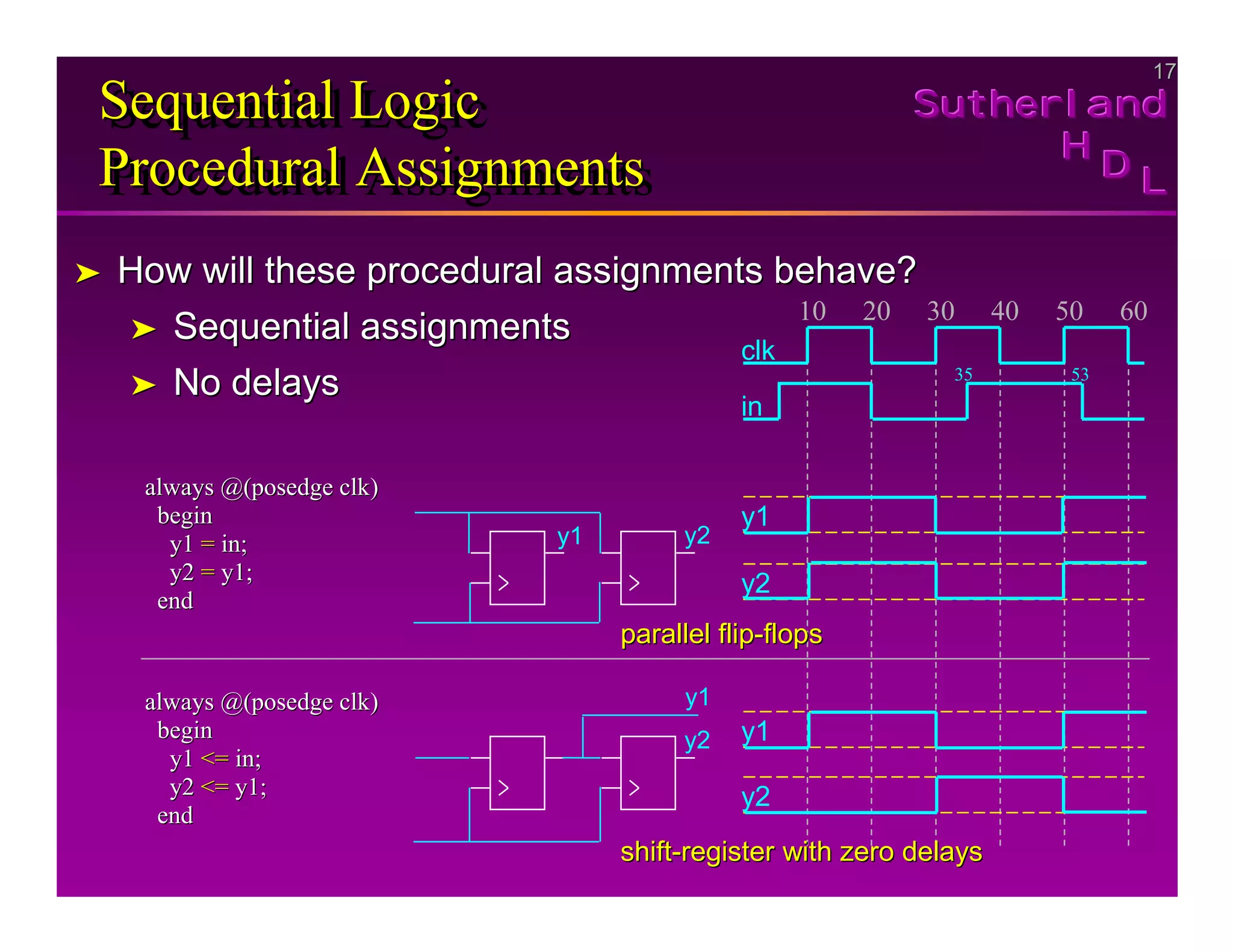

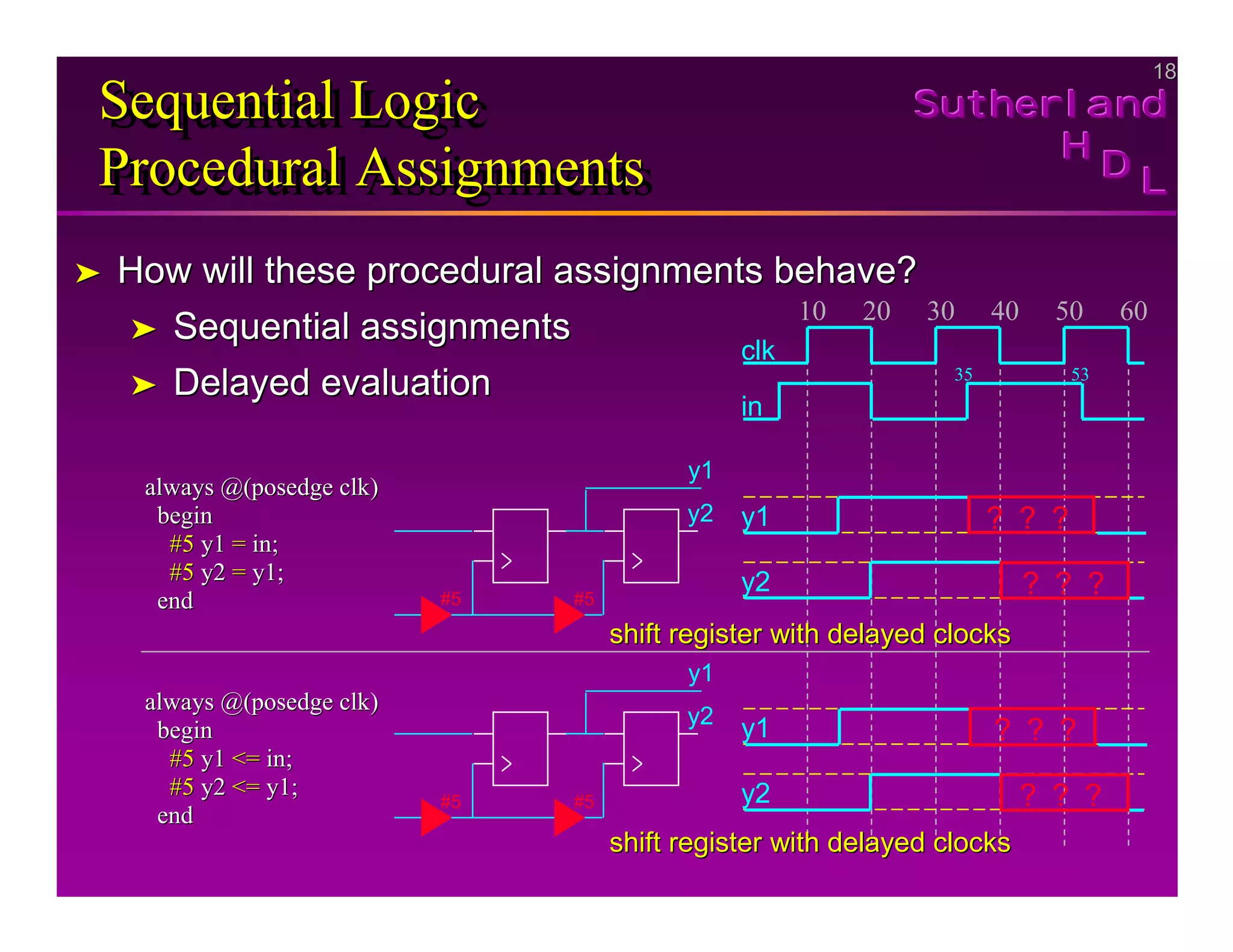

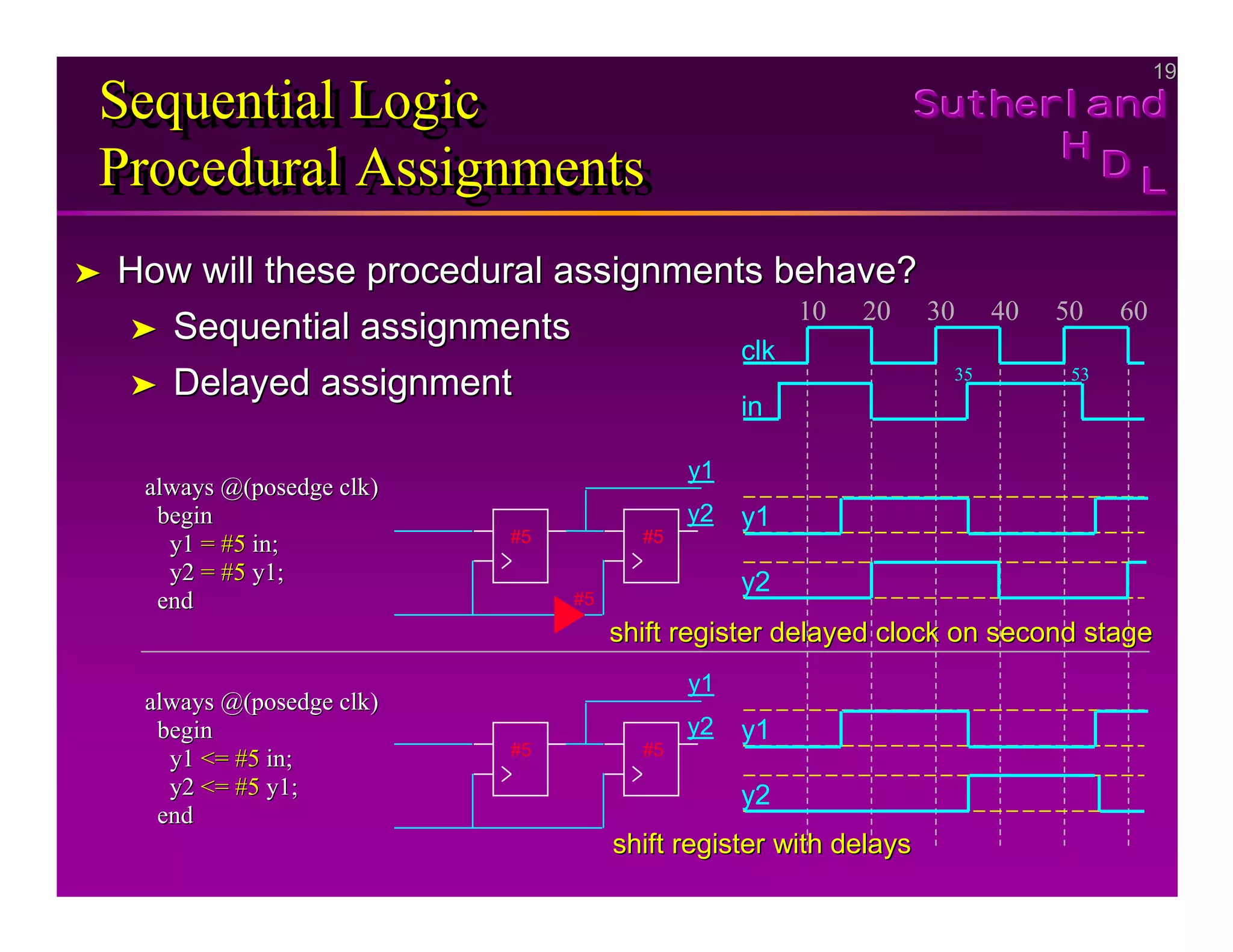

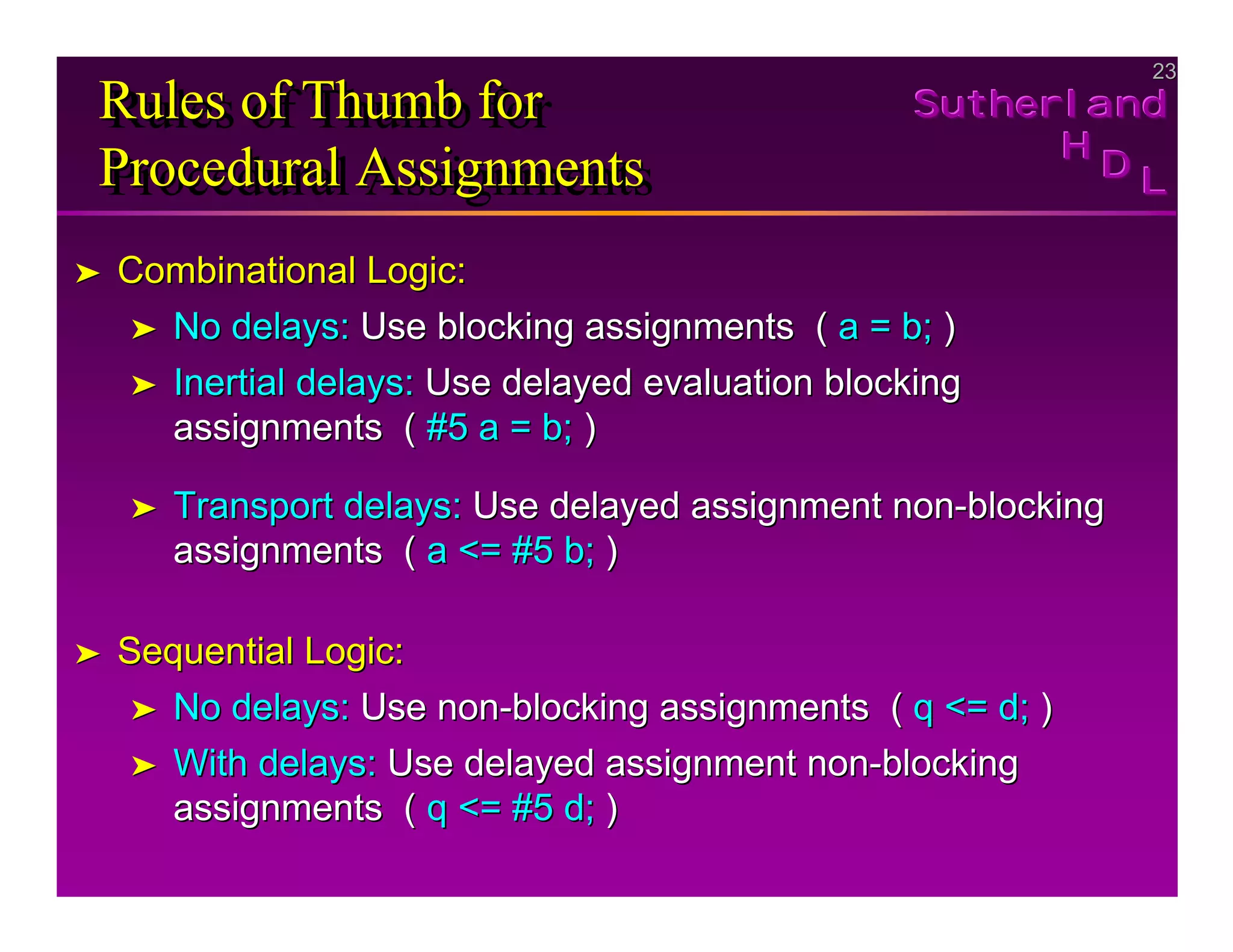

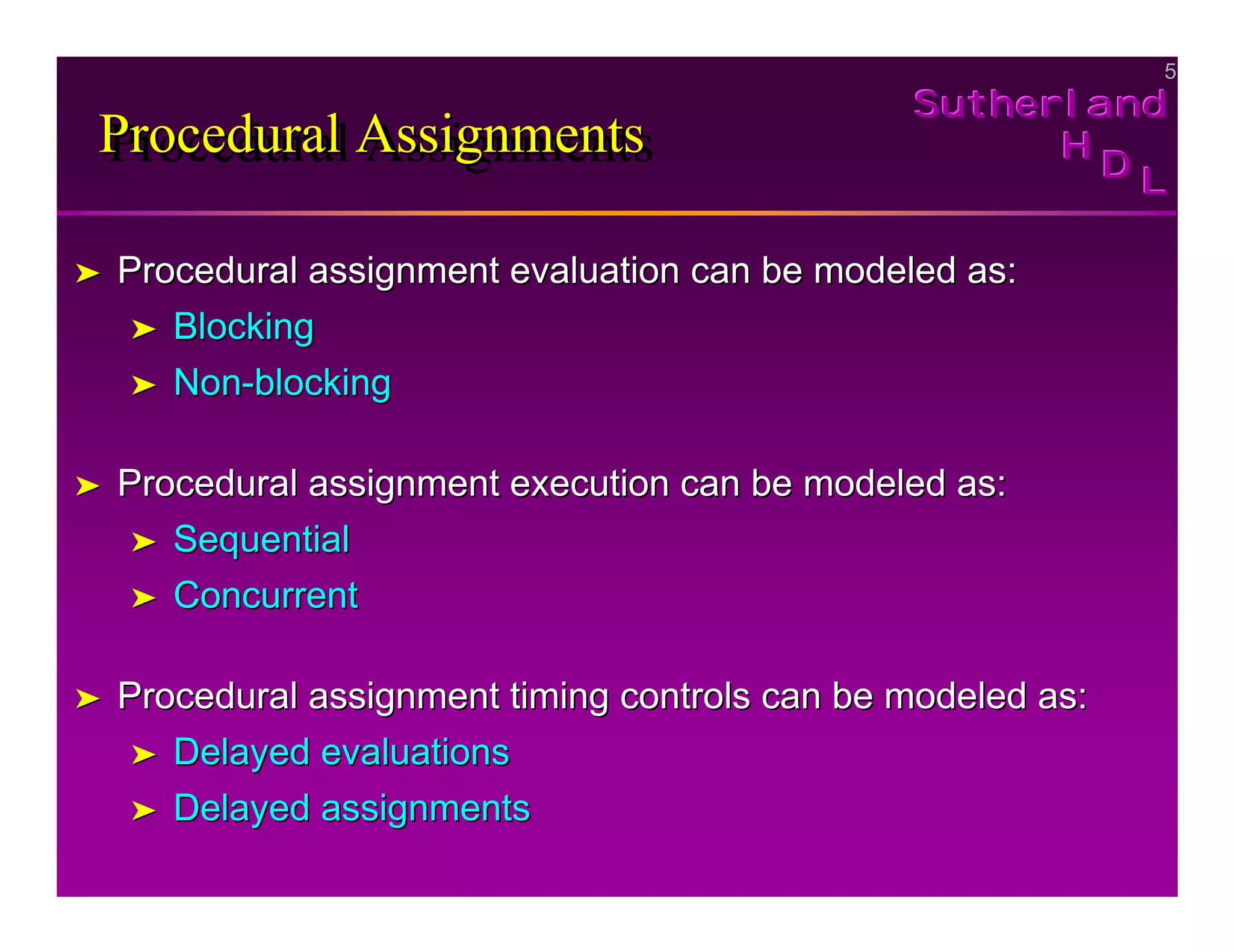

- Blocking assignments evaluate and assign in a single step, blocking further execution until complete. Non-blocking assignments evaluate immediately but assign later.

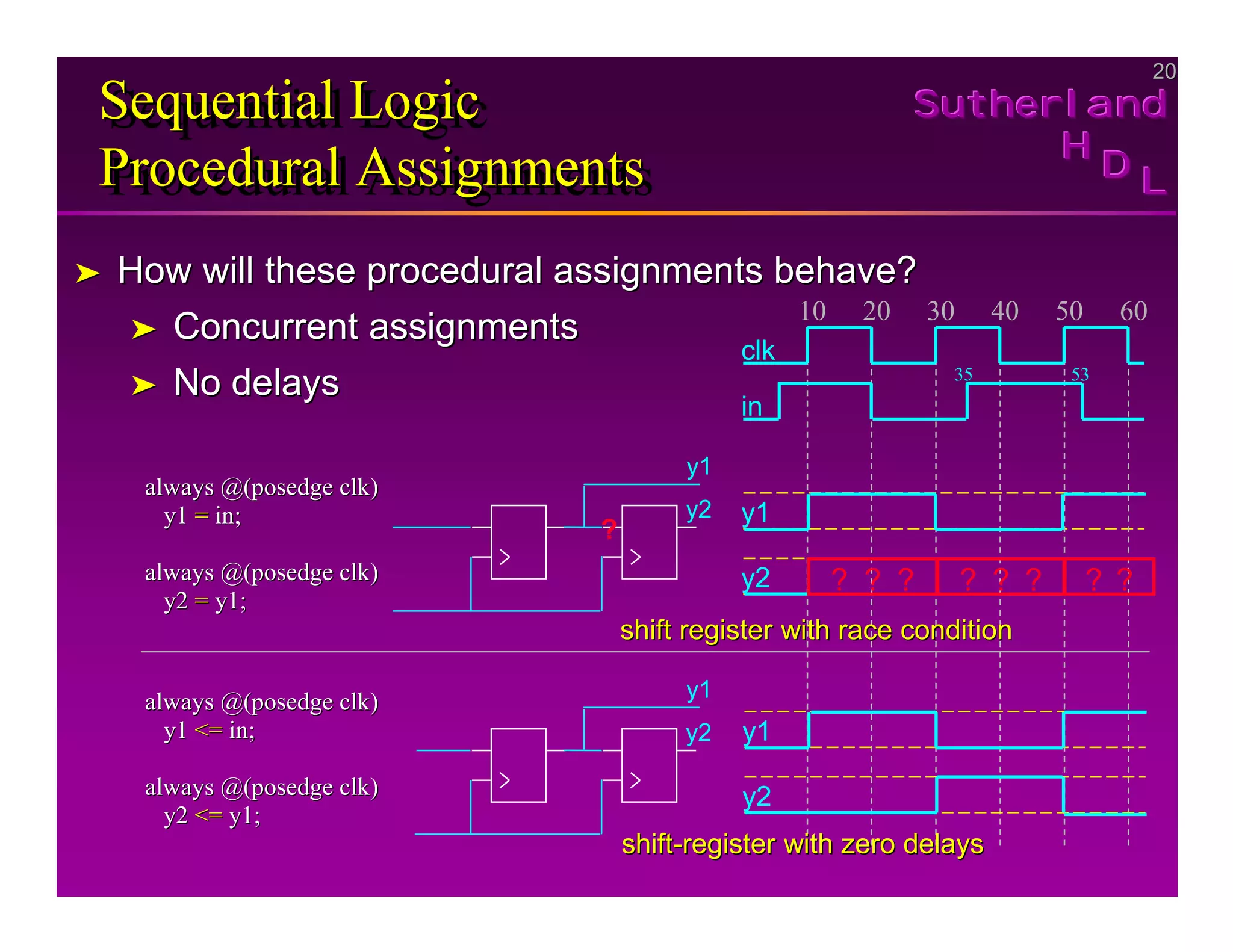

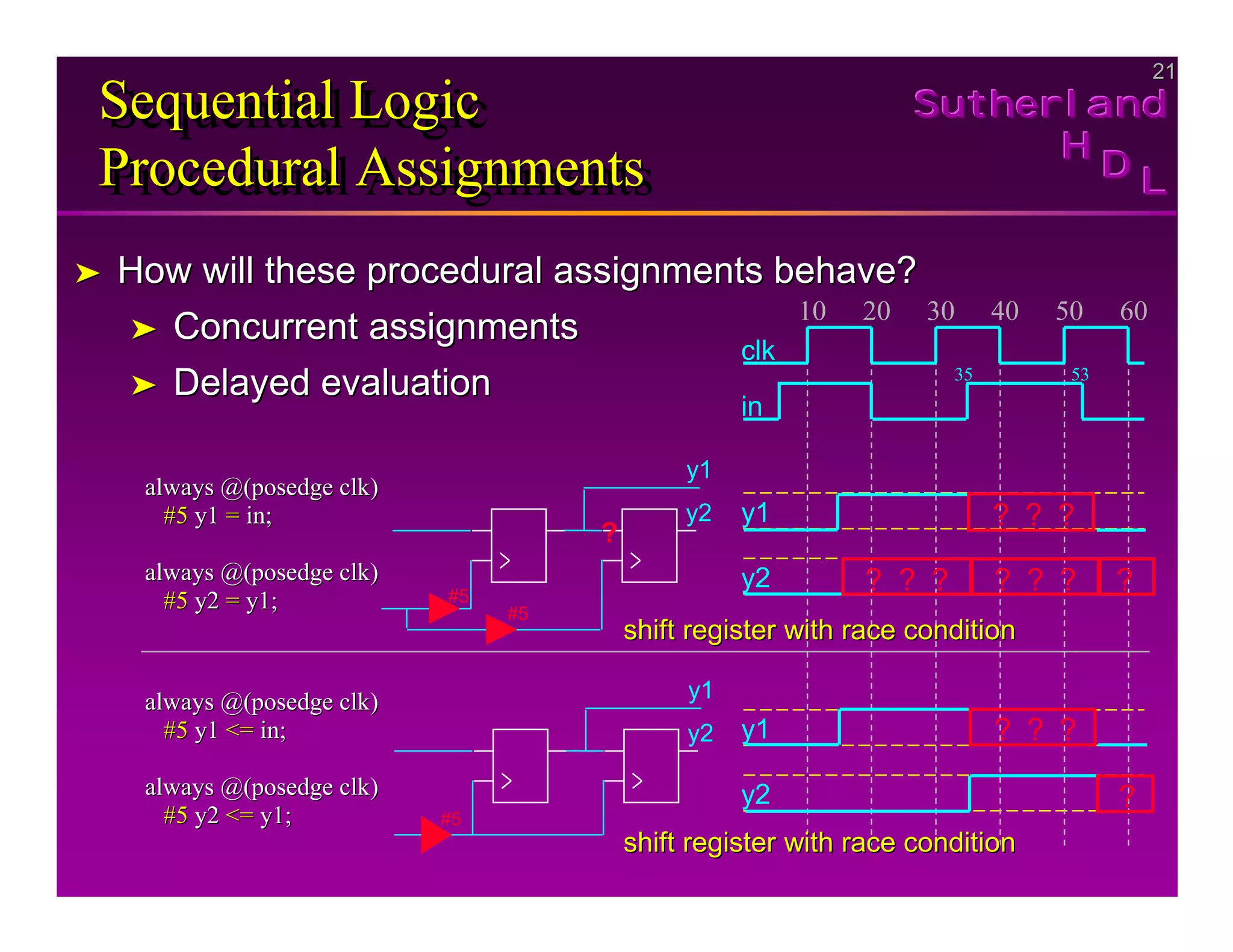

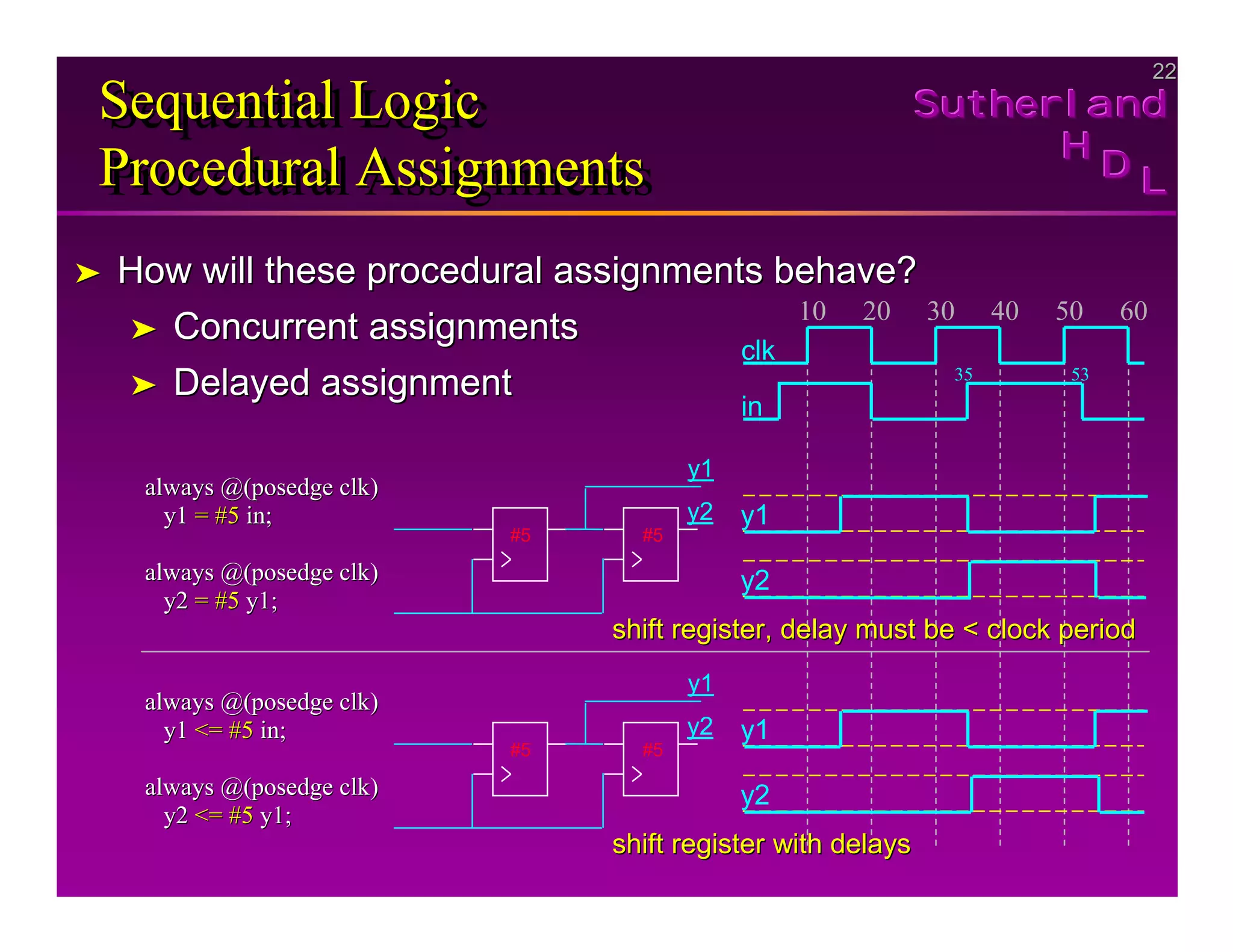

- Procedural assignments can be modeled as sequential (determinate order) or concurrent (indeterminate order).

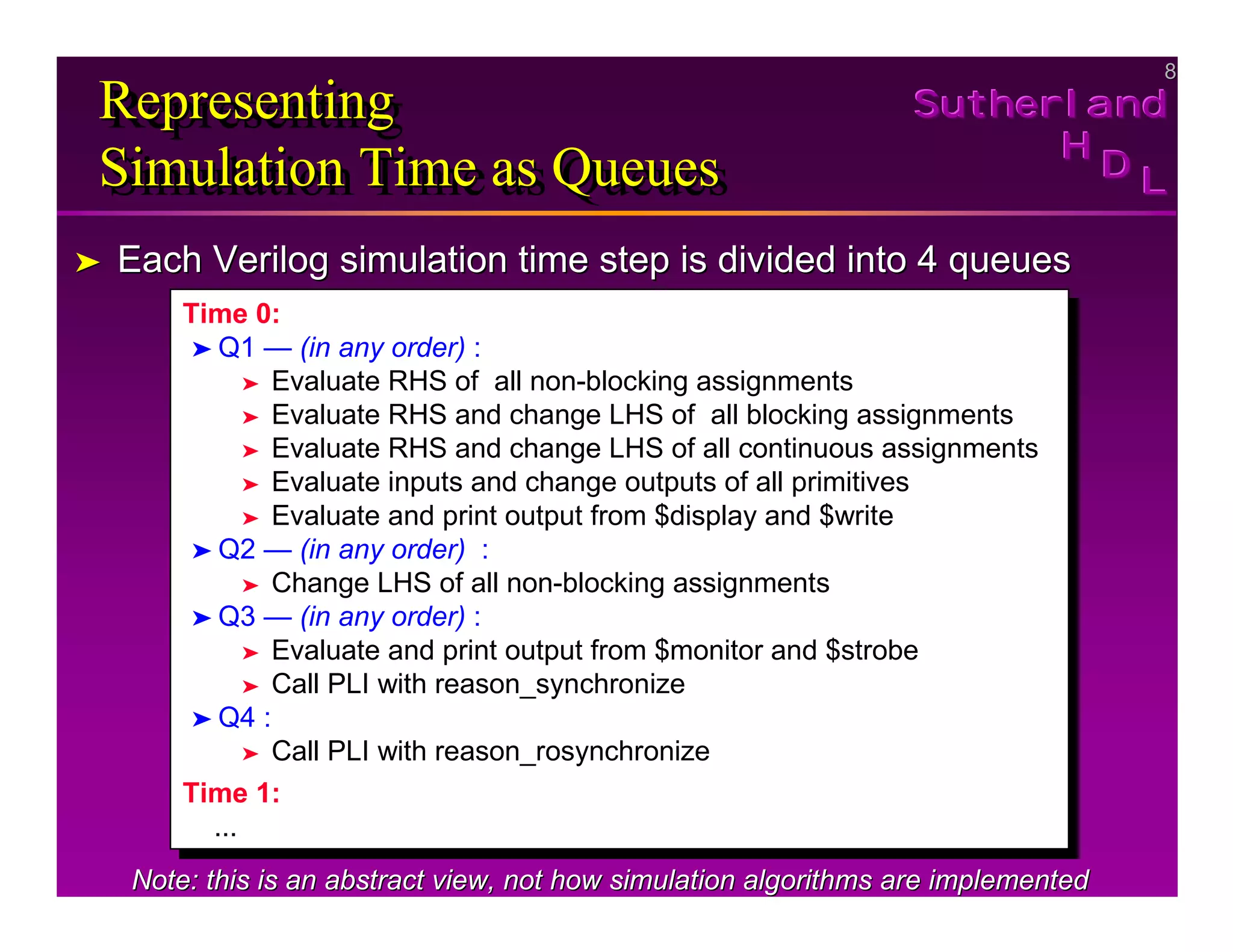

- Simulation time is divided into queues for evaluating different statement types. Blocking assigns in Q1, non-blocking assigns in Q2.

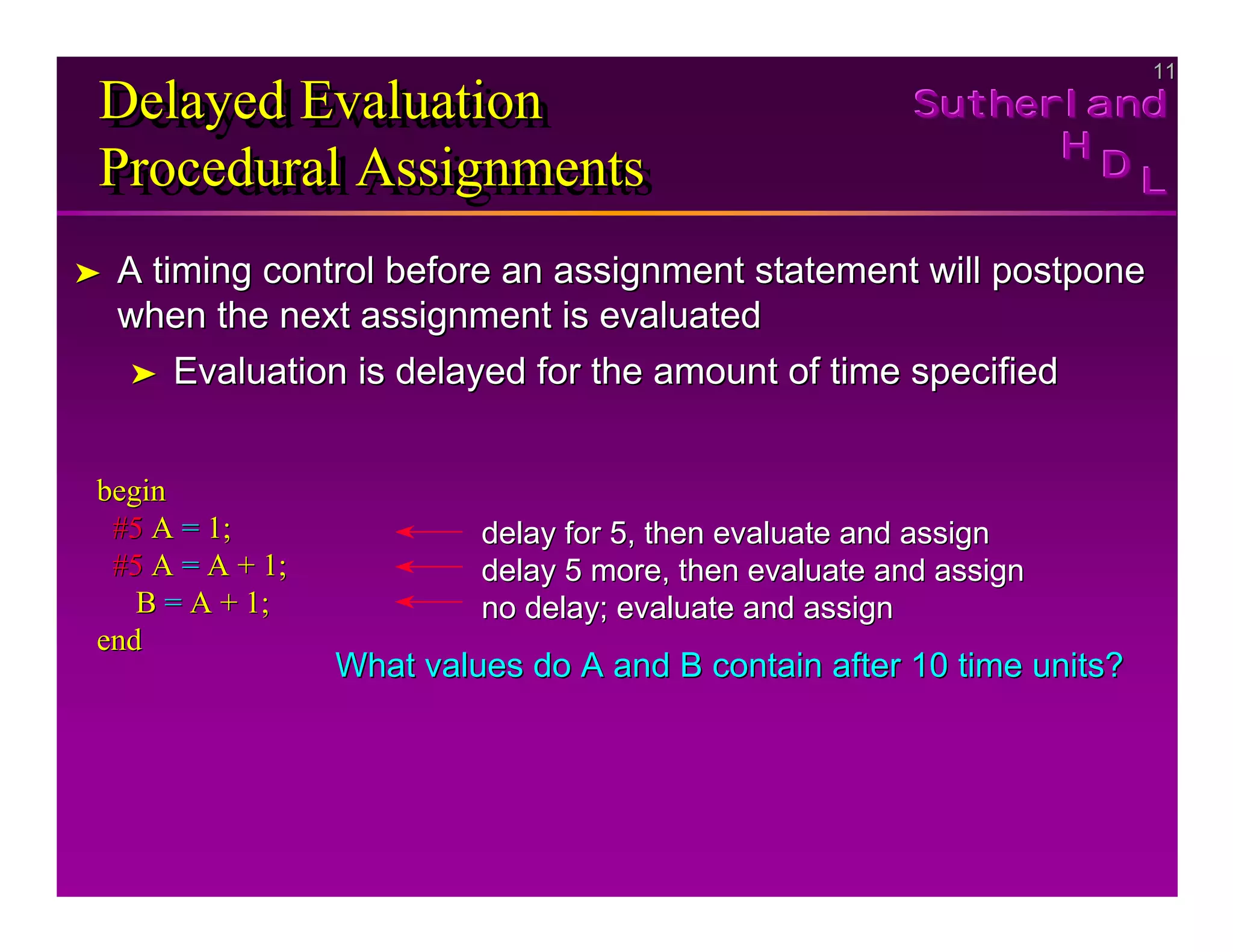

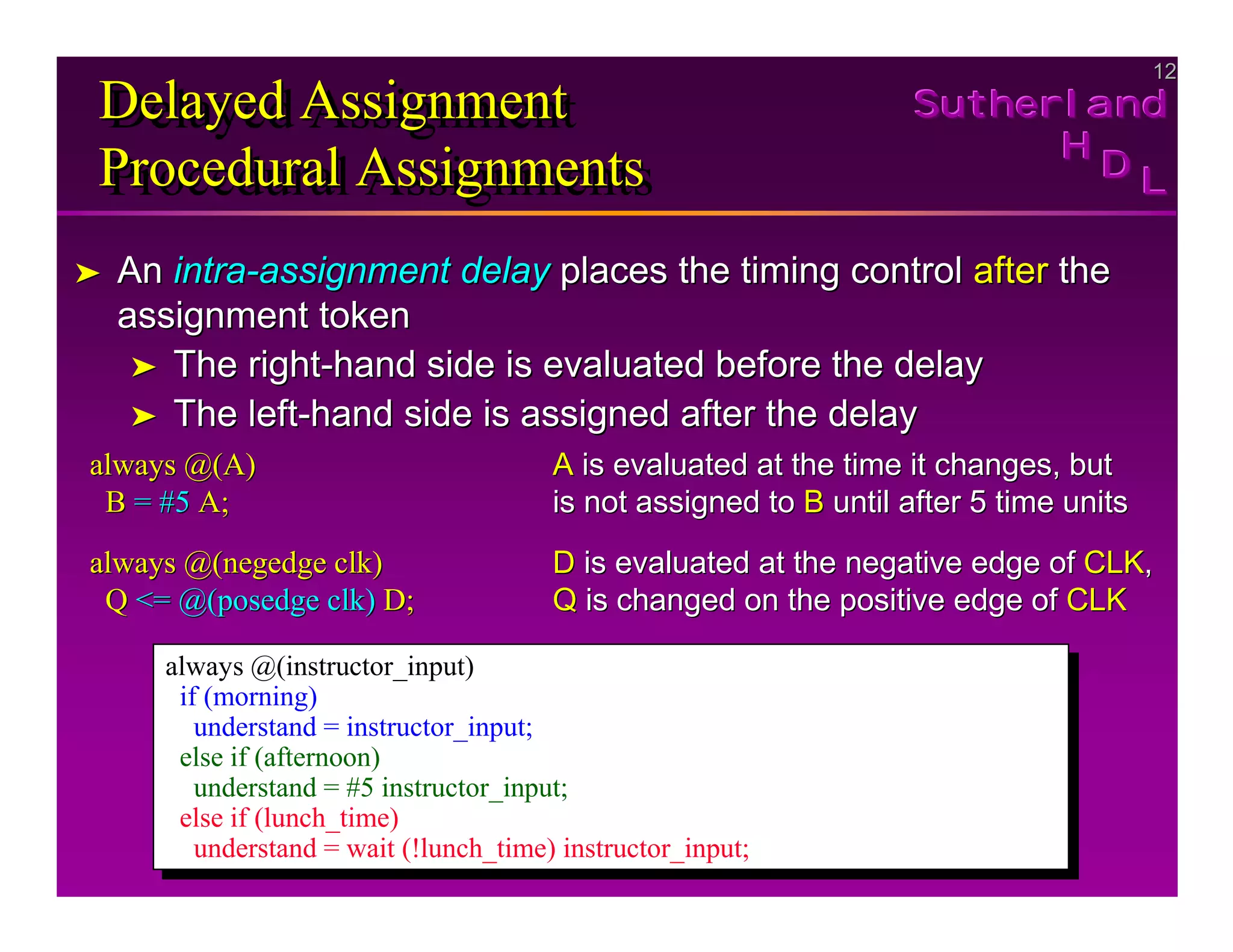

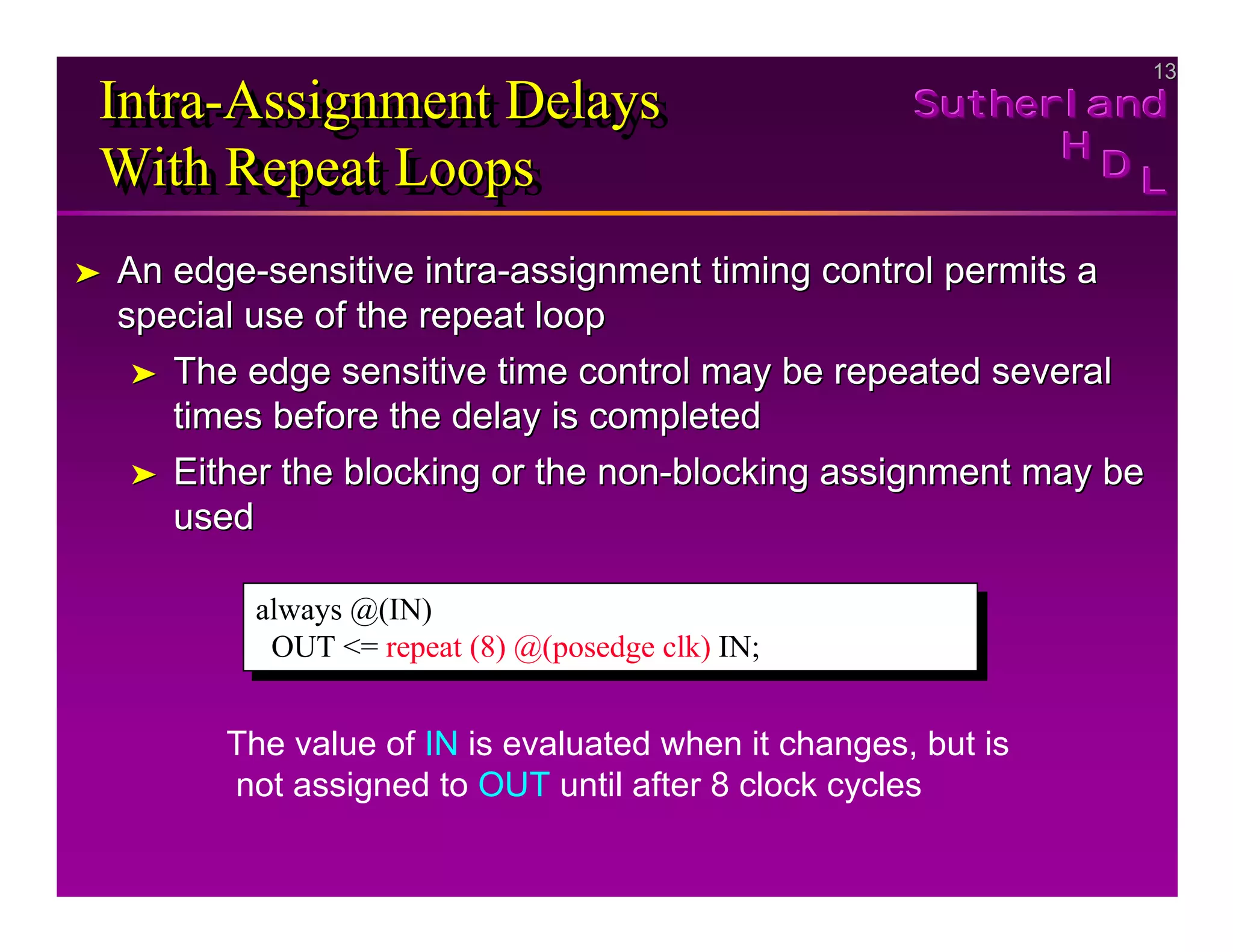

- Timing controls like # delays can postpone when an assignment is evaluated or assigned, allowing non-blocking assignments even in sequential blocks.

![6

6

Sutherland

Sutherland

Sutherland

H

H

H

D

D

D L

L

L

Blocking

Procedural Assignments

Blocking

Blocking

Procedural Assignments

Procedural Assignments

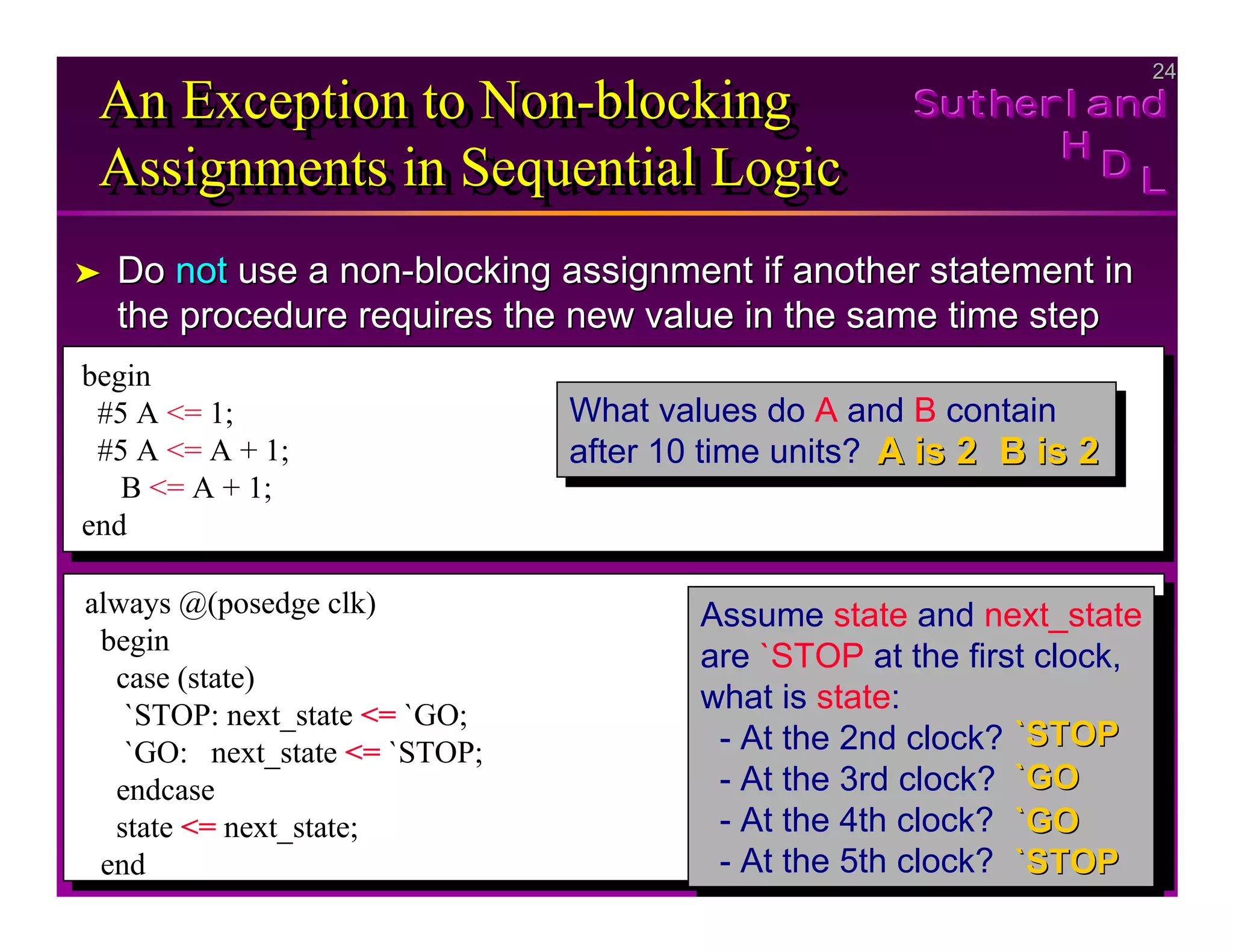

➤

➤ The

The =

= token represents a

token represents a blocking

blocking procedural assignment

procedural assignment

➤

➤ Evaluated and assigned in a single step

Evaluated and assigned in a single step

➤

➤ Execution flow within the procedure is blocked until the

Execution flow within the procedure is blocked until the

assignment is completed

assignment is completed

➤

➤ Evaluations of concurrent statements in the same time step

Evaluations of concurrent statements in the same time step

are blocked until the assignment is completed

are blocked until the assignment is completed

These examples will

These examples will not

not work

work

Why not?

Why not?

//swap bytes in word

always @(posedge clk)

begin

word[15:8] = word[ 7:0];

word[ 7:0] = word[15:8];

end

//swap bytes in word

always @(posedge clk)

begin

word[15:8] = word[ 7:0];

word[ 7:0] = word[15:8];

end

//swap bytes in word

always @(posedge clk)

fork

word[15:8] = word[ 7:0];

word[ 7:0] = word[15:8];

join

//swap bytes in word

always @(posedge clk)

fork

word[15:8] = word[ 7:0];

word[ 7:0] = word[15:8];

join](https://image.slidesharecdn.com/1996-cug-presentationnonblockingassigns-230515153138-9940421b/75/1996-CUG-presentation_nonblocking_assigns-pdf-6-2048.jpg)

![7

7

Sutherland

Sutherland

Sutherland

H

H

H

D

D

D L

L

L

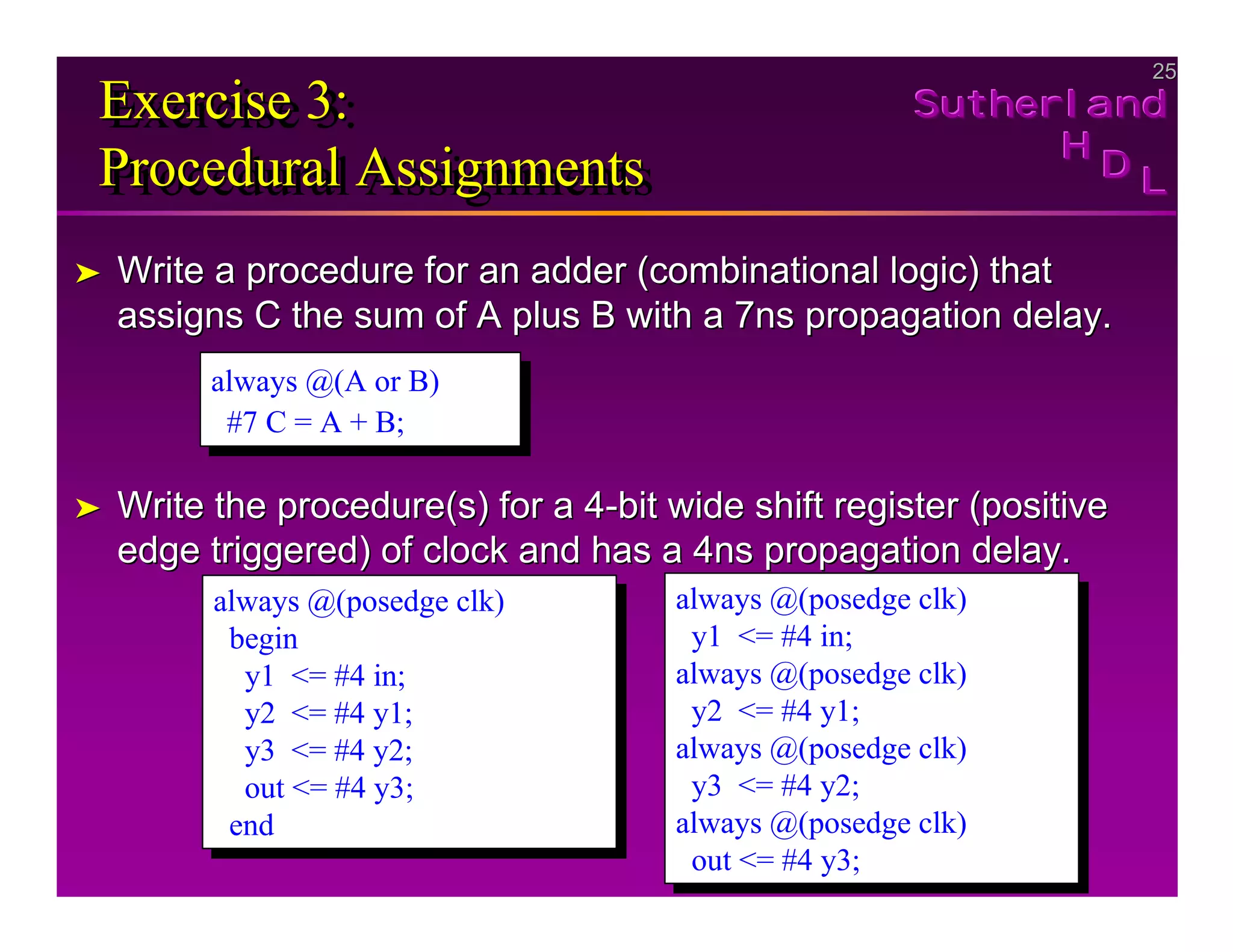

Non-Blocking

Procedural Assignments

Non

Non-

-Blocking

Blocking

Procedural Assignments

Procedural Assignments

➤

➤ The

The <=

<= token represents a

token represents a non

non-

-blocking

blocking assignment

assignment

➤

➤ Evaluated and assigned in two steps:

Evaluated and assigned in two steps:

①

① The right

The right-

-hand side is evaluated immediately

hand side is evaluated immediately

②

② The assignment to the left

The assignment to the left-

-hand side is postponed until

hand side is postponed until

other evaluations in the current time step are completed

other evaluations in the current time step are completed

➤

➤ Execution flow within the procedure continues until a

Execution flow within the procedure continues until a

timing control is encountered (flow is not blocked)

timing control is encountered (flow is not blocked)

These examples will work

These examples will work

Why?

Why?

//swap bytes in word

always @(posedge clk)

begin

word[15:8] <= word[ 7:0];

word[ 7:0] <= word[15:8];

end

//swap bytes in word

always @(posedge clk)

begin

word[15:8] <= word[ 7:0];

word[ 7:0] <= word[15:8];

end

//swap bytes in word

always @(posedge clk)

fork

word[15:8] <= word[ 7:0];

word[ 7:0] <= word[15:8];

join

//swap bytes in word

always @(posedge clk)

fork

word[15:8] <= word[ 7:0];

word[ 7:0] <= word[15:8];

join](https://image.slidesharecdn.com/1996-cug-presentationnonblockingassigns-230515153138-9940421b/75/1996-CUG-presentation_nonblocking_assigns-pdf-7-2048.jpg)