This document proposes a novel structure to improve the common mode rejection ratio (CMRR) of circuits like current buffers and folded cascode amplifiers. The proposed structure uses only four transistors and a current source to deviate common mode signals without affecting differential mode signals. This improves the CMRR by at least 12dB while preserving the CMRR bandwidth, which is a novel technique. The structure was applied to both a current buffer and folded cascode amplifier based on simulation results, demonstrating its effectiveness in improving CMRR.

![A Novel Simple And High Performance Structure For

Improving CMRR: Application to Current Buffers

and Folded Cascode Ampilifier

Amir Hossein Miremadi Hassan Faraji Baghtash

Islamic Azad University, West Tehran branch Iran University of science and technology (IUST) electrical

Tehran, Iran and electronic engineering faculty/ Electronics research

amirh_miremadi@yahoo.com center

Tehran, Iran

hfarajii@gmail.com

Abstract—A novel and simple structure for improving CMRR is process signals in differential form rather than ground-

introduced. This structure can be added to the circuits like folded reference form. Another advantage of differential operation

cascode amplifier, telescopic amplifier, current buffers, .etc to over the single-ended case is that the amplitude of the signal

improve the CMRR of these circuits. This simple and effective increases by the factor of 2[2]. An important parameter of

circuit uses common mode deviating technique to improve differential active structures is the CMRR. Differential signals

CMRR at least 12dB while preserves CMRR bandwidth which is have the advantage of canceling common-mode interference

a novel technique in order to improve CMRR. Application of this from unwanted signals and/ or noise. So CMRR is one of the

structure in both current buffer and folded cascode structures most significant parameters in many of the circuits which are

are shown. Simulation results in TSMC 0.18µm CMOS

processing differential signals; such as Op-amps, OTAs,

technology with HSPICE are presented to demonstrate the

validity of the proposed circuit. In addition Monte Carlo analysis

current buffers, etc; hence its improving is a critical issue in

is performed to simulate the fabrication condition. these circuits. Any variation of the input stage tail current

source in these circuits can significantly harm both

Keywords- High cmrr; current buffer; analog circuits; mixed deterministic and random components of the CMRR [3], [4].

mode; low voltag;, low power There have been numerous attempts to improve CMRR [5]-[7].

Most of these references used schemes to increase tail output

impedance such as using cascode current mirror. However

I. INTRODUCTION

most of these structures cause to increase minimum voltage

Today's Digital Signal Processing (DSP) is extremely on requirement. Some other structures that used techniques which

demand because of its natural benefits like reduced sensitivity didn’t need high output impedance tail need complicated

to analog noise, enhanced functionality and flexibility, implementation. On the other hand these structures need more

automated design and test, shorter design cycle, direct benefit power consumption and cause reduction in CMRR bandwidth.

from the scaling of VLSI technology, etc. But real world In this paper we proposed a simple and high effective cell

signals are analog; hence mixed-mode ICs are becoming which can be added to the circuits like folded cascode structure

progressively dominant i.e. System On Chip (SOC). In other and it cause improvement in CMRR and PSRR; whereas it

words Mixed-mode signal processing attracts increasing preserves CMRR bandwidths. This structure is composed of

attention since it simplifies design, enables compactness and only four transistors and increases power consumption slightly.

reduces cost. However signal interference from the digital to

the analog part remains a serious problem to overcome [1]; this II. PROPOSED HIGH PERFORMANCE COMMON MODE

is due to the fact that in a SOC, both analog and digital parts of

DEVIATING CELL

circuit have the same substrate. In these circuits, analog parts

must be resistant to the power supply interference coming from Fig .1 shows the conceptual schematic of the proposed

digital part. These variations which are caused by transient common mode deviating cell. The main idea is using a circuit

currents of digital circuits can cause undesired effects on power in parallel with signal path which has infinitive input resistance

supply rails or analog circuits’ inputs as common mode. Hence to the differential currents and zero to the commons. By using

both CMRR and PSRR play important roles in analog circuits. this idea we can deviates common mode currents and prevent

On the other hand, technology scaling imposes power supply to them from going to the output. On the other hand differential

be lowered. Decreasing power supply imposes some currents cannot flow in this block because of infinite resistance

restrictions on design procedure and harms common-mode to these signals ideally. Fig.2 shows transistor level

rejection ratio (CMRR) and power supply rejection ratio implementing of this idea. This structure is composed of n-type

(PSRR). Hence, for such circuits differential building blocks transistors M1, M2, p-type transistors Md1, Md2 and current

are accepted as a good solution. Therefore it is desired to source of Ib. transistors Md1, Md2, and current source of Ib

978-1-4244-8971-8/10$26.00 c 2010 IEEE](https://image.slidesharecdn.com/15-101202234827-phpapp01/85/15-1-320.jpg)

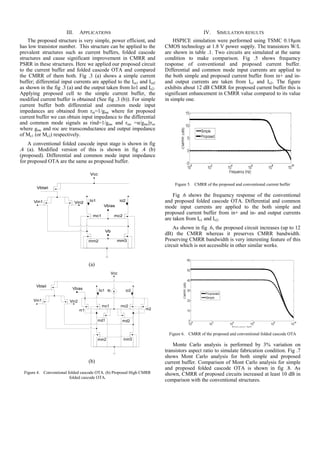

![TABLE I. TRANSISTORS ASPECT RATIO

OTA Current Buffer

ELEMENT Proposed conventional Proposed conventional

W L W L W L W L

M1 0.36 µm 0.18 µm NA NA NA NA NA NA

M2 0.36 µm 0.18 µm NA NA NA NA NA NA

Md1 27 µm 0.18 µm NA NA NA NA NA NA

Md2 27 µm 0.18 µm NA NA NA NA NA NA

Mc1 5.4 µm 0.54 µm 5.4 µm 0.54 µm 5.4 µm 0.54 µm 5.4 µm 0.54 µm

Mc2 5.4 µm 0.54 µm 5.4 µm 0.54 µm 5.4 µm 0.54 µm 5.4 µm 0.54 µm

Mm1 3.6 µm 0.54 µm 3.6 µm 0.54 µm 3.6 µm 0.54 µm 3.6 µm 0.54 µm

Mm2 3.6 µm 0.54 µm 3.6 µm 0.54 µm 3.6 µm 0.54 µm 3.6 µm 0.54 µm

MI1 3.6 µm 0.18 µm 3.6 µm 0.18 µm NA NA NA NA

MI2 3.6 µm 0.18 µm 3.6 µm 0.18 µm NA NA NA NA

Mmp1 2.7 µm 0.54 µm 2.7 µm 0.54 µm NA NA NA NA

Mmp2 2.7 µm 0.54 µm 2.7 µm 0.54 µm NA NA NA NA

and cause CMRR to improve in these circuits. This simple and

high effective circuit uses common mode deviating technique

to improve CMRR while preserves CMRR bandwidth which is

a novel technique in order to improve CMRR. Application of

this structure on both current buffer and folded cascode

structures are shown. Simulation results in TSMC 0.18µm

CMOS technology with HSPICE are presented to demonstrate

the validity of the proposed circuit. Mont Carlo analysis is

performed for simulating fabrication condition and

corroborated the appropriate performance of the proposed

circuit.

ACKNOWLEDGMENT

This work is supported by Islamic Azad University, West

Tehran branch.

Figure 7. Monte Carlo analysis of conventional and proposed current buffer. REFERENCES

- -) Simple. - ) Proposed

[1] Shahram Minaei ,I. Cem. Go¨ knar, Oguzhan Cicekoglu, "A new

differential configuration suitable for realization of high CMRR, all-

pass/notch filters," Springer-Verlag, p. 317–326, May 2005.

[2] Allen PE, Holberg DR, CMOS analog circuit design, 2, Ed. New York:

Oxford University Press, 2002.

[3] C.-G. Yu and R. L. Geiger, "Nonideality consideration for high-

precision amplifiers—Analysis of random common-mode rejection

ratio," IEEE Trans. Circuits Syst. I, Fundam. Theory Appl., vol. 40, no.

1, p. 1–12, Jan. 1993.

[4] F. You, S. H. K. Embabi, and E. Sanchez-Sinencio, "On the

commonmode rejection ratio in low voltage operational amplifiers with

complementary N-P input pairs," IEEE Trans. Circuits Syst. II, Analog

Digit.Signal Process., vol. 44, no. 8, p. 678–683, 1997.

[5] Vadim Ivanov, Junlin Zhou, and Igor M. Filanovsky, "A 100-dB CMRR

CMOS Operational Amplifier With Single-Supply Capability," IEEE

TRANSACTIONS ON CIRCUITS AND SYSTEMS—II: EXPRESS

BRIEFS, vol. 54, no. 5, pp. 397-401, May 2005.

[6] Vadim Ivanov, Junlin Zhou, Igor Filanovsky, "A 100 dB CMRR CMOS

Figure 8. Monte Carlo analyses of conventional and proposed folded OTA. - Operational Amplifier With Single-Supply Capability," IEEE., pp. 9-12,

-) Simple. - ) Proposed 2004.

[7] Jaime Rámirez-Angulo, Sandhana Balasubramanian, Antonio J. López-

Martin, and Ramón G. Carvajal, "Low Voltage Differential Input Stage

I. CONCLUSION With Improved CMRR and True Rail-to-Rail Common Mode Input

A novel and simple structure for improving CMRR was Range," IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—II:

EXPRESS BRIEFS, vol. 55, no. 12, pp. 1229-1233, Dec. 2008

introduced. As shown, this structure can be added to the

circuitries like folded cascode amplifier, current buffers, etc.;](https://image.slidesharecdn.com/15-101202234827-phpapp01/85/15-4-320.jpg)