The document discusses memory management concepts in operating systems including:

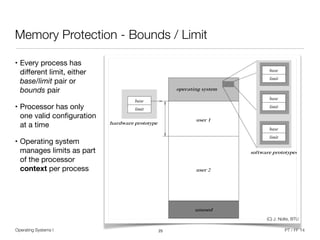

- Memory is a critical resource that must be managed by the operating system to allow multiple processes to efficiently share the physical memory.

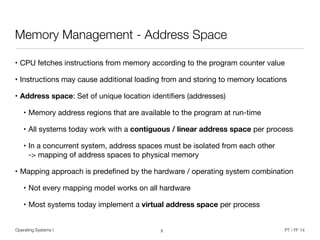

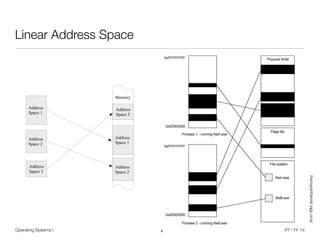

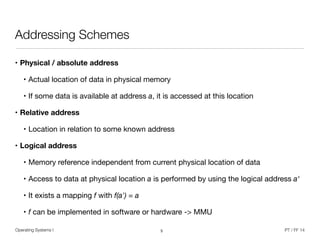

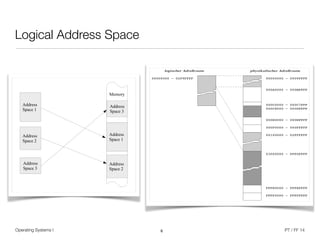

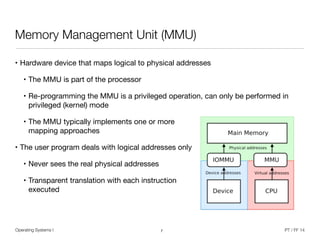

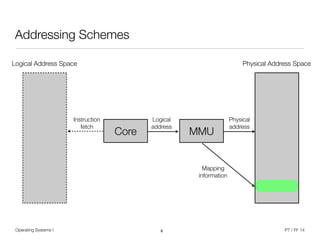

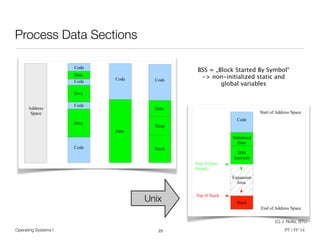

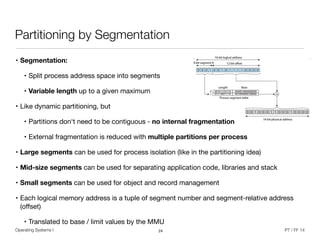

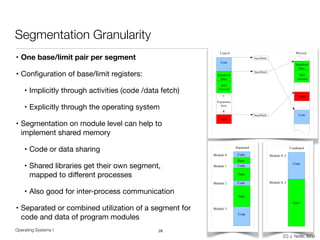

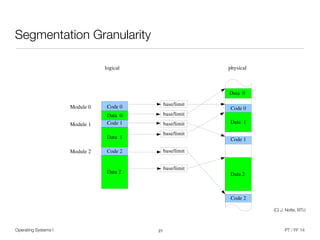

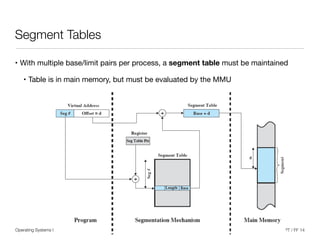

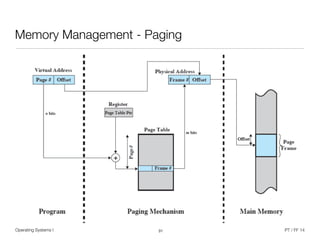

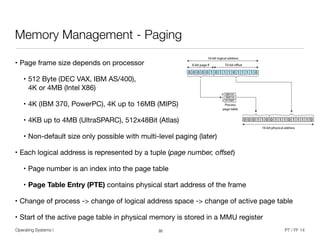

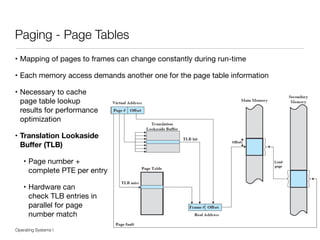

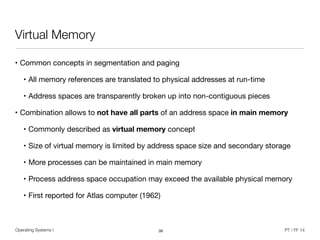

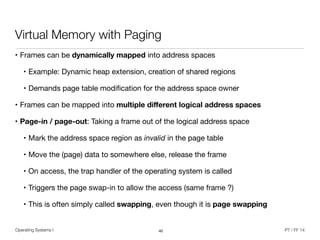

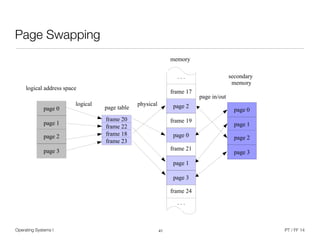

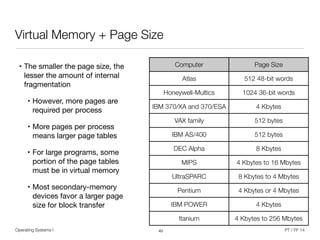

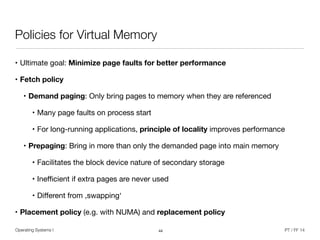

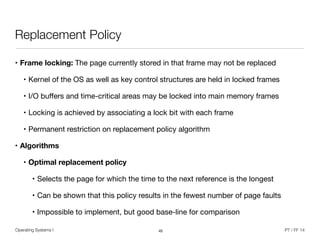

- The operating system implements virtual memory which maps process logical addresses to physical addresses to isolate processes.

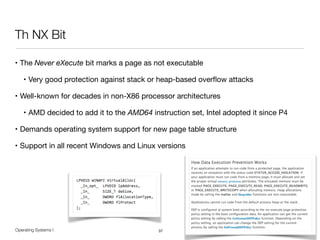

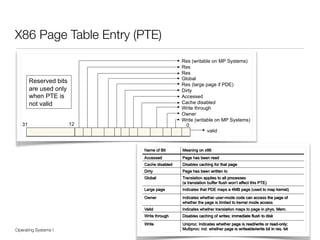

- A memory management unit (MMU) hardware performs this address translation transparently.

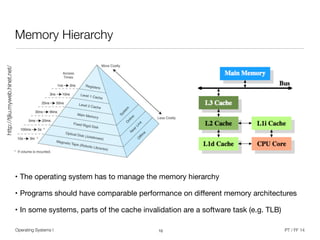

- Memory is organized in a hierarchy from fast expensive cache/RAM to slower cheaper disk storage.

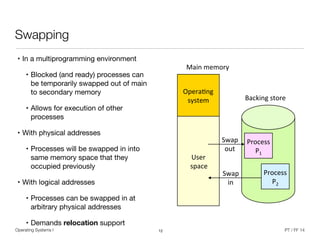

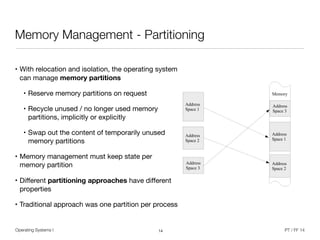

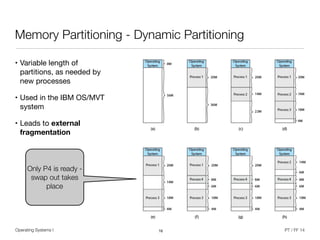

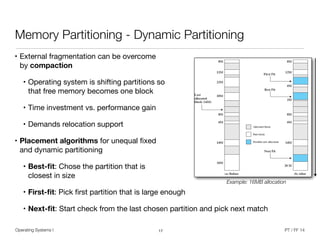

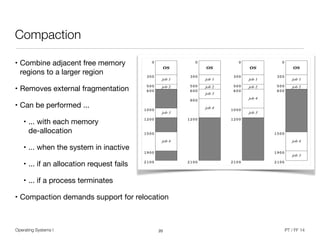

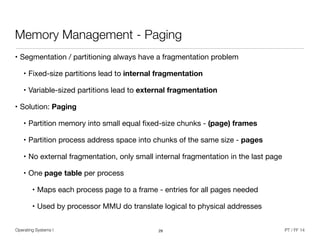

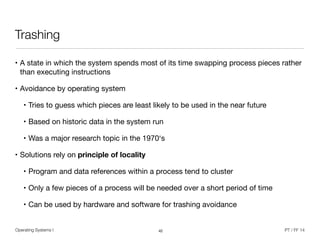

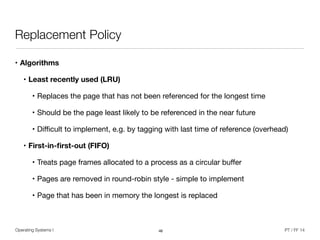

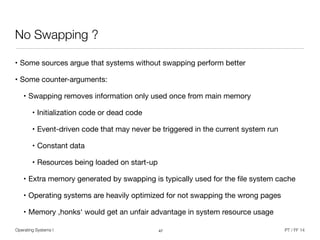

- The operating system uses paging, swapping and memory partitioning to manage this hierarchy and allocate memory to processes.