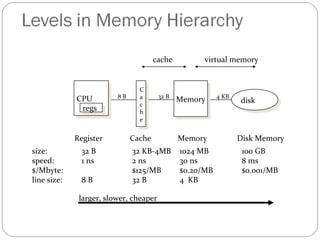

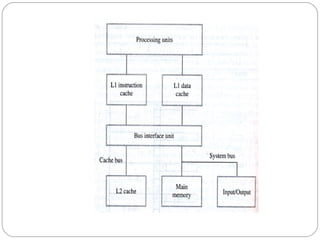

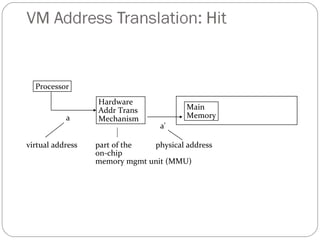

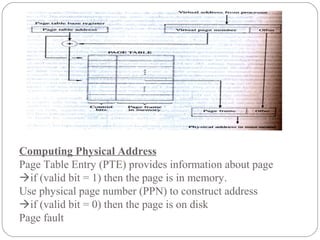

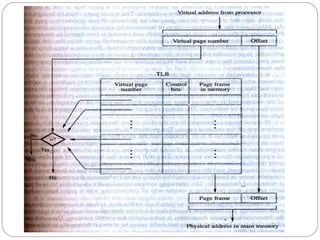

Virtual memory allows a program to access more memory than is physically installed on the system by storing seldom-used data on disk. The CPU uses virtual addresses while physical addresses identify the actual memory location. The memory management unit (MMU) translates virtual to physical addresses using page tables stored in memory. If a page is not in memory, a page fault occurs and the OS loads the required page from disk before resuming execution. Virtual memory provides the illusion of a larger memory to programs through demand paged paging and address translation mechanisms.