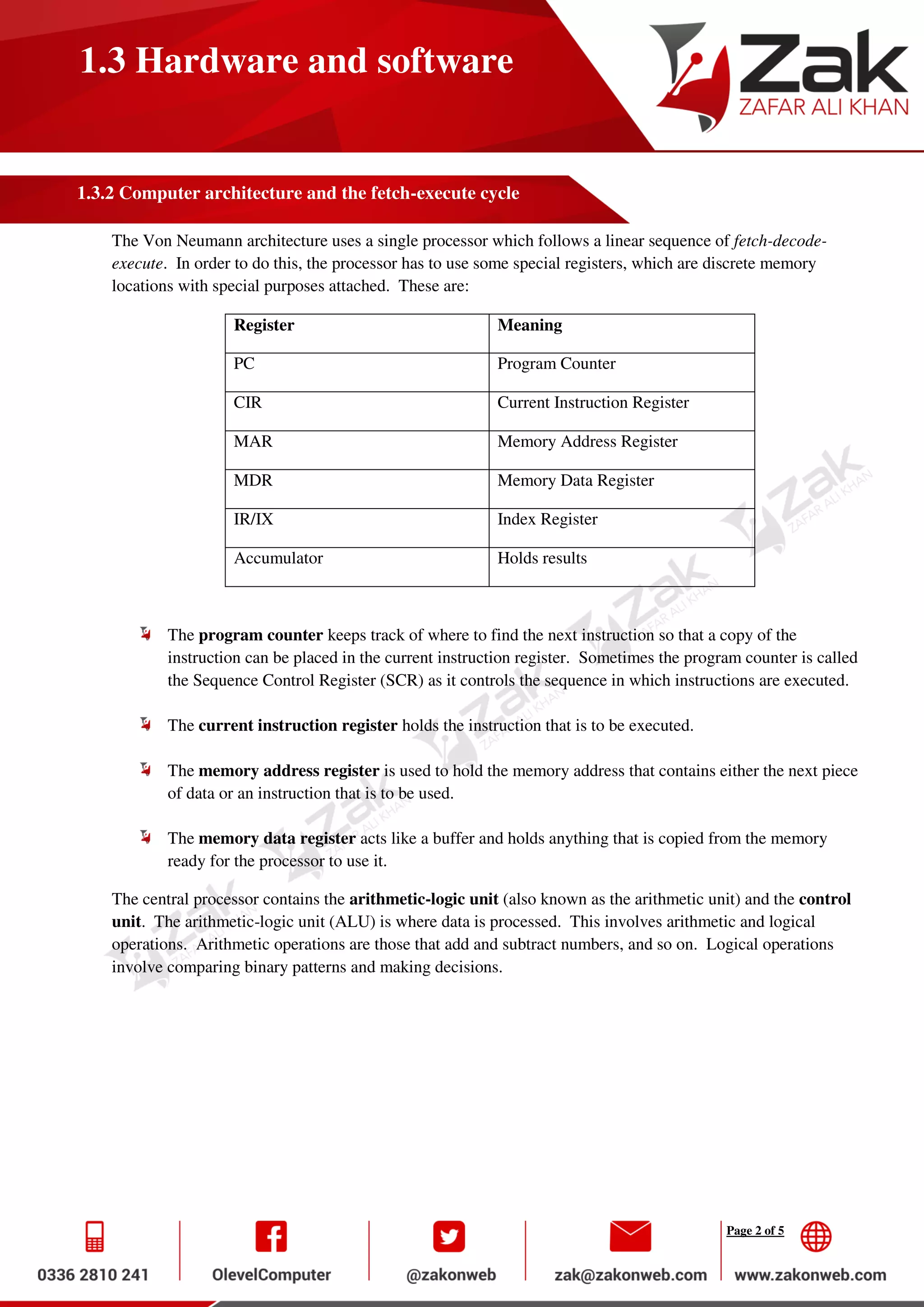

The document describes the Von Neumann architecture and the fetch-execute cycle of a CPU. It explains that Von Neumann introduced the concept of storing both instructions and data in memory. This allowed programs to be changed by modifying memory rather than rewiring the computer. It then outlines the registers involved in the fetch-execute cycle, including the program counter, instruction register, and accumulator. The cycle fetches an instruction from memory, decodes it, executes it, and then resets to fetch the next instruction, repeating continuously. The cycle provides the fundamental operation of a CPU.