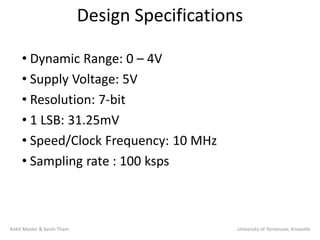

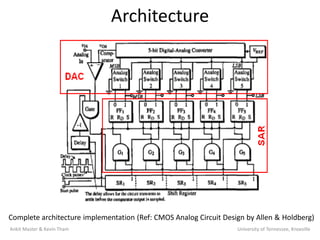

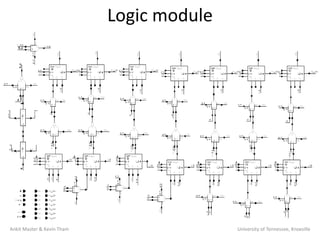

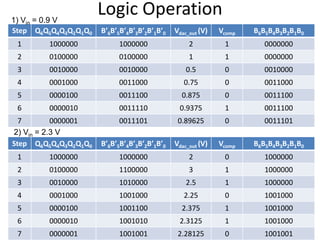

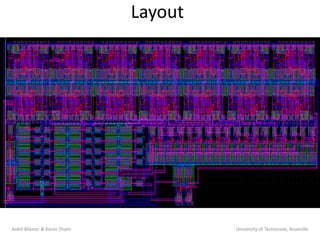

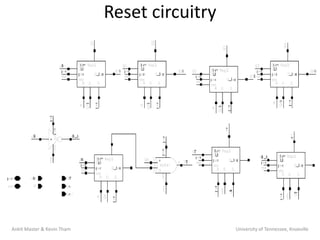

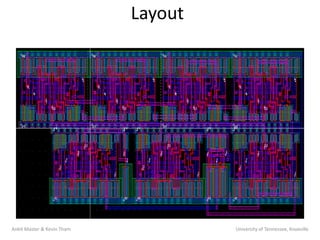

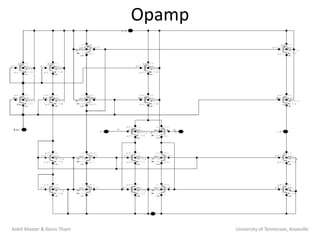

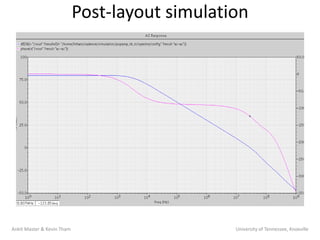

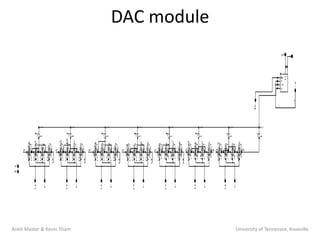

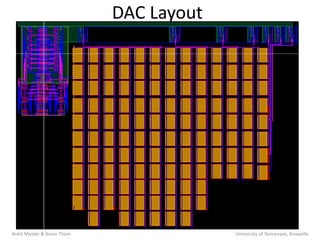

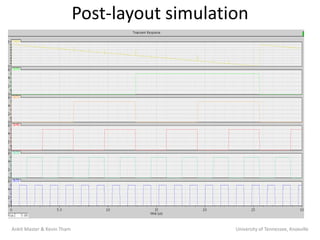

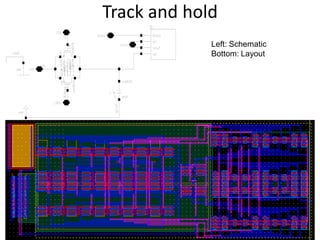

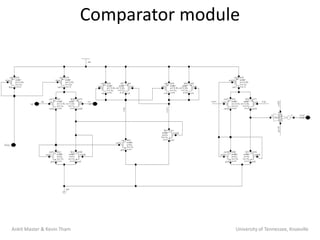

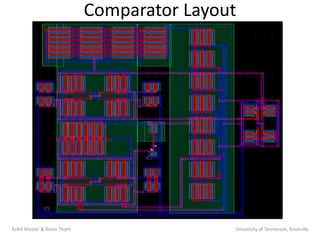

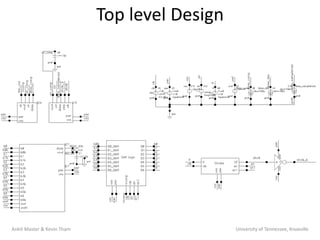

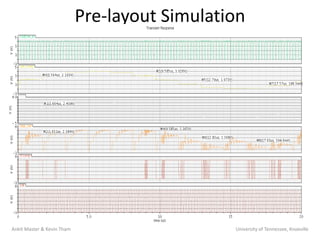

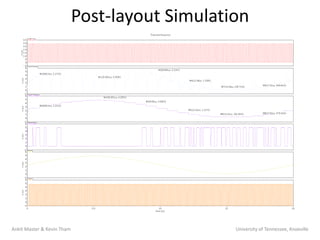

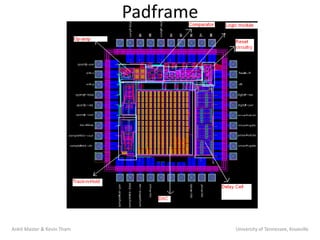

The document outlines the final project for a successive approximation ADC designed by Ankit Master and Kevin Tham at the University of Tennessee, Knoxville. Key specifications include a dynamic range of 0-4V, a 5V supply voltage, and a resolution of 7 bits with a sampling rate of 100 ksps. The report encompasses architecture design, logic operations, and simulations throughout the pre-layout and post-layout phases.