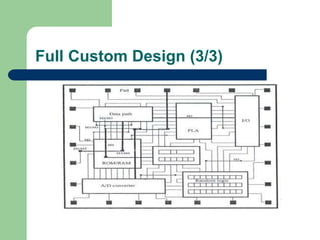

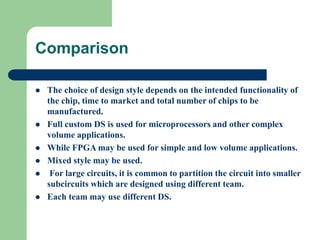

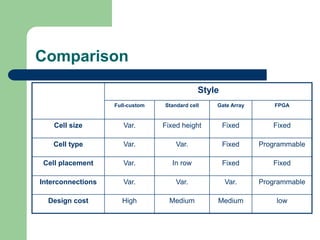

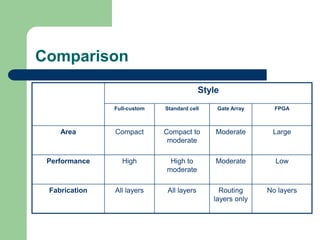

VLSI design involves integrating millions of transistors onto a single chip. There are various design styles including full custom, standard cell, gate array, and FPGA. Full custom designs have fully customized cells and layouts but require more design time. Standard cell and gate array styles use predesigned cells, reducing design time but only customizing interconnect layers. FPGA designs have no custom masks and the fastest design turnaround time.