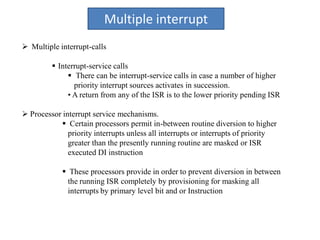

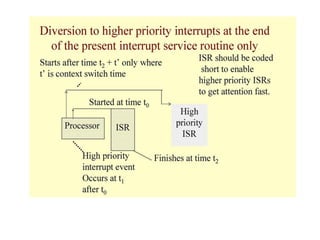

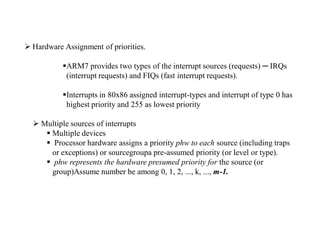

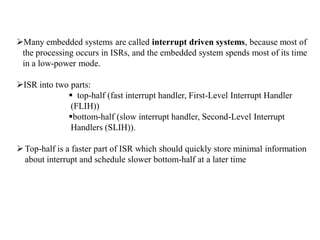

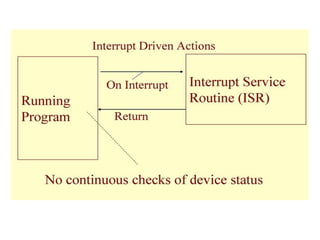

This document discusses interrupt handling in embedded systems. It defines an interrupt as a signal generated by an external event that causes the CPU to stop current execution and jump to an interrupt service routine (ISR). Hardware interrupts are triggered by peripheral devices, while software interrupts are called from software. The ISR handles the interrupt request and returns execution to the previous location. Interrupts are important for interacting with devices and responding to events immediately. Common hardware interrupt sources include pin changes, timers, and peripheral communication. Embedded systems are often interrupt-driven with processing occurring in ISRs while the system remains in low-power mode. Multiple interrupts are prioritized and handled through interrupt stacking or masking on certain processor architectures.

![Interrupt Sources

Hardware Interrupts

▫Commonly used to interact with external devices or peripherals

▫Microcontroller may have peripherals on chip

Software Interrupts

▫Triggered by software commands, usually for special operating system tasks]

• i.e. switching between user and kernel space, handling exceptions

Common hardware interrupt sources

▫Input pin change

▫Hardware timer overflow or compare-match

▫Peripherals for serial communication

UART, SPI, I2C – Rx data ready, tx ready, tx complete.

Watchdog timer timeout.

ADC conversion complete.](https://image.slidesharecdn.com/devicedriversandinterruptservicemechanism-170516185203/85/Device-drivers-and-interrupt-service-mechanism-9-320.jpg)