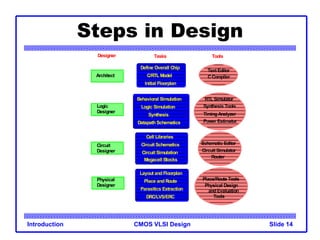

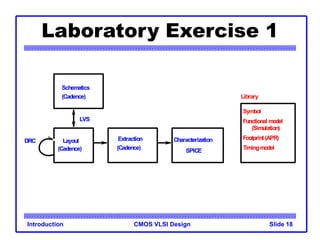

This document provides an introduction to a course on CMOS VLSI design. It outlines the prerequisites, organization of the course, and relevance of VLSI design. It discusses the difference between architecture design and chip design. It provides an overview of the topics that will be covered in a bottom-up approach and using CAD tools. It also outlines the course goals, work involved including homework, projects and labs, exams and grading policy.