The ALMA project aims to simplify programming for multi-core processors by providing tools that convert Scilab code into optimized C code, leveraging parallelization to enhance performance. The project, funded by the EU with a budget of 3.2 million euros, focuses on reducing development times by 30-60% and making parallel computing accessible to users without deep technical knowledge. Key outcomes include a free Scilab to C code converter and plans for future product launches to support various hardware platforms.

![FP7-ICT-2011-7-287733 – ScilabTEC – Oliver Oey – oliver.oey@kit.edu 18

Type Inference - Shape

Calculate shape of each Scilab statement

s = [1 2 3]; // s = 1x3

for f = 1:10 // f = 1x1

s = s + f // s = 1x3

end

Scilab

Type Inference

Loopify

Simplify

C Code Output

C Code](https://image.slidesharecdn.com/10-150618120534-lva1-app6892/75/ScilabTEC-2015-KIT-18-2048.jpg)

![FP7-ICT-2011-7-287733 – ScilabTEC – Oliver Oey – oliver.oey@kit.edu 19

Type Inference – Growing Arrays

Support growing arrays

a = 1;

a(1,5) = 1;

[1 0 0 0 1]

Maximum size must be known!

What happens if matrix is indexed by variable?

a(1,b) = 1; // Maximum value of b unknown

Two solutions:

Scilab

Type Inference

Loopify

Simplify

C Code Output

C Code

a = zeros(1,5);

mfe_fixedsize(a);

a = 1;

a(1,b) = 1;

a = 1;

mfe_size(a, 1, 1:5);

a(1,b) = 1;](https://image.slidesharecdn.com/10-150618120534-lva1-app6892/75/ScilabTEC-2015-KIT-19-2048.jpg)

![FP7-ICT-2011-7-287733 – ScilabTEC – Oliver Oey – oliver.oey@kit.edu 20

Type Inference – Data Type

Scilab has data type function

double

int32, int16, int8

uint32, uint16, uint8

boolean

complex, real, imag

a = uint8([255 256]);

[255 0]

Scilab

Type Inference

Loopify

Simplify

C Code Output

C Code](https://image.slidesharecdn.com/10-150618120534-lva1-app6892/75/ScilabTEC-2015-KIT-20-2048.jpg)

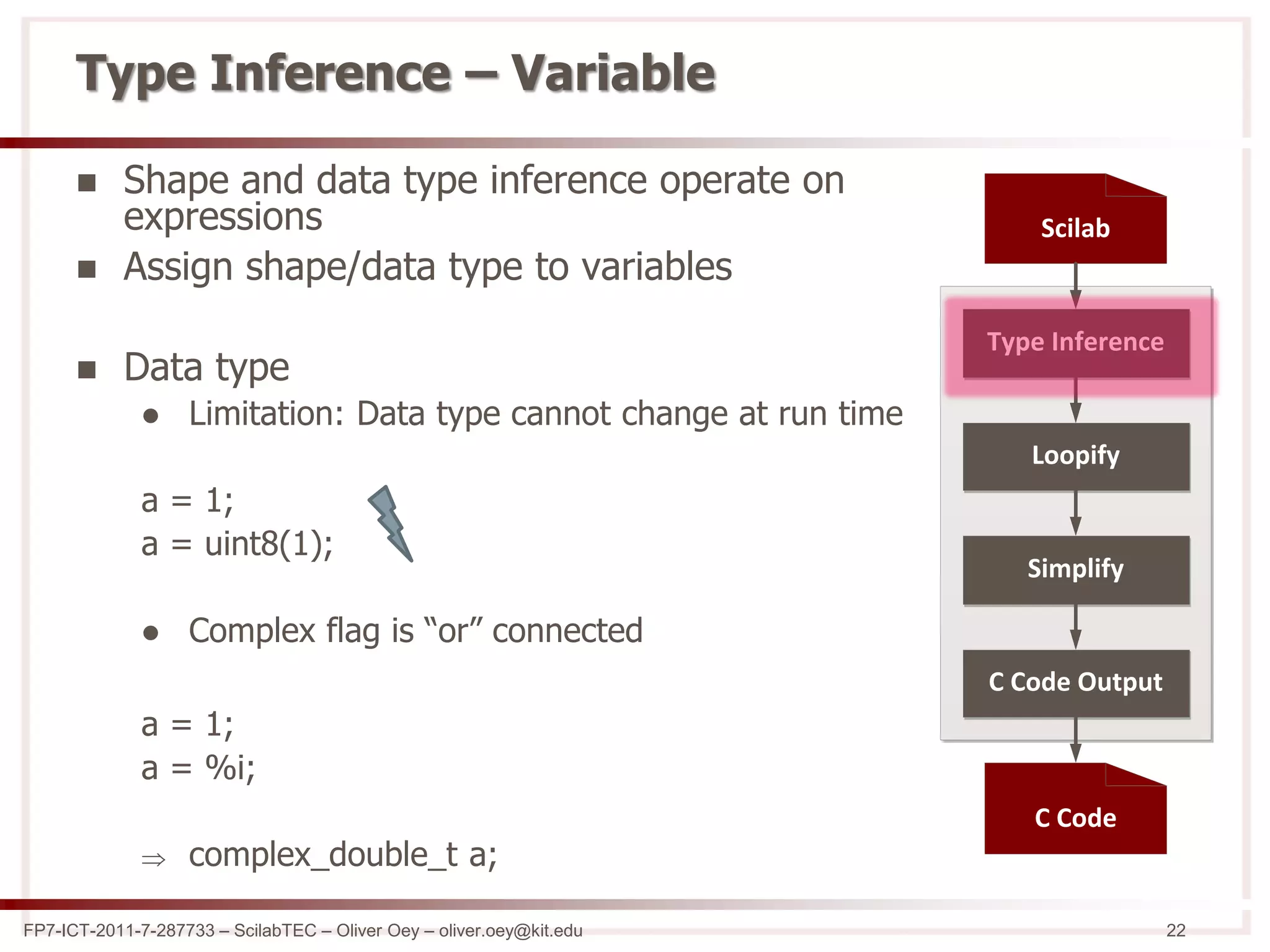

![FP7-ICT-2011-7-287733 – ScilabTEC – Oliver Oey – oliver.oey@kit.edu 23

Type Inference – Variable (2)

Shape

Variable shape is maximum of all dimensions

a = zeros(1,3);

a = zeros(4,1);

double a[4,3];

Limitation: Number of dimensions cannot

change

a = zeros(3,3);

a = zeros(3,3,3);

Scilab

Type Inference

Loopify

Simplify

C Code Output

C Code](https://image.slidesharecdn.com/10-150618120534-lva1-app6892/75/ScilabTEC-2015-KIT-23-2048.jpg)

![FP7-ICT-2011-7-287733 – ScilabTEC – Oliver Oey – oliver.oey@kit.edu 24

Loopify

Translates Matlab/Scilab variables into

Data

Dynamic size

Static (maximum) size

Translates Matlab/Scilab statements into

Loop nest

Size calculation

Scilab C code

a = zeros(2,3); int32_t a_data[3][2] = {{0}};

int32_t a_size[2];

const int32_t a_ssize[2] = {2, 3};

for (v1 = 0; v1 < 3; ++v1) {

for (v0 = 0; v0 < 2; ++v0) {

a_data[v1][v0] = 0;

}

}

a_size[0] = 2;

a_size[1] = 3;

Scilab

Type Inference

Loopify

Simplify

C Code Output

C Code](https://image.slidesharecdn.com/10-150618120534-lva1-app6892/75/ScilabTEC-2015-KIT-24-2048.jpg)

![FP7-ICT-2011-7-287733 – ScilabTEC – Oliver Oey – oliver.oey@kit.edu 25

Simplify

Remove unnecessary “for loops”

Remove unnecessary variable dimensions

Remove size variables and statements for fixed

size variables

Scilab C code

a = 1;

(before simplify)

int32_t a_data[1][1] = {{0}};

…

for (v1 = 0; v1 < 1; ++v1) {

for (v0 = 0; v0 < 1; ++v0) {

a_data[v1][v0] = 1;

}

}

a = 1;

(after simplify)

int32_t a_data = 0;

…

a_data[v1][v0] = 1;

Scilab

Type Inference

Loopify

Simplify

C Code Output

C Code](https://image.slidesharecdn.com/10-150618120534-lva1-app6892/75/ScilabTEC-2015-KIT-25-2048.jpg)