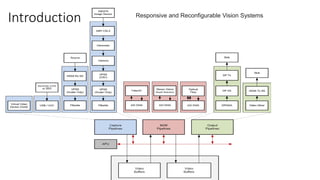

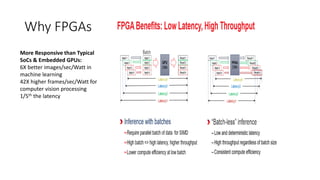

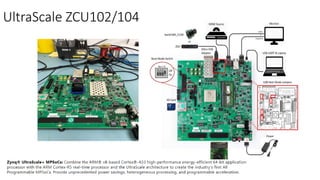

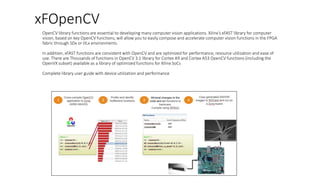

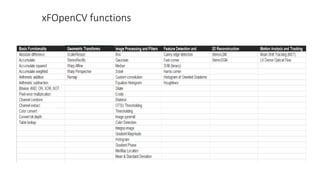

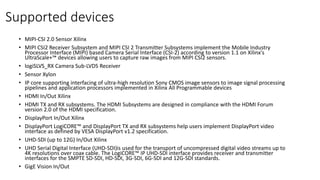

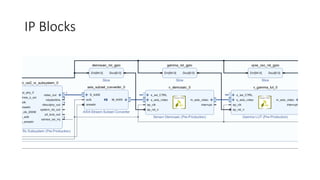

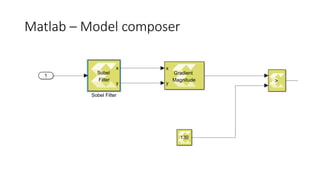

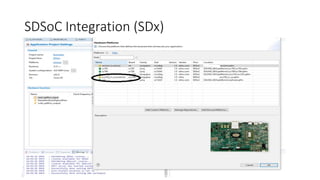

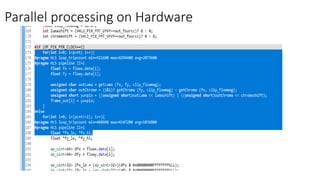

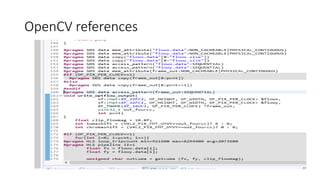

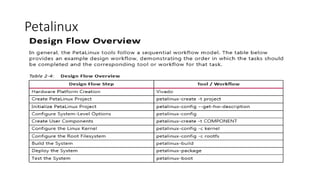

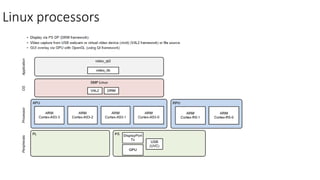

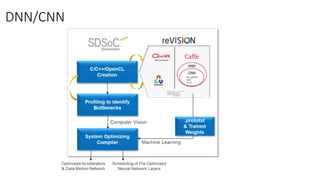

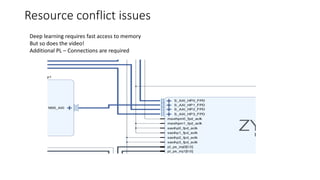

The document discusses the Re-Vision stack which provides implementations for computer vision applications using FPGAs. It includes designs for dense optical flow, stereo vision, and combining multiple algorithms. The stack utilizes OpenCV libraries optimized for FPGAs and supports various camera interfaces. It leverages SDSoC to integrate C/C++ code with FPGA logic and allows parallel processing. Deep learning is mentioned as a future integration to combine computer vision tasks with neural networks. Resource conflicts between video and neural network memory needs require additional programmable logic and connections.