1) The document discusses using RISCV-DV, an open source framework, to enhance verification coverage for the RISC-V Vector extension.

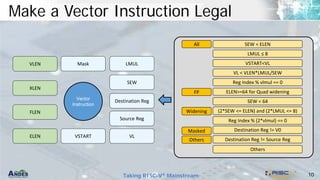

2) It describes how RISCV-DV implements the Vector extension through instruction support, programmer's model support, and constrained random generation of vector programs.

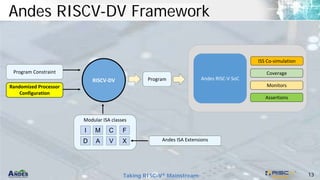

3) A case study shows how Andes customized RISCV-DV to verify their NX27V processor implementation of the Vector extension through co-simulation and directed instruction streams.